Xilinx FPGA入门连载30:超声波测距回响脉宽计数之数码管显示

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1jGjAhEm

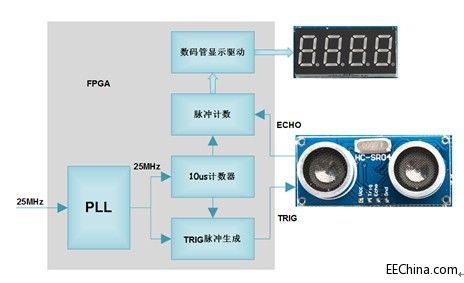

如图所示,本实例同样是以10us计数器产生的10us脉冲TRIG给超声波测距模块,然后以10us为单位计算超声波测距模块返回的回响信号ECHO的高电平保持时间。采集到的ECHO高电平脉冲保持周期(以10us为单位)将以16进制方式显示到数码管上。

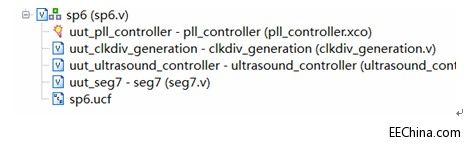

如图所示,本实例一共6个模块,顶层模块sp6.v主要对各个子模块进行例化和连接;pll_controller.v模块是IP核,例化PLL,产生FPGA内部需要的时钟信号;clkdiv_generation.v模块产生10us的基准时钟使能信号;ultrasound_controller.v模块对超声波测距模块的回响信号进行高脉冲时间计数;seg7.v模块驱动数码管显示。

连接好下载线,给SP6开发板供电。

打开ISE,进入iMPACT下载界面,将本实例工程下的sp6.bit文件烧录到FPGA中在线运行。

此时我们在超声波测距模块前面摆放平整的障碍物,可以看到数码管上的16进制数据会发生变化。基本规律是:障碍物距离超声波测距模块近,则数码管的数值较小;障碍物距离超声波测距模块远,则数码管的数值较大。

大家可以通过如下的公式计算当前数码管显示数据和实际超声波测距模块与障碍物距离是否一致。当然了,大家也不用着急,接下来几节我们就着手进行换算,将16进制先转换为10进制,然后把下述的公式结果计算出来并显示在数码管上。

假设超声波模块与障碍物间的距离为S(单位:m),ECHO输出的高脉冲宽度为T(单位:s),声速在25°C条件下定义为346(单位:m/s)。那么ECHO脉冲宽度与测试距离的关系如下。

S = (T*346)/2

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 迄今为止最牛的ASIC验证平台(05-22)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)