Xilinx FPGA入门连载38:SRAM读写测试之设计概述

时间:12-18

来源:互联网

点击:

Xilinx FPGA入门连载40:SRAM读写测试之设计概述

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1jGjAhEm

如图所示,本实例每秒钟定时进行一个SRAM地址的读和写操作。读写数据比对后,通过D2 LED状态进行指示。与此同时,也可以通过chipscope pro在ISE中查看当前操作的SRAM读写时序。

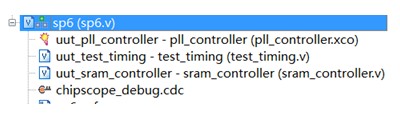

该实例的工程模块划分层次如图所示。

● Sp6.v是顶层模块,主要完成各个子模块例化、相互接口的互联。

● Pll_controller.v模块是IP核,例化PLL功能完成时钟的倍频、分频管理。

● Test_timing.v模块产生SRAM的遍历读写请求,比对写入和读出的SRAM值是否一致,结果赋值给LED指示灯。

● Chipscope_debug.cdc模块引出设计模块内部信号,在chipscope下可以在线观察SRAM的读写时序。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 迄今为止最牛的ASIC验证平台(05-22)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)