可编程逻辑能为微控制器带来什么改变?

时间:09-14

来源:互联网

点击:

在过去25年里,微控制器的内部外设发生了巨大的变化。最初许多微控制器只包含RAM、ROM,也许还有基本的定时器。随着微控制器的发展,更多的外设被基础到这种单价不超过一美元的器件中。定时器/计数器、PWM和包括UART、SPI和I2C在内的标准串行接口常用于这些廉价的微控制器。另一个重大变化是32位CPU正在取代同一价格范围的8位器件。

但是即便有如此丰富的特性,对于廉价微控制器而言,随时都存在微控制器厂商不能迅速支持的项目专用硬件接口或新的第三方接口。往往这要求设计人员使用外部硬件或是通过位拆裂在固件中实现接口。位拆裂使用固件触发IO端口,一般可用于实现串行接口。如果要监测端口以解码串行数据的时候,也可以使用这种方法。无论是使用外部硬件还是位拆裂来实现接口,都会产生额外的设计成本。虽然增加外部硬件带来的成本是明显的,但使用软件实现串行接口可能也会要求使用速度更快因而也更加昂贵的CPU。

大多数通用微控制器今天都支持SPI、UART和I2C接口,但仍然有很多时候,某些内部用户可编程逻辑会非常有用。Atmel、赛普拉斯、Microchip和NXP等多家公司已经把部分用户可定义逻辑添加到自己的部件上,用于修复部分此类问题。这些器件主要是带附加逻辑的微控制器。CPU仍然是主要的处理器件,附加逻辑的作用是提高CPU的工作效率。这类器件常见于成本敏感性产品中,但也在低级任务中用作小型协处理器,以减轻主处理器的负担,从而提升效率。

另一方面FPGA也正在朝着类似的目标前进,虽然是从另一个方向。赛灵思和Altera多年来一直在添加软硬核处理器以创建片上系统。FPGA方法一般成本较高,但如果项目需要大量定制逻辑,这就是一种高成本效益的方法。这些器件对于构建ASIC、小批量产品的原型而言极具价值。这类应用的上市时间至关重要,而较大型产品需要持续的硬件灵活性。

微控制器搭配逻辑与FPGA搭配CPU,这两种器件类型都能为现场提供硬件灵活性。一旦基于闪存的器件成为常规,现场升级就会成为标准。最早设计人员只能够升级固件,但现在硬件(逻辑)和固件都能够在现场轻松实现升级。从计算机鼠标到高速网络路由器等设备均能够重新编写设备的固件和硬件,从而进行现场升级。

上文提及的四家公司(Atmel、赛普拉斯、Microchip和NXP)均可提供“胶连”逻辑,帮助减轻主处理器的负荷,或是无需使用外部逻辑。就提供的逻辑模块类型和这些逻辑模块彼此互联的方式以及与定时器、UART和IO引脚等板载模块互联的方式而言,每家公司都采取了不同的方法。

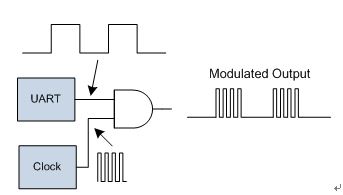

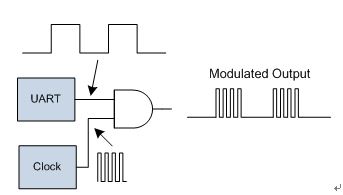

因此有必要了解这些厂家各自是如何实现内部可编程逻辑的,以便为选择最适合自己项目的解决方案做出最佳决策。只要一个简单的内部AND或者OR门控就足以避免使用外部组件,或是改善CPU性能。所有四种方法都支持用定制逻辑门控输入和输出信号。这类方法可借助时钟门控输入,以便使用计数器测量外部时钟频率。这四类逻辑模块均支持的一个简单例子是一种调制UART输出,使之用于IR通信的方法。在此例中,不仅有图1所示的内部AND门控,还能够将来自时钟或计数器的信号及UART TX输出路由到AND门控。

图1 简单调制的UART

Atmel XMEGA定制逻辑(XCL)

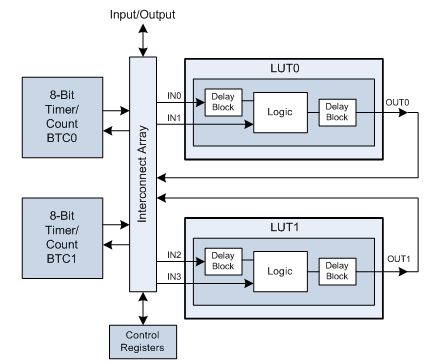

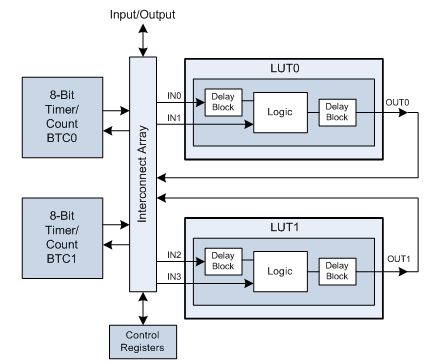

Atmel XCL模块内置两个LUT(查找表)模块,配套两个8位定时器/计数器模块。这两个LUT不必连接到定时器/计数器模块,而是与UART、EVENT模块或IO引脚互联。这两个LUT可用作两个独立的2输入单元或一个单独的3输入单元。该逻辑模块可配置为组合逻辑,如AND、NAND、OR、NOR、XOR、XNOR、NOT或MUX功能。它们也可配置为顺序逻辑功能,例如D触发器、D锁存器或RS锁存器。由于能够与其它逻辑模块和IO引脚互联,这些简单的LUT模块能够方便地让设计人员避免使用某些外部逻辑,或者节省CPU周期。例如Atmel XCL模块应用手册(AT01084)解释了如何配置XCL模块,以避免在产生额外CPU开销或使用外部逻辑的情况下,为UART输出提供曼彻斯特编码。AVR XMEGA E器件内置一个XCL模块。

图2 Atmel的XMEGA定制逻辑(XCL)

Microchip可配置逻辑单元(CLC)

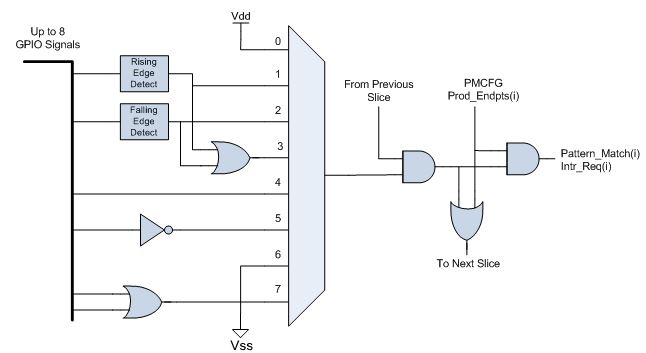

Microchip CLC允许用户从八路输入中选择最多四个信号。这些输入可以是两个IO引脚、内部时钟、外设或寄存器位的组合。这四个信号随后路由到可编程逻辑模块中。该逻辑模块可编程为AND-OR、OR-XOR、4输入AND、S-R锁存器的8种组合之一,也可配置为4种其它触发器组合之一。Microchip在其《可配置逻辑单元提示与技巧》应用手册中给出了部分实例。其中的实例之一演示了如何配置这些模块以解码正交信号。在不使用这些额外的逻辑模块情况下,CPU需要以高得多的速率采样信号,才能避免正处于转换阶段的信号发生伪旋转,让CPU只被有效转换中断。Microchip PIC10(L)F320/322器件每个都包含一个CLC模块,而每个CLC模块都包含四个图3所示的模块。

图3 Microchip的可配置逻辑单元(4个中的一个)

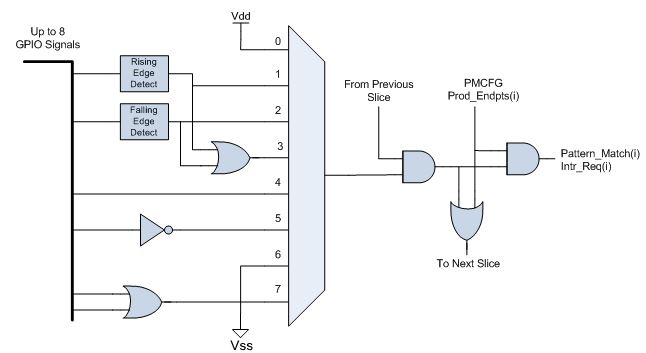

NXP模式匹配引擎

NXP提供的用户可配置逻辑被称为模式匹配引擎。该逻辑模块的输入可选择最大八个GPIO输入。这八个输入可为复杂的布尔表达生成乘积项。这些输出可用于触发中断,驱动特殊IO引脚,或是路由到下一个逻辑模块或slice。其它特性则支持上升或下降信号以及反相信号的边缘检测。该附加硬件经配置后,只有发生复杂(或简单)事件组合时才中断CPU。NXP LPC81x器件内置一个模式匹配引擎。

图4 NXP引脚中断/模式匹配引擎

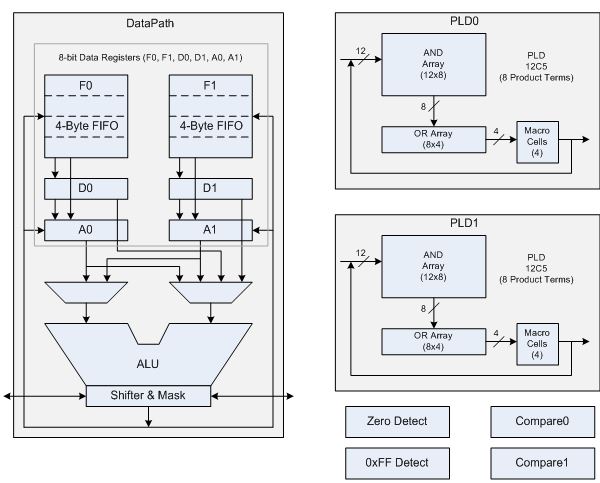

赛普拉斯PSoC通用数字模块(UDB)

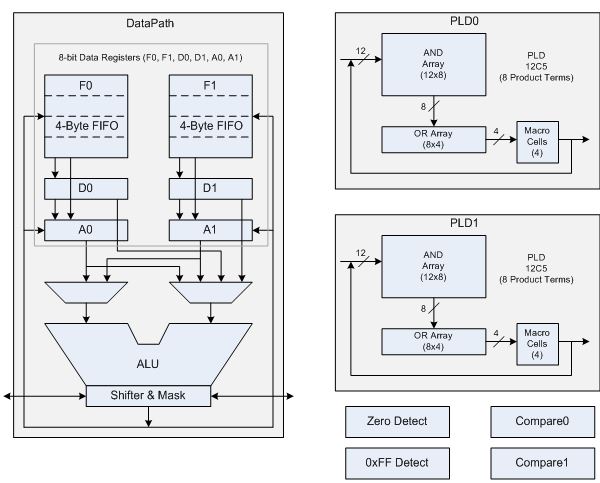

赛普拉斯通过使用通用数字模块或UDB,采用更先进的方法在上文介绍的其他三个厂商的方法和FPGA之间独树一帜。一个UDB由两个12C4 PLD和一个数据通路构成。PLD可用于控制数据通路的操作和数据流,也可用作通用逻辑和状态机。数据通路是一种能提供8位功能(AND、OR、ADD、SUB、INC、DEC、XOR)、移位功能(左和右)以及供数据排队的两个4字节FIFO的定制模块。这些模块也可以结合在一起提供16位、24位或32位功能。

UDB的输入和输出可路由到任何GPIO、外设/组件IO、中断等。UDB、固定功能模拟和数字模块以及GPIO之间的互联都使用数字信号接口(DSI)处理。UDB经编程可实现为任何功能,包括从简单的逻辑门到计数器和PWM以及UART和I2C外设等通用串行接口。

就利用UDB实现设计而言,用户可以选择多种选项。既可把简单的逻辑门布局在原理图中,也可在Verilog中实现设计。还可提供定制图形界面,无需使用Verilog即可实现设计。PSoC 3、PSoC 4和PSoC 5系列微控制器可包含4个到24个此类逻辑模块(UDB)。

图5 赛普拉斯PSoC通用数字模块(UDB)

定制接口实例

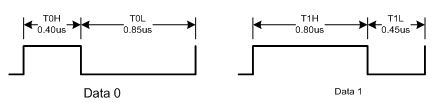

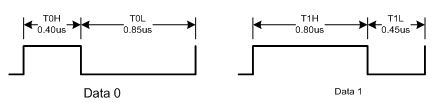

最近我注意到Worldsemi生产的一些RGB LED很有意思。部件编号分别为WS2811、WS2812和WS2812B,但它们工作方式一致。只需要一个GPIO引脚,您就可以驱动1,000个或者更多的此类部件。这相当令人感兴趣,因为我能够用一个GPIO引脚控制如此大数量的RGB LED。连接这些LED的接口不是SPI、UART或I2C,而是定制接口。通信信号采用异步信号,每一位开始于上升沿。数据为1或0由下图所示的高脉冲长度决定。

图6 WS2811/12数据0/1时序

每个部件需要24位数据,每一种颜色(红、绿、蓝)为下列格式的8位。

图7 WS2811/12数据格式

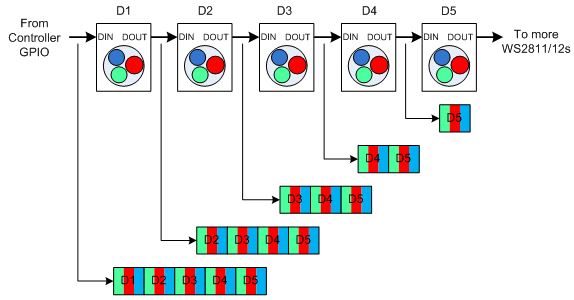

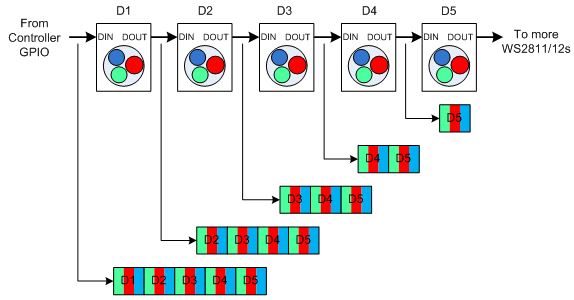

WS2811/12部件采用DIN(数据输入)和DOUT(数据输出)信号,以便简单地进行串行连接。每个部件都保留其看到的头24位数据,然后把剩余数据从DOUT引脚输出。参见下面的图8。

图8 连接多个WS2811/12部件

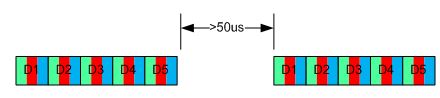

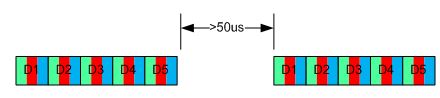

当数据流启动后,每个部件将看到持续的数据流。如果数据信号的上升沿不超过50微秒,部件会锁存数据,将紧邻的24位数据视为自己的数据,并将其余数据重新发送出去。

图9 数据流闲置时间超过50微秒时器件复位

正如您所看到的,其原理并不复杂,但它并不能轻松地适配到标准的微控制器硬件上。我确实发现有人使用SPI接口来维持时序,但这要求每个真实的数据位使用至少三个SPI数据位,对于通过位拆裂获得CPU性能而言优势不大。由于时序并不严格,如果您在固件中实现接口(位拆裂),CPU将专门用于翻转驱动信号直至LED全部更新。这意味着您需要禁用所有中断,在整个过程中不对任何其它输入做出响应。如果您有1,000个LED,则更新时间为(0.40微秒+0.85)*24位*1,000个LED=30,000微秒或30毫秒。这可能并不是什么问题,但如果您要以30Hz的频率更新LED,将几乎占用100%的CPU!

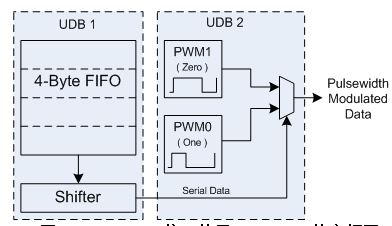

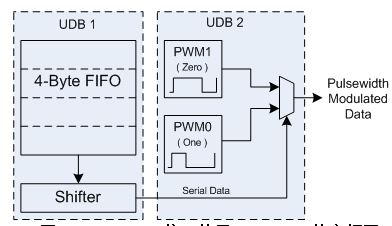

在编写代码时,我习惯于在不得不较长时间禁用中断的地方避免阻塞代码或条件,特别在系统中有用户接口或是需要与其它处理器通信的情况下尤为如此。我的目的是尽量减轻CPU的负担,让硬件完成大部分工作,就如同今天常见的内部UART或SPI模块所做的工作一样。赛普拉斯PSoC UDB有几项特性能让这项工作变得非常简便。每个UDB在数据通路中有两个4字节FIFO和一个移位器。在实现UART时,您可将一个FIFO用作TX缓存,另一个用作RX缓存。对于WS2811/12,我只需要一个输出FIFO和移位器。我决定配置硬件,为每个器件每次生成一次中断。中断处理器将加载24位(3字节)数据,直到FIFO为空时返回。采用这种方法,可以每30微秒中断一次,而不必以150毫微秒或更短间隔禁用全部中断和位拆裂。我决定使用的微控制器是赛普拉斯PSoC CY8C4245AXI。该微控制器大批量采购价格约为一美元,有四个UDB,运行频率为48MHz,足以满足此项工作所需的速度和硬件要求。

设计使用了PSoC提供的四个UDB中的两个。一个用于使用FIFO缓冲数据和移位数据,这样每个器件的全部24位(3字节)可一次性写入。第二个UDB可使用两个比较输出创建PWM。一个比较输出用于创建逻辑0,另一个用于创建逻辑1。该串行数据可用于控制数字多路复用器,选择波形1或0。敬请参见下图10的方框图。

图10 WS2811/12接口使用PSoC UDB的方框图

UDB中四个PLD(每个UDB有2个)的大多数乘积项可用于控制数据通路,生成中断,提供状态和控制功能,但这也使用了这种低成本微控制器中一半的UDB资源。

接下来的工作是明确这一附加硬件能为设计节省多少CPU开销。以1,000个LED组成的阵列为例,其刷新频率为30Hz。如果设计使用固件对接口进行位拆裂操作,会差不多占用100%的CPU资源。使用PSoC器件中的可编程硬件仍然可以做到每30微秒中断一次,虽然这也是较重的负荷,但运行在48MHz的ARM Cortex-M0足以应付。为测试CPU开销,我创建了一个简单的环路,以大约30Hz的频率刷新显示器。在主环路中,我触发了一个引脚,然后使用示波器计算40毫秒内的触发数量。然后我禁用中断,再次运行项目,并比较结果。与使用固件中的位拆裂造成的几乎100%的CPU占用相比,持续显示刷新只占用大约12%的CPU资源。这样另外88%的CPU周期可用于外部通信和用户界面。如果为设计添加DMA,该开销可能会从12%下降到2%或更低。我使用的最廉价PSoC(约1美元)只包含UDB但未包含DMA,不过一些较大型的部件确实内置有DMA。

随后我实际制作了一个由60x16个LED(960个LED)网格组成的真正RGB LED板,用于测试该组件。该组件的运行符合预期,可用作显示基本的直线、矩形、圆圈以及文本的图形界面。

图11 使用960个RGB LED制作的广告牌

无论是大型LED板还是简单的定制界面,部分内部可编程硬件会给设计性能造成重大影响。不是每一种定制界面都需要多字节FIFO或全硬件状态机,但拥有这种灵活性能为您提供更多设计选择、提高性能,或是让现有设计迅速适合产品需求。

但是即便有如此丰富的特性,对于廉价微控制器而言,随时都存在微控制器厂商不能迅速支持的项目专用硬件接口或新的第三方接口。往往这要求设计人员使用外部硬件或是通过位拆裂在固件中实现接口。位拆裂使用固件触发IO端口,一般可用于实现串行接口。如果要监测端口以解码串行数据的时候,也可以使用这种方法。无论是使用外部硬件还是位拆裂来实现接口,都会产生额外的设计成本。虽然增加外部硬件带来的成本是明显的,但使用软件实现串行接口可能也会要求使用速度更快因而也更加昂贵的CPU。

大多数通用微控制器今天都支持SPI、UART和I2C接口,但仍然有很多时候,某些内部用户可编程逻辑会非常有用。Atmel、赛普拉斯、Microchip和NXP等多家公司已经把部分用户可定义逻辑添加到自己的部件上,用于修复部分此类问题。这些器件主要是带附加逻辑的微控制器。CPU仍然是主要的处理器件,附加逻辑的作用是提高CPU的工作效率。这类器件常见于成本敏感性产品中,但也在低级任务中用作小型协处理器,以减轻主处理器的负担,从而提升效率。

另一方面FPGA也正在朝着类似的目标前进,虽然是从另一个方向。赛灵思和Altera多年来一直在添加软硬核处理器以创建片上系统。FPGA方法一般成本较高,但如果项目需要大量定制逻辑,这就是一种高成本效益的方法。这些器件对于构建ASIC、小批量产品的原型而言极具价值。这类应用的上市时间至关重要,而较大型产品需要持续的硬件灵活性。

微控制器搭配逻辑与FPGA搭配CPU,这两种器件类型都能为现场提供硬件灵活性。一旦基于闪存的器件成为常规,现场升级就会成为标准。最早设计人员只能够升级固件,但现在硬件(逻辑)和固件都能够在现场轻松实现升级。从计算机鼠标到高速网络路由器等设备均能够重新编写设备的固件和硬件,从而进行现场升级。

上文提及的四家公司(Atmel、赛普拉斯、Microchip和NXP)均可提供“胶连”逻辑,帮助减轻主处理器的负荷,或是无需使用外部逻辑。就提供的逻辑模块类型和这些逻辑模块彼此互联的方式以及与定时器、UART和IO引脚等板载模块互联的方式而言,每家公司都采取了不同的方法。

因此有必要了解这些厂家各自是如何实现内部可编程逻辑的,以便为选择最适合自己项目的解决方案做出最佳决策。只要一个简单的内部AND或者OR门控就足以避免使用外部组件,或是改善CPU性能。所有四种方法都支持用定制逻辑门控输入和输出信号。这类方法可借助时钟门控输入,以便使用计数器测量外部时钟频率。这四类逻辑模块均支持的一个简单例子是一种调制UART输出,使之用于IR通信的方法。在此例中,不仅有图1所示的内部AND门控,还能够将来自时钟或计数器的信号及UART TX输出路由到AND门控。

图1 简单调制的UART

Atmel XMEGA定制逻辑(XCL)

Atmel XCL模块内置两个LUT(查找表)模块,配套两个8位定时器/计数器模块。这两个LUT不必连接到定时器/计数器模块,而是与UART、EVENT模块或IO引脚互联。这两个LUT可用作两个独立的2输入单元或一个单独的3输入单元。该逻辑模块可配置为组合逻辑,如AND、NAND、OR、NOR、XOR、XNOR、NOT或MUX功能。它们也可配置为顺序逻辑功能,例如D触发器、D锁存器或RS锁存器。由于能够与其它逻辑模块和IO引脚互联,这些简单的LUT模块能够方便地让设计人员避免使用某些外部逻辑,或者节省CPU周期。例如Atmel XCL模块应用手册(AT01084)解释了如何配置XCL模块,以避免在产生额外CPU开销或使用外部逻辑的情况下,为UART输出提供曼彻斯特编码。AVR XMEGA E器件内置一个XCL模块。

图2 Atmel的XMEGA定制逻辑(XCL)

Microchip可配置逻辑单元(CLC)

Microchip CLC允许用户从八路输入中选择最多四个信号。这些输入可以是两个IO引脚、内部时钟、外设或寄存器位的组合。这四个信号随后路由到可编程逻辑模块中。该逻辑模块可编程为AND-OR、OR-XOR、4输入AND、S-R锁存器的8种组合之一,也可配置为4种其它触发器组合之一。Microchip在其《可配置逻辑单元提示与技巧》应用手册中给出了部分实例。其中的实例之一演示了如何配置这些模块以解码正交信号。在不使用这些额外的逻辑模块情况下,CPU需要以高得多的速率采样信号,才能避免正处于转换阶段的信号发生伪旋转,让CPU只被有效转换中断。Microchip PIC10(L)F320/322器件每个都包含一个CLC模块,而每个CLC模块都包含四个图3所示的模块。

图3 Microchip的可配置逻辑单元(4个中的一个)

NXP模式匹配引擎

NXP提供的用户可配置逻辑被称为模式匹配引擎。该逻辑模块的输入可选择最大八个GPIO输入。这八个输入可为复杂的布尔表达生成乘积项。这些输出可用于触发中断,驱动特殊IO引脚,或是路由到下一个逻辑模块或slice。其它特性则支持上升或下降信号以及反相信号的边缘检测。该附加硬件经配置后,只有发生复杂(或简单)事件组合时才中断CPU。NXP LPC81x器件内置一个模式匹配引擎。

图4 NXP引脚中断/模式匹配引擎

赛普拉斯PSoC通用数字模块(UDB)

赛普拉斯通过使用通用数字模块或UDB,采用更先进的方法在上文介绍的其他三个厂商的方法和FPGA之间独树一帜。一个UDB由两个12C4 PLD和一个数据通路构成。PLD可用于控制数据通路的操作和数据流,也可用作通用逻辑和状态机。数据通路是一种能提供8位功能(AND、OR、ADD、SUB、INC、DEC、XOR)、移位功能(左和右)以及供数据排队的两个4字节FIFO的定制模块。这些模块也可以结合在一起提供16位、24位或32位功能。

UDB的输入和输出可路由到任何GPIO、外设/组件IO、中断等。UDB、固定功能模拟和数字模块以及GPIO之间的互联都使用数字信号接口(DSI)处理。UDB经编程可实现为任何功能,包括从简单的逻辑门到计数器和PWM以及UART和I2C外设等通用串行接口。

就利用UDB实现设计而言,用户可以选择多种选项。既可把简单的逻辑门布局在原理图中,也可在Verilog中实现设计。还可提供定制图形界面,无需使用Verilog即可实现设计。PSoC 3、PSoC 4和PSoC 5系列微控制器可包含4个到24个此类逻辑模块(UDB)。

图5 赛普拉斯PSoC通用数字模块(UDB)

定制接口实例

最近我注意到Worldsemi生产的一些RGB LED很有意思。部件编号分别为WS2811、WS2812和WS2812B,但它们工作方式一致。只需要一个GPIO引脚,您就可以驱动1,000个或者更多的此类部件。这相当令人感兴趣,因为我能够用一个GPIO引脚控制如此大数量的RGB LED。连接这些LED的接口不是SPI、UART或I2C,而是定制接口。通信信号采用异步信号,每一位开始于上升沿。数据为1或0由下图所示的高脉冲长度决定。

图6 WS2811/12数据0/1时序

每个部件需要24位数据,每一种颜色(红、绿、蓝)为下列格式的8位。

图7 WS2811/12数据格式

WS2811/12部件采用DIN(数据输入)和DOUT(数据输出)信号,以便简单地进行串行连接。每个部件都保留其看到的头24位数据,然后把剩余数据从DOUT引脚输出。参见下面的图8。

图8 连接多个WS2811/12部件

当数据流启动后,每个部件将看到持续的数据流。如果数据信号的上升沿不超过50微秒,部件会锁存数据,将紧邻的24位数据视为自己的数据,并将其余数据重新发送出去。

图9 数据流闲置时间超过50微秒时器件复位

正如您所看到的,其原理并不复杂,但它并不能轻松地适配到标准的微控制器硬件上。我确实发现有人使用SPI接口来维持时序,但这要求每个真实的数据位使用至少三个SPI数据位,对于通过位拆裂获得CPU性能而言优势不大。由于时序并不严格,如果您在固件中实现接口(位拆裂),CPU将专门用于翻转驱动信号直至LED全部更新。这意味着您需要禁用所有中断,在整个过程中不对任何其它输入做出响应。如果您有1,000个LED,则更新时间为(0.40微秒+0.85)*24位*1,000个LED=30,000微秒或30毫秒。这可能并不是什么问题,但如果您要以30Hz的频率更新LED,将几乎占用100%的CPU!

在编写代码时,我习惯于在不得不较长时间禁用中断的地方避免阻塞代码或条件,特别在系统中有用户接口或是需要与其它处理器通信的情况下尤为如此。我的目的是尽量减轻CPU的负担,让硬件完成大部分工作,就如同今天常见的内部UART或SPI模块所做的工作一样。赛普拉斯PSoC UDB有几项特性能让这项工作变得非常简便。每个UDB在数据通路中有两个4字节FIFO和一个移位器。在实现UART时,您可将一个FIFO用作TX缓存,另一个用作RX缓存。对于WS2811/12,我只需要一个输出FIFO和移位器。我决定配置硬件,为每个器件每次生成一次中断。中断处理器将加载24位(3字节)数据,直到FIFO为空时返回。采用这种方法,可以每30微秒中断一次,而不必以150毫微秒或更短间隔禁用全部中断和位拆裂。我决定使用的微控制器是赛普拉斯PSoC CY8C4245AXI。该微控制器大批量采购价格约为一美元,有四个UDB,运行频率为48MHz,足以满足此项工作所需的速度和硬件要求。

设计使用了PSoC提供的四个UDB中的两个。一个用于使用FIFO缓冲数据和移位数据,这样每个器件的全部24位(3字节)可一次性写入。第二个UDB可使用两个比较输出创建PWM。一个比较输出用于创建逻辑0,另一个用于创建逻辑1。该串行数据可用于控制数字多路复用器,选择波形1或0。敬请参见下图10的方框图。

图10 WS2811/12接口使用PSoC UDB的方框图

UDB中四个PLD(每个UDB有2个)的大多数乘积项可用于控制数据通路,生成中断,提供状态和控制功能,但这也使用了这种低成本微控制器中一半的UDB资源。

接下来的工作是明确这一附加硬件能为设计节省多少CPU开销。以1,000个LED组成的阵列为例,其刷新频率为30Hz。如果设计使用固件对接口进行位拆裂操作,会差不多占用100%的CPU资源。使用PSoC器件中的可编程硬件仍然可以做到每30微秒中断一次,虽然这也是较重的负荷,但运行在48MHz的ARM Cortex-M0足以应付。为测试CPU开销,我创建了一个简单的环路,以大约30Hz的频率刷新显示器。在主环路中,我触发了一个引脚,然后使用示波器计算40毫秒内的触发数量。然后我禁用中断,再次运行项目,并比较结果。与使用固件中的位拆裂造成的几乎100%的CPU占用相比,持续显示刷新只占用大约12%的CPU资源。这样另外88%的CPU周期可用于外部通信和用户界面。如果为设计添加DMA,该开销可能会从12%下降到2%或更低。我使用的最廉价PSoC(约1美元)只包含UDB但未包含DMA,不过一些较大型的部件确实内置有DMA。

随后我实际制作了一个由60x16个LED(960个LED)网格组成的真正RGB LED板,用于测试该组件。该组件的运行符合预期,可用作显示基本的直线、矩形、圆圈以及文本的图形界面。

图11 使用960个RGB LED制作的广告牌

无论是大型LED板还是简单的定制界面,部分内部可编程硬件会给设计性能造成重大影响。不是每一种定制界面都需要多字节FIFO或全硬件状态机,但拥有这种灵活性能为您提供更多设计选择、提高性能,或是让现有设计迅速适合产品需求。

PWM Atmel 赛普拉斯 Microchip NXP FPGA 赛灵思 Altera AVR PIC SoC Verilog PSoC LED ARM Cortex 显示器 示波器 相关文章:

- 基于Actel FPGA的PWM IP的应用(09-17)

- 适用于消费性市场的nano FPGA技术(09-27)

- 现场可编程门阵列的供电(03-24)

- 基于FPGA的UPFC控制器IP设计(07-18)

- CPLD器件在单片机控制器中的使用(07-24)

- 基于FPGA的步进电机正弦波细分驱动器设计(08-02)