Vivado使用误区与进阶——XDC约束技巧之I/O篇 (上)

时间:03-24

来源:互联网

点击:

作者:周丽娜(Ally Zhou ),Xilinx工具与方法学应用专家

《XDC约束技巧之时钟篇》中曾对I/O约束做过简要概括,相比较而言,XDC中的I/O约束虽然形式简单,但整体思路和约束方法却与UCF大相径庭。加之FPGA的应用特性决定了其在接口上有多种构建和实现方式,所以从UCF到XDC的转换过程中,最具挑战的可以说便是本文将要讨论的I/O约束了。

I/O 约束的语法

XDC 中可以用于 I/O 约束的命令包括 set_input_delay / set_output_delay 和set_max_delay / set_min_delay 。其中,只有那些从 FPGA 管脚进入和/或输出都不经过任何时序元件的纯组合逻辑路径可以用 set_max_delay / set_min_delay 来约束,其余 I/O 时序路径都必须由set_input_delay / set_output_delay 来约束。如果对 FPGA 的 I/O 不加任何约束,Vivado 会缺省认为时序要求为无穷大,不仅综合和实现时不会考虑 I/O 时序,而且在时序分析时也不会报出这些未约束的路径。

本文以下章节将会着重讨论 XDC 接口约束和时序分析的基础,介绍如何使用set_input_delay / set_output_delay 对 FPGA 的 I/O 时序进行约束。

Input 约束

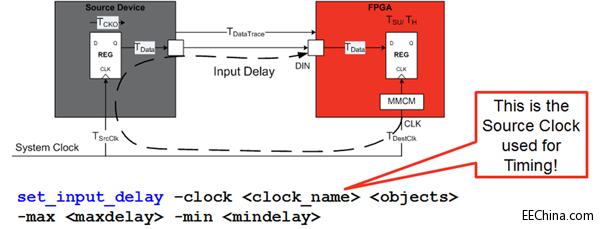

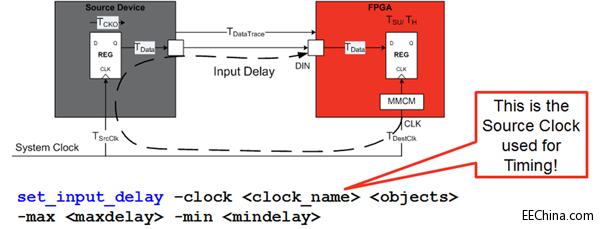

上图所示 set_input_delay 的基本语法中, 是想要设定 input 约束的端口名,可以是一个或数个 port;-clock 之后的 指明了对 时序进行分析所用的时钟,可以是一个 FPGA 中真实存在的时钟也可以是预先定义好的虚拟时钟;-max 之后的 描述了用于 setup 分析的包含有板级走线和外部器件的延时;-min 之后的 描述了用于 hold 分析的包含有板级走线和外部器件的延时。

上述这些选项是定义 Input 约束时必须写明的,还有少数几个可选项,如 -add_delay和 -clock_fall 用于 DDR 接口的约束。

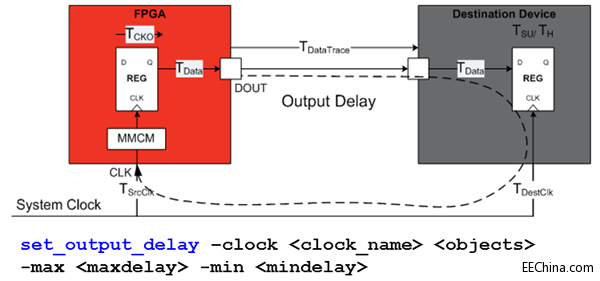

Output 约束

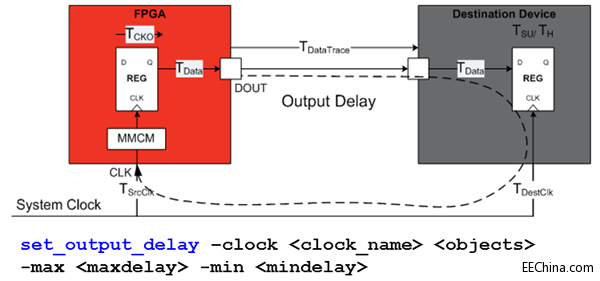

上图所示 set_output_delay 的基本语法中, 是想要设定 output 约束的端口名,可以是一个或数个 port;-clock 之后的 指明了对 时序进行分析所用的时钟,可以是一个 FPGA 中真实存在的时钟也可以是预先定义好的虚拟时钟;-max 之后的 描述了用于 setup 分析的包含有板级走线和外部器件的延时;-min之后的 描述了用于 hold 分析的包含有板级走线和外部器件的延时。

上述这些选项是定义 Output 约束时必须写明的,还有少数几个可选项如 -add_delay和 -clock_fall 用于 DDR 接口的约束。

Setup/Hold 时序分析

我们知道约束是为了设计服务,而设置好的约束必须在时序报告中加以验证。所以,怎样理解时序分析中的检查规则就成了重中之重,这一点对 I/O 约束来说尤为重要。理解时序分析工具如何选取路径分析的发送端(Launch)和接收端(Capture)时钟沿(Clock Edges),在 Setup 和 Hold 分析时又有怎样的具体区别,以及这些数字在时序报告中如何体现等等是设置正确 I/O 约束的基础。

更具体的时序分析方法以及如何深入解读时序报告等内容将会在后续另开主题文章详述,这里仅就 Setup/Hold 分析时对时钟边沿的选择加以描述,便于以下章节的展开。

Setup 时序分析

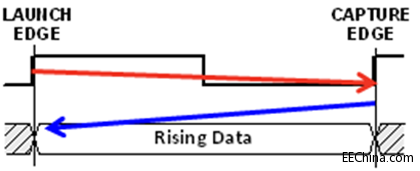

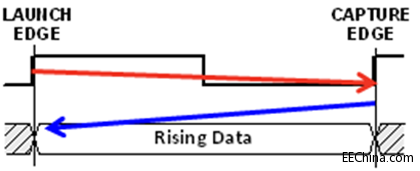

同步电路设计中,一般情况下,数据在时钟上升沿发送,在下一个时钟上升沿接收,发送的时钟沿称作 Launch Edge,接收沿称作 Capture Edge。时序分析中的 Setup Check 跟Capture Edge 的选择息息相关。

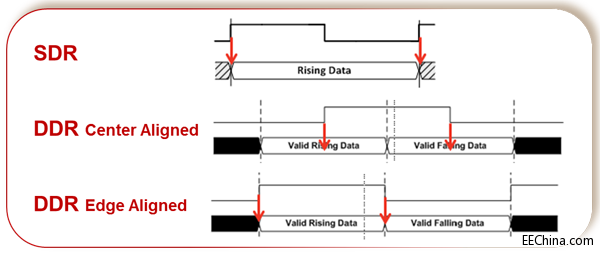

在 SDR 接口的 setup 分析中,工具如下图这样识别发送和接收时钟沿。

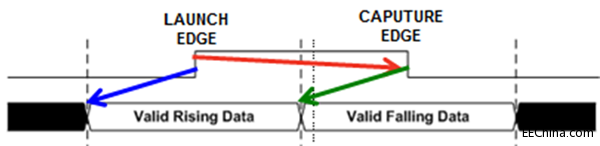

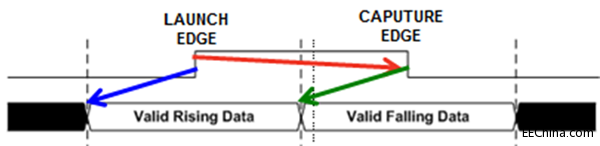

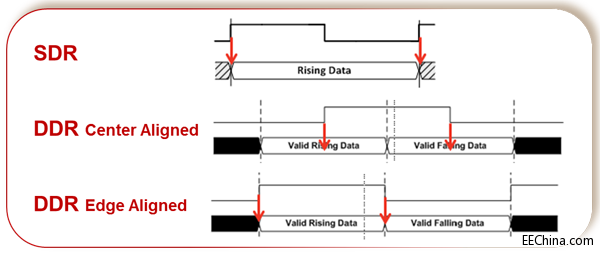

而在 DDR 接口的 setup 分析中,因为数据是双沿采样,所以发送和接收时钟沿变成上升(下降)沿发送,下降(上升)沿接收。

Hold 时序分析

Hold Check 主要是为了保证数据在接收(采样)端时钟沿之后还能稳定保持一段时间,对 Hold 分析而言,同一个时钟沿既是 Launch Edge 也是 Capture Edge,这一点对 SDR和 DDR(不论是中心对齐还是边沿对齐)都一样。

Input 接口类型和约束

由于历史的原因,相当一部分 FPGA 设计仍然在系统中起到胶合逻辑(Glue Logic)的作用,当然,如今的 FPGA 中嵌入了高速串行收发器和嵌入式处理器等,早就不仅仅局限于系统设计的配角,反而成为了其中的主角甚至是明星。但数据接口的同步一直是FPGA 设计中的常见问题,也是一个重点和难点,很多设计不稳定都是因为数据接口的同步有问题。

FPGA 的数据接口同步根据系统级设计方式来讲可以分为系统同步和源同步两种。

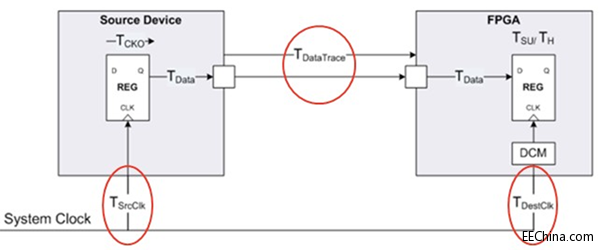

系统同步接口

系统同步接口(System Synchronous Interface)的构建相对容易,以 FPGA 做接收侧来举例,上游器件仅仅传递数据信号到 FPGA 中,时钟信号则完全依靠系统板级来同步。时钟信号在系统级上同源,板级走线的延时也要对齐。正因为这样的设计,决定了数据传递的性能受到时钟在系统级的走线延时和 skew 以及数据路径延时的双重限制,无法达到更高速的设计要求,所以大部分情况也仅仅应用 SDR 方式。

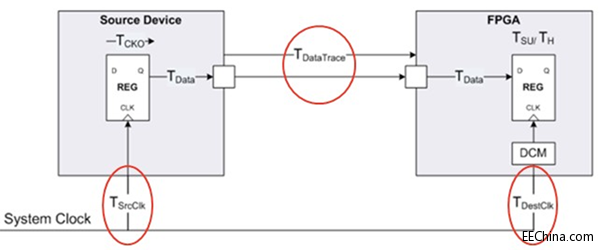

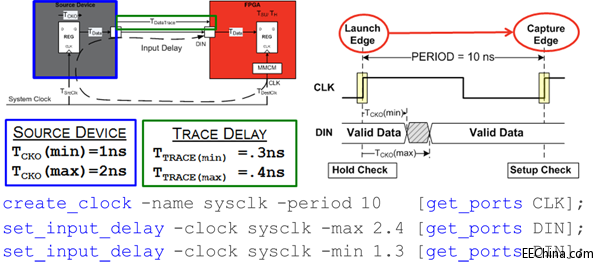

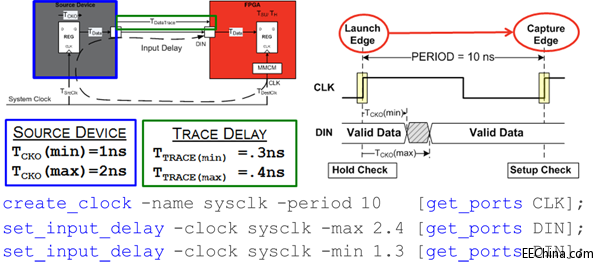

对系统同步接口做 Input 约束相对容易,只需要考虑上游器件的 Tcko 和数据在板级的延时即可。下图是一个 SDR 上升沿采样系统同步接口的 Input 约束示例。

设置和分析 I/O 约束一定要有个系统级思考的视角,如上右图所示,Launch Edge 对应的是上游器件的时钟,而 Capture Edge 则对应 FPGA 的输入时钟,正因为是系统同步时钟,所以可以将其视作完全同步而放在一张图上分析,这样一来,就可以用一般时序分析方法来看待问题。

一条完整的时序路径,从源触发器的 C 端开始,经过 Tcko 和路径传输延时再到目的触发器的 D 端结束。放在系统同步的接口时序上,传输延时则变成板级传输延时(还要考虑 skew),所以上述 -max 后的数值是 Tcko 的最大值加上板级延时的最大值而来,而-min后的数值则是由两个最小值相加而来。

《XDC约束技巧之时钟篇》中曾对I/O约束做过简要概括,相比较而言,XDC中的I/O约束虽然形式简单,但整体思路和约束方法却与UCF大相径庭。加之FPGA的应用特性决定了其在接口上有多种构建和实现方式,所以从UCF到XDC的转换过程中,最具挑战的可以说便是本文将要讨论的I/O约束了。

I/O 约束的语法

XDC 中可以用于 I/O 约束的命令包括 set_input_delay / set_output_delay 和set_max_delay / set_min_delay 。其中,只有那些从 FPGA 管脚进入和/或输出都不经过任何时序元件的纯组合逻辑路径可以用 set_max_delay / set_min_delay 来约束,其余 I/O 时序路径都必须由set_input_delay / set_output_delay 来约束。如果对 FPGA 的 I/O 不加任何约束,Vivado 会缺省认为时序要求为无穷大,不仅综合和实现时不会考虑 I/O 时序,而且在时序分析时也不会报出这些未约束的路径。

本文以下章节将会着重讨论 XDC 接口约束和时序分析的基础,介绍如何使用set_input_delay / set_output_delay 对 FPGA 的 I/O 时序进行约束。

Input 约束

上图所示 set_input_delay 的基本语法中, 是想要设定 input 约束的端口名,可以是一个或数个 port;-clock 之后的 指明了对 时序进行分析所用的时钟,可以是一个 FPGA 中真实存在的时钟也可以是预先定义好的虚拟时钟;-max 之后的 描述了用于 setup 分析的包含有板级走线和外部器件的延时;-min 之后的 描述了用于 hold 分析的包含有板级走线和外部器件的延时。

上述这些选项是定义 Input 约束时必须写明的,还有少数几个可选项,如 -add_delay和 -clock_fall 用于 DDR 接口的约束。

Output 约束

上图所示 set_output_delay 的基本语法中, 是想要设定 output 约束的端口名,可以是一个或数个 port;-clock 之后的 指明了对 时序进行分析所用的时钟,可以是一个 FPGA 中真实存在的时钟也可以是预先定义好的虚拟时钟;-max 之后的 描述了用于 setup 分析的包含有板级走线和外部器件的延时;-min之后的 描述了用于 hold 分析的包含有板级走线和外部器件的延时。

上述这些选项是定义 Output 约束时必须写明的,还有少数几个可选项如 -add_delay和 -clock_fall 用于 DDR 接口的约束。

Setup/Hold 时序分析

我们知道约束是为了设计服务,而设置好的约束必须在时序报告中加以验证。所以,怎样理解时序分析中的检查规则就成了重中之重,这一点对 I/O 约束来说尤为重要。理解时序分析工具如何选取路径分析的发送端(Launch)和接收端(Capture)时钟沿(Clock Edges),在 Setup 和 Hold 分析时又有怎样的具体区别,以及这些数字在时序报告中如何体现等等是设置正确 I/O 约束的基础。

更具体的时序分析方法以及如何深入解读时序报告等内容将会在后续另开主题文章详述,这里仅就 Setup/Hold 分析时对时钟边沿的选择加以描述,便于以下章节的展开。

Setup 时序分析

同步电路设计中,一般情况下,数据在时钟上升沿发送,在下一个时钟上升沿接收,发送的时钟沿称作 Launch Edge,接收沿称作 Capture Edge。时序分析中的 Setup Check 跟Capture Edge 的选择息息相关。

在 SDR 接口的 setup 分析中,工具如下图这样识别发送和接收时钟沿。

而在 DDR 接口的 setup 分析中,因为数据是双沿采样,所以发送和接收时钟沿变成上升(下降)沿发送,下降(上升)沿接收。

Hold 时序分析

Hold Check 主要是为了保证数据在接收(采样)端时钟沿之后还能稳定保持一段时间,对 Hold 分析而言,同一个时钟沿既是 Launch Edge 也是 Capture Edge,这一点对 SDR和 DDR(不论是中心对齐还是边沿对齐)都一样。

Input 接口类型和约束

由于历史的原因,相当一部分 FPGA 设计仍然在系统中起到胶合逻辑(Glue Logic)的作用,当然,如今的 FPGA 中嵌入了高速串行收发器和嵌入式处理器等,早就不仅仅局限于系统设计的配角,反而成为了其中的主角甚至是明星。但数据接口的同步一直是FPGA 设计中的常见问题,也是一个重点和难点,很多设计不稳定都是因为数据接口的同步有问题。

FPGA 的数据接口同步根据系统级设计方式来讲可以分为系统同步和源同步两种。

系统同步接口

系统同步接口(System Synchronous Interface)的构建相对容易,以 FPGA 做接收侧来举例,上游器件仅仅传递数据信号到 FPGA 中,时钟信号则完全依靠系统板级来同步。时钟信号在系统级上同源,板级走线的延时也要对齐。正因为这样的设计,决定了数据传递的性能受到时钟在系统级的走线延时和 skew 以及数据路径延时的双重限制,无法达到更高速的设计要求,所以大部分情况也仅仅应用 SDR 方式。

对系统同步接口做 Input 约束相对容易,只需要考虑上游器件的 Tcko 和数据在板级的延时即可。下图是一个 SDR 上升沿采样系统同步接口的 Input 约束示例。

设置和分析 I/O 约束一定要有个系统级思考的视角,如上右图所示,Launch Edge 对应的是上游器件的时钟,而 Capture Edge 则对应 FPGA 的输入时钟,正因为是系统同步时钟,所以可以将其视作完全同步而放在一张图上分析,这样一来,就可以用一般时序分析方法来看待问题。

一条完整的时序路径,从源触发器的 C 端开始,经过 Tcko 和路径传输延时再到目的触发器的 D 端结束。放在系统同步的接口时序上,传输延时则变成板级传输延时(还要考虑 skew),所以上述 -max 后的数值是 Tcko 的最大值加上板级延时的最大值而来,而-min后的数值则是由两个最小值相加而来。

Xilinx FPGA 电路 收发器 嵌入式 总线 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 迄今为止最牛的ASIC验证平台(05-22)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)