零基础学FPGA (二十一) 探秘SOPC

时间:02-03

来源:互联网

点击:

作者:小墨同学

今天是来北京的第8天了,想想过的蛮快的,在这8天里呢,由于这边正在开SOPC的课程,自己对这方面之前只是了解过,知道有SOPC这回事,但是从来没有接触过,正好有这个机会让我蹭了几天的课,算是对这东西有了深入的了解吧。课程讲的很快,短短4天的功夫就从入门讲到了我认为比较难懂的方面,不过还好,经过我这几天的消化,之前也有点基础,理解一下还是没什么问题的,只不过让我去操作一个有点难度的外设的话,我估计还得下点功夫了~

讲SOPC的郝老师跟我住一个屋,郝老师人很不错,也很年轻,也是个90后,这几天跟着郝老师学到了不少东西,不仅仅是SOPC方面的,更多还有对工程师这个行业,对这个社会的一些新的认识。

由于我也是刚接触SOPC,不能像大神们讲的那么井井有条,思路严谨,我只是把我最近几天学到的东西跟大家分享一下,也作为自己的一份笔记。再下面的几篇文章中,我都会给大家发一些SOPC的笔记,从基本的概念,到基本硬件系统的搭建,一些常用IP核的应用,像什么PIO核,UART核,USB,EPCS控制器,SDRAM控制器等,还有后面的自定义外设等,估计用四五篇文章的长度来讲这部分吧。

学这一部分知识要软硬结合,硬件相信大家都没问题了,软件呢需要用到C语言的知识,由于我之前很久没用C语言了,如果大家对C语言还不是很熟的话,建议大家回去补一下C语言的课,虽然我们是搞硬件的,但是越到后面,软硬就不分了~

第一篇文章我就先来说说我理解中的SOPC,再教大家手把手搭建一个硬件平台,这个硬件平台搭建好了,我们以后的软件就全部是基于这个平台的编程了。

一、我理解中的SOPC

SOPC呢,也就是所谓的可编程片上系统,通常一个系统所包含的,什么CPU,存储器,DSP和一些IO外设等都放在FPGA的周围,这样大大增加的系统的面积从而增加了系统的成本,SOPC技术呢就是把CPU,DSP,定时器,IO模块都放到FPGA里面,通过Quartus II提供的SOPC builder这个工具,在里面嵌入NIOS II处理器和一些常用的IP 核,NIOS II处理器作为主机,其他外设作为从机,主机和从机之间通过AVALON MM总线进行通信与访问,每一个外设都有一个地址,NIOS II处理器可以通过这条总线对外设进行操作,但是每次只能访问一个外设,系统硬件搭建好了之后,通过Quartus II对其进行综合,布局布线,时序约束等硬件系统搭建工作,然后我们用C语言通过NIOS II eclipse 这个工具来给我们的硬件系统编程,并进行运行调试,最后将我们设计好的硬件与软件文件烧入FPGA的配置芯片或者FILASH中,通过相应的总线来控制相应的外设。下面是我画的一个关系图

下面我们就通过一个具体的实例来理解这个过程

二 、硬件系统搭建

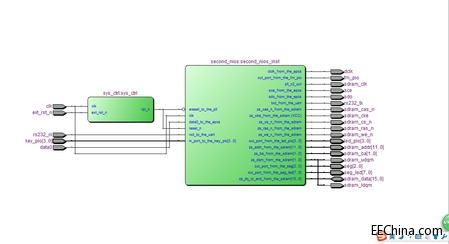

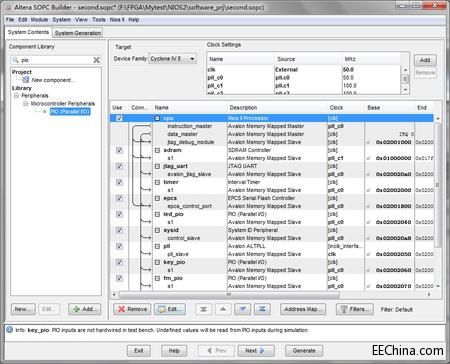

上面这个图就是我们要搭建的硬件系统,硬件系统的搭建需要用到Quartus II软件 和它提供的SOPC builder 工具,一步步来,Quartus II建立工程就不说了,建立工程之后,tool ——sopc builder,按照上面的框图一个个添加我们需要的IP

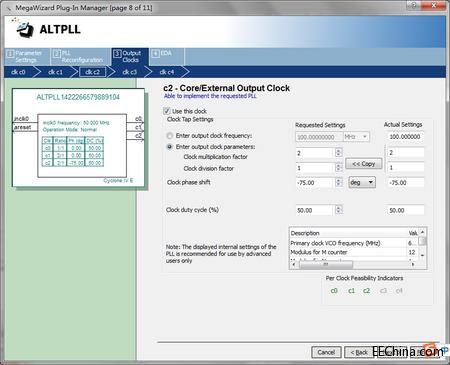

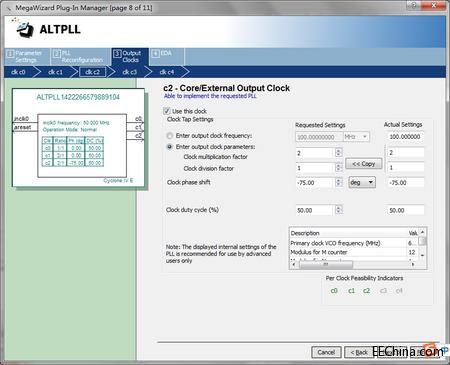

首先我喜欢添加时钟,即PLL,直接在左上方的搜索框里输入PLL双击即可,至于PLL的配置方法我就不说了,相信大家都已经很熟了,由于我们的输入时钟是50M,我们需要的内部时钟主要用来控制各种IP,用50M的c0时钟,但是我们系统设计SDRAM,我们需要100M的c1时钟来控制SDRAM控制器,即SDRAM接口,同样还需要一个时钟输出到FPGA芯片外部来控制SDRAM芯片,我们用C2时钟,C2时钟跟C1时钟同频不同相,根据经验值,这个相位偏移我们选-75deg,频率100M

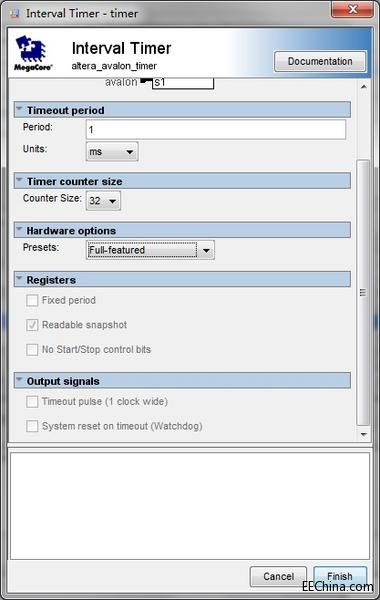

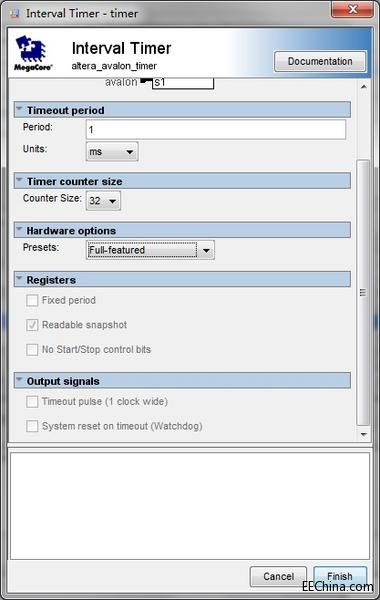

接着添加定时器,在搜索框输入timer 配置定时单位,位宽,这里我们设置为1ms,32位,在硬件选项对话框里一般选择 full—featured,当然也可以手动配置一些参数选custom

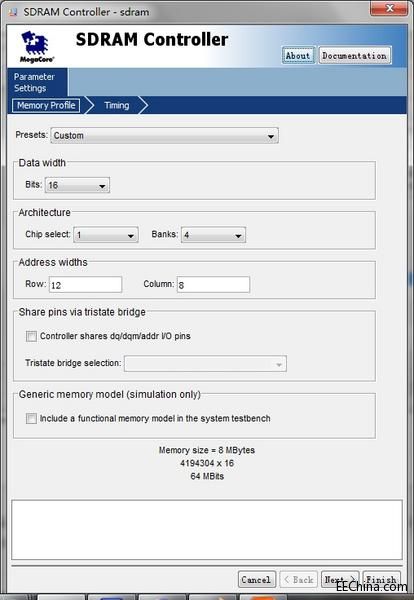

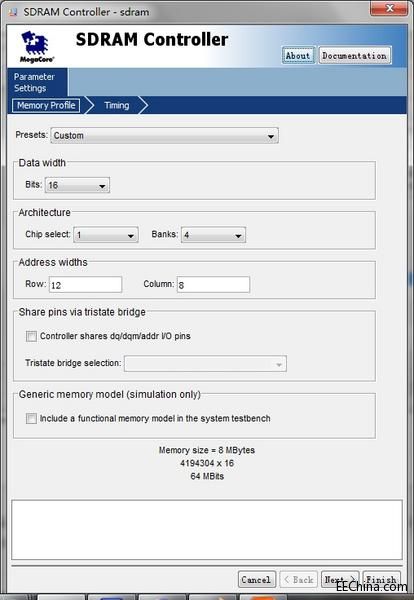

然后我们可以配置SDRAM,即我们的内存,SDRAM的配置参数是按照我们板子上芯片的具体参数配置的,由于系统提供的SDRAM芯片跟我们不匹配,所以我们用custom手动配置

之后可以配置EPCS控制器啊,JTAG控制器,UART,PIO,sysid等相应IP

EPCS控制器是我们要控制控制片外的EPCS芯片用到的一个IP核,由于我们的CPU每次运行起来都是从内存,即SDRAM中读取数据的,而我们要做的就是将FPGA的硬件配置文件和我们的软件配置文件烧入到EPCS芯片中,这样CPU运行的时候就需要从EPCS芯片中将数据搬运到SDRAM中运行,从而提高运行速度,EPCS芯片控制器不需要配置,直接添加即可。

JTAG控制器是我们调试用的,包括我们将软件代码下载的时候,在窗口返回的一些数据就是通过JTAG口传回的,这个IP也不需要配置,直接添加即可

UART控制器即串口,为我们以后做串口调试实验做好硬件基础,这里大家可以手动配置波特率,和相应数据位

sysID说白了就是我们这个系统的标号,跟身份证差不多意思,即一个系统对应一个标号,标号我们可以随便取

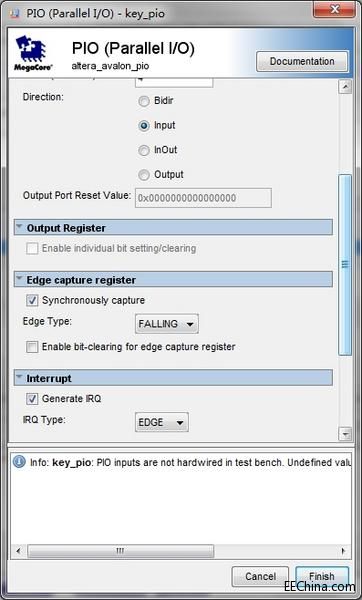

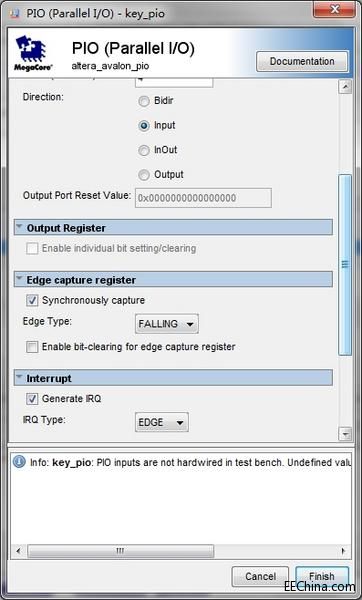

PIO外设即我们的IO口,分为输入输出,我们可以手动配置他们的输入输出,位宽等参数,输出没什么说的,说一下输入,输入我们主要是按键输入,我的开发板上是4位按键,所以位宽设为4,由于是按键输入,所以我们要检测的是按键的下降沿,而且是沿中断而不是电平中断,这里我们需要手动改一下。PIO外设我们可以随便加,包括什么数码管,蜂鸣器,键盘,led等

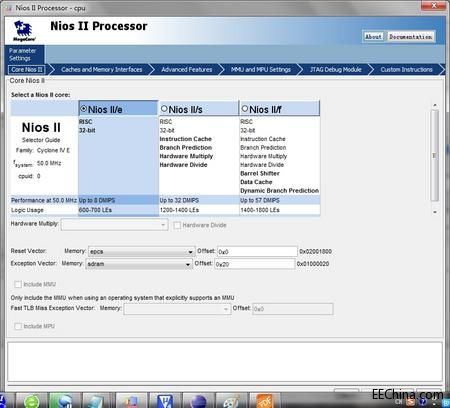

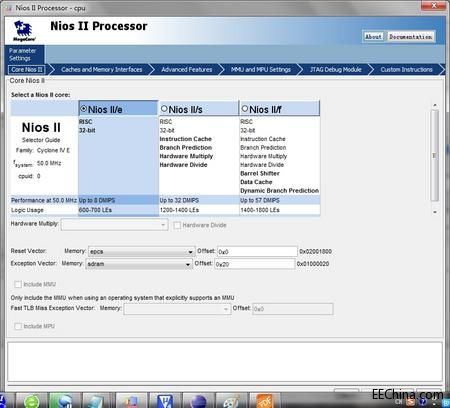

最后我们添加CPU,即我们的NIOS II 处理器,NIOS II处理器分为三种模式,即经济型,稳定型和快速型,当然越高端的类型所占的逻辑资源就越多,我们做一些小实验用经济型或者稳定型就够了

还有一点要注意,配置参数中的两个选项,Reset Vector——复位向量

Exception Vector——执行向量,我们分别选EPCS和SDRAM,即我们复位的时候,CPU从EPCS中将数据搬入SDRAM中重新执行,不复位的过程中,CPU从SDRAM中执行(这个地方可能理解的不对,望大神指点)

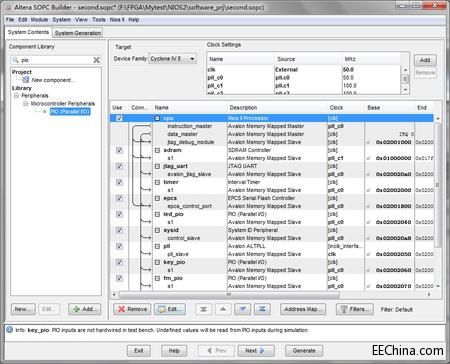

全部配置完成之后,我们需要对每一个IP核改下名字,右键,rename改成我们习惯的名字,不改的话后面总是跟着一些后缀。其实配置完成之后,系统就自动将这些模块连接好了,我们需要做的就是改一下时钟,让内部处理SDRAM控制器模块的其他IP用PLL模块输出的c0时钟,SDRAM控制器用c1时钟

接下来我们需要系统自动分配基地址和中断号,其实细心的朋友可能发现,在右面IRQ一栏下有些中断号是重复的,所以我们要系统重新分配一下中断优先级。点system——Assign base address 和 Assign interrupt numbers 即可,最后点下面的generate生成我们的系统即可

这样我们在sopc builder里的工作就完成了,硬件一旦生成,就不要轻易改了,剩下的事就是我们要在软件里折腾。

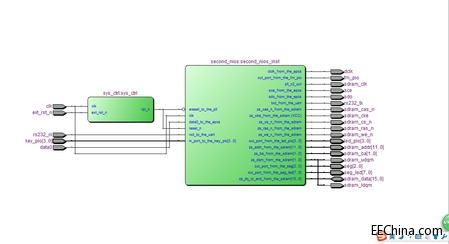

其实还可以这么理解,我们刚刚生成的系统就相当于一个集合了各种IP的模块,我们直接拿来调用即可。打开文件目录下后缀名为.inst的文件,就例化了我们刚才生成的系统,我们在quartus II顶层文件中调用这个系统,生成顶层模块,配置好管脚,这样我们的硬件部分才算是真的完成了

三、软件部分

硬件搞好了就要做软件,养成一个好的习惯,在工程目录中建立一个文件夹,专门放软件部分的文件

做软件,无非就是访问我们硬件系统中的寄存器,用C语言来控制,这里我们先简单做一个控制PIO核的小工程,通过控制PIO核来控制LED

软件方面的工程建立我不想多说,只想跟大家谈一下学习方法,当我们拿到一个外设,肯定要首先看一下他的datasheet,看他的寄存器映射图,拿PIO这个核来说,我们可以从网上下载n2cpu_nii5v3这个文件,里面详细介绍了各种IP核的资料

看datasheet 一般先看他的overview嘛,英文功底还是有的

然后我们需要看他的软件文件software files,即控制这个IP核需要的头文件,这里是altera_avalon_pio_regs.h

然后就是看寄存器视图了,寄存器视图告诉了我们如何具体操纵这个IP以及相应位的介绍

例如,第一个寄存器是数据寄存器,可以用来读写数据,只要我们知道这个PIO核的基址,再知道它的寄存器偏移我们就可以往数据寄存器里读写数据了,至于基址是多少,我们在定义硬件系统的时候系统已经自动生成,我们到时候只要调用就好了

再例如第二个寄存器是向量寄存器,即控制IO口的数据流方向,第三个寄存器是中断寄存器等等

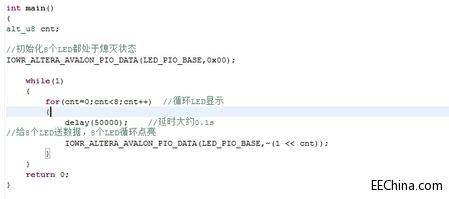

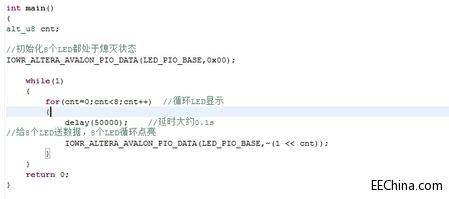

代码部分我们来看一下

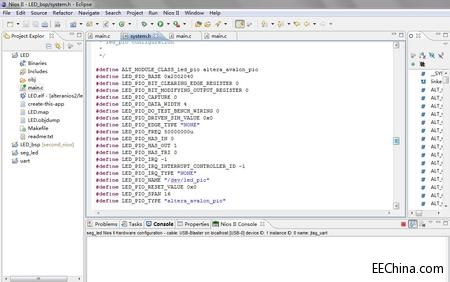

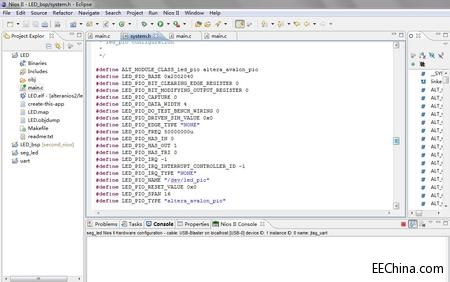

首先是初始化,我们调用函数找到我们PIO核的基址,并给我们的pio口赋初值0,至于PIO核的基址在头文件system.h中有定义

system .h中定义了我们硬件系统中所有IP的相关参数,我们可以直接拿来调用

初始化之后呢就进入while循环,循环移位就是我们所说的流水灯了。由于工程比较简单,按理说还需要调试,这里我们就不调试了,下板即可,先将我们的硬件下到板子了,即我们的SOF文件,然后再下我们的软件,右键我们的工程名,run as——NIOS II hardware

这篇文章主要是讲了硬件系统的搭建,其实硬件系统一搭建起来,我们以后的工程都可以用这个硬件系统,其实我自己也感觉这种用文字描述的方式来教大家做确实是不好理解,有些东西也不好用文字描述,上传的图片也是有限的,所以我中间也省了不少的步骤,包括一些常见错误的处理方法,工程文件的导入等,这些希望大家自己找资料了解,具体细节如果用文字描述起来更是繁琐,能看视频教学最好了。

下面的文章我们主要是在软件上折腾,包括定时器中断的使用啊,串口收发代码的讲解啊,还有自定义外设AD,DA芯片的控制啊,这些我们后续再谈吧~写了也不少了,暂时收工吧。

以后小墨同学的文章将在北京至芯科技官方技术论坛更新,至芯科技的官方技术论坛也有很多的资料供大家下载,里面也有小墨的专题板块,希望广大网友和爱好者的大力支持~

http://www.fpgaw.com/

小墨同学《零基础学FPGA》学习专版 一个大三学生学习之路的真实记录

http://www.fpgaw.com/thread-78527-1-1.html

下面是至芯科技官方网站,夏宇闻教授和那里的老师都超好的~有意愿接受FPGA培训的可以找工作人员咨询

http://www.zxopen.com/

以后小墨同学的教程会跟这款开发板配套,想跟小墨同学一起学习,一起进步的的可以考虑一下购买一块开发板,毕竟学习要舍得投资嘛,下面是开发板淘宝链接

http://item.taobao.com/item.htm? ... ;abbucket=13#detail

今天是来北京的第8天了,想想过的蛮快的,在这8天里呢,由于这边正在开SOPC的课程,自己对这方面之前只是了解过,知道有SOPC这回事,但是从来没有接触过,正好有这个机会让我蹭了几天的课,算是对这东西有了深入的了解吧。课程讲的很快,短短4天的功夫就从入门讲到了我认为比较难懂的方面,不过还好,经过我这几天的消化,之前也有点基础,理解一下还是没什么问题的,只不过让我去操作一个有点难度的外设的话,我估计还得下点功夫了~

讲SOPC的郝老师跟我住一个屋,郝老师人很不错,也很年轻,也是个90后,这几天跟着郝老师学到了不少东西,不仅仅是SOPC方面的,更多还有对工程师这个行业,对这个社会的一些新的认识。

由于我也是刚接触SOPC,不能像大神们讲的那么井井有条,思路严谨,我只是把我最近几天学到的东西跟大家分享一下,也作为自己的一份笔记。再下面的几篇文章中,我都会给大家发一些SOPC的笔记,从基本的概念,到基本硬件系统的搭建,一些常用IP核的应用,像什么PIO核,UART核,USB,EPCS控制器,SDRAM控制器等,还有后面的自定义外设等,估计用四五篇文章的长度来讲这部分吧。

学这一部分知识要软硬结合,硬件相信大家都没问题了,软件呢需要用到C语言的知识,由于我之前很久没用C语言了,如果大家对C语言还不是很熟的话,建议大家回去补一下C语言的课,虽然我们是搞硬件的,但是越到后面,软硬就不分了~

第一篇文章我就先来说说我理解中的SOPC,再教大家手把手搭建一个硬件平台,这个硬件平台搭建好了,我们以后的软件就全部是基于这个平台的编程了。

一、我理解中的SOPC

SOPC呢,也就是所谓的可编程片上系统,通常一个系统所包含的,什么CPU,存储器,DSP和一些IO外设等都放在FPGA的周围,这样大大增加的系统的面积从而增加了系统的成本,SOPC技术呢就是把CPU,DSP,定时器,IO模块都放到FPGA里面,通过Quartus II提供的SOPC builder这个工具,在里面嵌入NIOS II处理器和一些常用的IP 核,NIOS II处理器作为主机,其他外设作为从机,主机和从机之间通过AVALON MM总线进行通信与访问,每一个外设都有一个地址,NIOS II处理器可以通过这条总线对外设进行操作,但是每次只能访问一个外设,系统硬件搭建好了之后,通过Quartus II对其进行综合,布局布线,时序约束等硬件系统搭建工作,然后我们用C语言通过NIOS II eclipse 这个工具来给我们的硬件系统编程,并进行运行调试,最后将我们设计好的硬件与软件文件烧入FPGA的配置芯片或者FILASH中,通过相应的总线来控制相应的外设。下面是我画的一个关系图

下面我们就通过一个具体的实例来理解这个过程

二 、硬件系统搭建

上面这个图就是我们要搭建的硬件系统,硬件系统的搭建需要用到Quartus II软件 和它提供的SOPC builder 工具,一步步来,Quartus II建立工程就不说了,建立工程之后,tool ——sopc builder,按照上面的框图一个个添加我们需要的IP

首先我喜欢添加时钟,即PLL,直接在左上方的搜索框里输入PLL双击即可,至于PLL的配置方法我就不说了,相信大家都已经很熟了,由于我们的输入时钟是50M,我们需要的内部时钟主要用来控制各种IP,用50M的c0时钟,但是我们系统设计SDRAM,我们需要100M的c1时钟来控制SDRAM控制器,即SDRAM接口,同样还需要一个时钟输出到FPGA芯片外部来控制SDRAM芯片,我们用C2时钟,C2时钟跟C1时钟同频不同相,根据经验值,这个相位偏移我们选-75deg,频率100M

接着添加定时器,在搜索框输入timer 配置定时单位,位宽,这里我们设置为1ms,32位,在硬件选项对话框里一般选择 full—featured,当然也可以手动配置一些参数选custom

然后我们可以配置SDRAM,即我们的内存,SDRAM的配置参数是按照我们板子上芯片的具体参数配置的,由于系统提供的SDRAM芯片跟我们不匹配,所以我们用custom手动配置

之后可以配置EPCS控制器啊,JTAG控制器,UART,PIO,sysid等相应IP

EPCS控制器是我们要控制控制片外的EPCS芯片用到的一个IP核,由于我们的CPU每次运行起来都是从内存,即SDRAM中读取数据的,而我们要做的就是将FPGA的硬件配置文件和我们的软件配置文件烧入到EPCS芯片中,这样CPU运行的时候就需要从EPCS芯片中将数据搬运到SDRAM中运行,从而提高运行速度,EPCS芯片控制器不需要配置,直接添加即可。

JTAG控制器是我们调试用的,包括我们将软件代码下载的时候,在窗口返回的一些数据就是通过JTAG口传回的,这个IP也不需要配置,直接添加即可

UART控制器即串口,为我们以后做串口调试实验做好硬件基础,这里大家可以手动配置波特率,和相应数据位

sysID说白了就是我们这个系统的标号,跟身份证差不多意思,即一个系统对应一个标号,标号我们可以随便取

PIO外设即我们的IO口,分为输入输出,我们可以手动配置他们的输入输出,位宽等参数,输出没什么说的,说一下输入,输入我们主要是按键输入,我的开发板上是4位按键,所以位宽设为4,由于是按键输入,所以我们要检测的是按键的下降沿,而且是沿中断而不是电平中断,这里我们需要手动改一下。PIO外设我们可以随便加,包括什么数码管,蜂鸣器,键盘,led等

最后我们添加CPU,即我们的NIOS II 处理器,NIOS II处理器分为三种模式,即经济型,稳定型和快速型,当然越高端的类型所占的逻辑资源就越多,我们做一些小实验用经济型或者稳定型就够了

还有一点要注意,配置参数中的两个选项,Reset Vector——复位向量

Exception Vector——执行向量,我们分别选EPCS和SDRAM,即我们复位的时候,CPU从EPCS中将数据搬入SDRAM中重新执行,不复位的过程中,CPU从SDRAM中执行(这个地方可能理解的不对,望大神指点)

全部配置完成之后,我们需要对每一个IP核改下名字,右键,rename改成我们习惯的名字,不改的话后面总是跟着一些后缀。其实配置完成之后,系统就自动将这些模块连接好了,我们需要做的就是改一下时钟,让内部处理SDRAM控制器模块的其他IP用PLL模块输出的c0时钟,SDRAM控制器用c1时钟

接下来我们需要系统自动分配基地址和中断号,其实细心的朋友可能发现,在右面IRQ一栏下有些中断号是重复的,所以我们要系统重新分配一下中断优先级。点system——Assign base address 和 Assign interrupt numbers 即可,最后点下面的generate生成我们的系统即可

这样我们在sopc builder里的工作就完成了,硬件一旦生成,就不要轻易改了,剩下的事就是我们要在软件里折腾。

其实还可以这么理解,我们刚刚生成的系统就相当于一个集合了各种IP的模块,我们直接拿来调用即可。打开文件目录下后缀名为.inst的文件,就例化了我们刚才生成的系统,我们在quartus II顶层文件中调用这个系统,生成顶层模块,配置好管脚,这样我们的硬件部分才算是真的完成了

三、软件部分

硬件搞好了就要做软件,养成一个好的习惯,在工程目录中建立一个文件夹,专门放软件部分的文件

做软件,无非就是访问我们硬件系统中的寄存器,用C语言来控制,这里我们先简单做一个控制PIO核的小工程,通过控制PIO核来控制LED

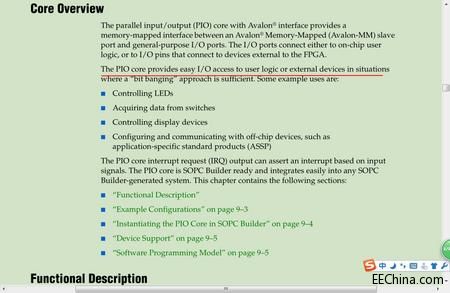

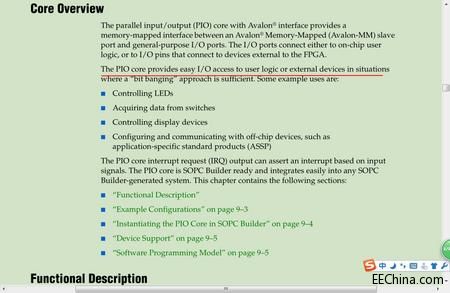

软件方面的工程建立我不想多说,只想跟大家谈一下学习方法,当我们拿到一个外设,肯定要首先看一下他的datasheet,看他的寄存器映射图,拿PIO这个核来说,我们可以从网上下载n2cpu_nii5v3这个文件,里面详细介绍了各种IP核的资料

看datasheet 一般先看他的overview嘛,英文功底还是有的

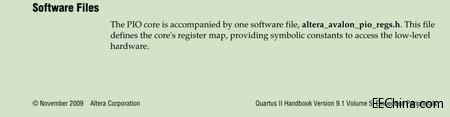

然后我们需要看他的软件文件software files,即控制这个IP核需要的头文件,这里是altera_avalon_pio_regs.h

然后就是看寄存器视图了,寄存器视图告诉了我们如何具体操纵这个IP以及相应位的介绍

例如,第一个寄存器是数据寄存器,可以用来读写数据,只要我们知道这个PIO核的基址,再知道它的寄存器偏移我们就可以往数据寄存器里读写数据了,至于基址是多少,我们在定义硬件系统的时候系统已经自动生成,我们到时候只要调用就好了

再例如第二个寄存器是向量寄存器,即控制IO口的数据流方向,第三个寄存器是中断寄存器等等

代码部分我们来看一下

首先是初始化,我们调用函数找到我们PIO核的基址,并给我们的pio口赋初值0,至于PIO核的基址在头文件system.h中有定义

system .h中定义了我们硬件系统中所有IP的相关参数,我们可以直接拿来调用

初始化之后呢就进入while循环,循环移位就是我们所说的流水灯了。由于工程比较简单,按理说还需要调试,这里我们就不调试了,下板即可,先将我们的硬件下到板子了,即我们的SOF文件,然后再下我们的软件,右键我们的工程名,run as——NIOS II hardware

这篇文章主要是讲了硬件系统的搭建,其实硬件系统一搭建起来,我们以后的工程都可以用这个硬件系统,其实我自己也感觉这种用文字描述的方式来教大家做确实是不好理解,有些东西也不好用文字描述,上传的图片也是有限的,所以我中间也省了不少的步骤,包括一些常见错误的处理方法,工程文件的导入等,这些希望大家自己找资料了解,具体细节如果用文字描述起来更是繁琐,能看视频教学最好了。

下面的文章我们主要是在软件上折腾,包括定时器中断的使用啊,串口收发代码的讲解啊,还有自定义外设AD,DA芯片的控制啊,这些我们后续再谈吧~写了也不少了,暂时收工吧。

以后小墨同学的文章将在北京至芯科技官方技术论坛更新,至芯科技的官方技术论坛也有很多的资料供大家下载,里面也有小墨的专题板块,希望广大网友和爱好者的大力支持~

http://www.fpgaw.com/

小墨同学《零基础学FPGA》学习专版 一个大三学生学习之路的真实记录

http://www.fpgaw.com/thread-78527-1-1.html

下面是至芯科技官方网站,夏宇闻教授和那里的老师都超好的~有意愿接受FPGA培训的可以找工作人员咨询

http://www.zxopen.com/

以后小墨同学的教程会跟这款开发板配套,想跟小墨同学一起学习,一起进步的的可以考虑一下购买一块开发板,毕竟学习要舍得投资嘛,下面是开发板淘宝链接

http://item.taobao.com/item.htm? ... ;abbucket=13#detail

USB C语言 DSP FPGA Quartus 总线 LED 相关文章:

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 我的FPGA学习历程(05-23)

- Virtex-5推动超宽带通信和测距的发展(01-06)

- Altera FPGA下载配置(11-11)

- 基于ARM9和CPLD的输入输出系统设计(04-09)

- 基于FPGA的高速图像采集系统设计(03-30)