利用FPGA对大规模MIMO信道进行特性描述

时间:01-12

来源:互联网

点击:

由24个FPGA、96个天线以及一个802.11定制模块构建的系统可对多用户MIMO传播环境进行实时分析。

作者:Patrick Murphy

Mango Communications公司总裁

patrick@mangocomm.com

Clayton Shepard

莱斯大学研究生

cws@rice.edu

Lin Zhong

莱斯大学副教授

lzhong@rice.edu

Chris Dick

赛灵思DSP首席科学家

chris.dick@xilinx.com

Ashutosh Sabharwal

莱斯大学教授

ashu@rice.edu

多用户MIMO(MUMIMO)是一种无线通信技术,采用基础架构节点(例如基站和接入点)上的多个天线为多个客户同时提供服务。MU-MIMO是未来无线标准中必不可少的组成部分,有望为繁忙的网络带来显著的性能提升。

人们预想随着无线系统的更新换代,基站的天线数量将会不断增加,最终形成“大规模MIMO”系统。大规模MIMO方案将MU-MIMO基站上的天线 数量增至数十个甚至数百个,以求在提高性能的同时简化基站的信号处理功能。有一种可扩展的大规模MIMO技术被称为共轭波束形成[1]。该技术的一种早期 实现方案显示出实际性能提升潜力[2]。

多用户MIMO技术离不开无线传输环境的准确信息。一个MUMIMO基础架构节点可同时服务多个用户,前提条件是具备有关每个用户无线信道的准确的最新测量信息。实时收集信道信息极具挑战性,而且陈旧或不准确的信道信息对性能影响可能非常严重。

我们设计出一款用于描述大规模MIMO信道特性的集成系统,可帮助研究人员实时分析信道的动态特性。该系统的核心部分采用基于赛灵思FPGA的 WARP硬件平台和Mango Communications的802.11参考设计,可通过莱斯大学(Rice University)的Argos平台将24个FPGA连接至96个天线[2]。Mango Communications开发的Python定制框架可用来实时控制和收集来自阵列中每个节点的数据。Mango和莱斯大学的这两款工具结合使用可提 供深入的无线协议栈信息,包括对大规模MIMO进行特性描述所需的原始信道数据。

Mango Communications802.11定制模块的重要功能是实时发送来自各个接收天线的底层基带参数,例如AGC增益、信道估计值和原始数据包内容 (甚至是含有错误的数据包)。参考设计的这项功能使莱斯大学的Argos阵列作为符合802.11标准的接入点(AP)使用,为商用Wi-Fi设备(例如 智能手机、平板电脑或笔记本电脑)提供互联网,同时实时收集阵列天线与每个客户端之间的信道数据。赛灵思FPGA是实现每个天线上的实时处理的关键。

它们将来自各个天线的数据简化成可由定制模块发送和分析的每客户端信道特性信息。

让我们来具体了解一下WARP硬件平台、Mango的802.11模块以及针对MU-MIMO的共轭波束形成策略。最后,我们还会检查特性分析过程,包括实时从Wi-Fi客户端收集无线信道测量数据,以及处理信道数据以估计可达到的MU-MIMO性能。系统组件

无线开放访问研究平台(WARP)是一款全新构建的可扩展、可编程无线平台,用于高级无线网络的原型设计。WARP能够将高性能可编程硬件与包含参考设计和支持资料的开放源码库结合在一起。

WARP项目于2006年由莱斯大学教授Ashu Sabharwal创立,最初由美国国家科学基金会(National Science Foundation)提供资金支持,目前由赛灵思持续提供支持。自此,该项目已经发展成为能够自我维持的开放源码平台,其用户遍布世界各地。Mango Communications于2008年从莱斯大学WARP项目中拆分出来,最初的目的是制造和销售莱斯WARP硬件。2012年,Mango发布了经 过彻底重新设计的WARP v3硬件。如今,Mango工程师是WARP资源库和论坛最活跃的贡献者,持续提供开发和开放源码WARP设计支持。

大规模MIMO信道测量系统的核心组成部分是Mango Communications的WARPv3硬件平台。WARP v3适用于快速、实时构建新型无线系统的原型设计。在硬件方面集成了一个赛灵思高性能Virtex®-6 FPGA,两个灵活的射频接口以及包括DDR3 DRAM和两个1Gbps以太网接口在内的多个外设。WARP v3板卡可通过Mango的双无线电FMC模块扩展至4个射频接口。图1中的硬件配置可提供具有FPGA独立数字基带连接的4个完全可编程的射频接口。

图1 – 具有双无线电FMC模块的WARP v3硬件可提供一个大FPGA、四个RF接口、存储器和两个以太网连接。

为了研究大规模MIMO系统,应该让多个WARPv3节点位于相同位置并共享电源、时钟和以太网连接。莱斯大学Argos项目能够满足这一要求。 Argos v2阵列包含24个四天线WARP v3节点,如图2所示。Argos阵列旨在支持各种大规模MIMO实验,而且特别适合同时收集所有96个阵列天线的信道测量数据。

图2 – 莱斯大学Argos v2阵列包含24个四无线电WARP v3节点,具备共享时钟和以太网连接。

这种实时处理能力对于我们的大规模MIMO信道特性描述设计来说非常重要,因为这样系统就可以不断地测量信道,并可靠地观测小于毫秒的信道特性变 化。执行该处理的FPGA定制设计正是针对WARP v3的Mango Communications 802.11参考设计。

该参考设计是802.11a/g介质访问控制层(MAC)和物理层(PHY)的实时FPGA实现方案。该设计用来与标准Wi-Fi设备进行交互操 作,起到接入点(用于Wi-Fi客户端)、客户端(访问Wi-Fi接入点)或者监控器(只能接收的网络活动无源观测器)的作用。您可以对MAC和PHY进 行定制,以探索从标准配置衍生出的变体方案。这种互操作性与可扩展性的完美结合能够实现各种规模的无线通信和网络实验。WARP v3硬件用户可免费获得802.11参考设计的完整源文件。

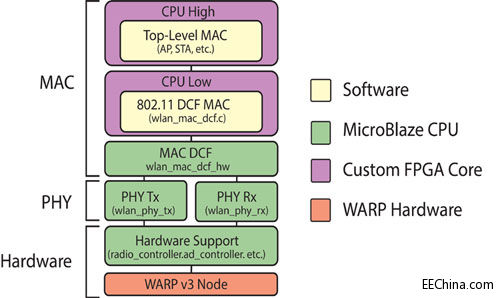

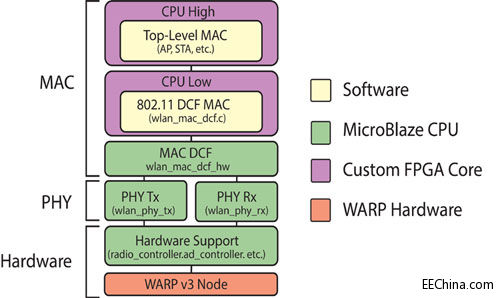

图3给出了参考设计架构。该设计使用两个赛灵思MicroBlaze™内核在软件中实现高电平和低电平MAC协议。MAC连接两个FPGA核,分别 用于实现PHY发送器和接收器。我们在赛灵思系统生成器中实现了这些PHY内核。发送器内核实现了完整的字节至波形流水线,可从MAC读取数据包有效载 荷,创建OFDM波形,并将波形驱动至射频接口DAC。该流水线包含编码、扰码、交织、IFFT和前同步码插入。MAC指定每个数据包的调制和编码速率; 支持802.11a/g规定的全部8种数据速率。

图3 – Mango 802.11参考设计架构包含两个用于MAC的赛灵思MicroBlazeCPU以及PHY发送器和接收器系统生成器定制内核。

接收器设计则实现了完整的波形至字节流水线,包括AGC、同步、FFT、信道估计、均衡、检测和解码。

Argos阵列中每个WARP v3节点上的FPGA都可提供接近射频接口的强大处理能力。在诸如Argos这样的大规模MIMO配置中,有大量数据需要处理。例如,当接收40MHz的 带宽时,WARP v3上的每个射频接口都会产生960Mbps的采样流(双12位40Msps的ADC)。完整Argos阵列的总量是该值的96倍,远远超出可发送到PC 和实时处理的最高值。相反,该系统能够利用FPGA实时对这些数据进行本地处理,并显著减少上游处理器的负担。

WARPnet框架针对我们的大规模MIMO信道特性描述设计,维持着与Argos阵列中每个节点的连接。每个节点都被配置为802.11监控器,可捕获来自每个接收数据包的信道估计值,并通过以太网下载这些数据包以备进一步分析。

WARPnet的完整Python源代码在WARP库中以开放源码方式提供。

作者:Patrick Murphy

Mango Communications公司总裁

patrick@mangocomm.com

Clayton Shepard

莱斯大学研究生

cws@rice.edu

Lin Zhong

莱斯大学副教授

lzhong@rice.edu

Chris Dick

赛灵思DSP首席科学家

chris.dick@xilinx.com

Ashutosh Sabharwal

莱斯大学教授

ashu@rice.edu

多用户MIMO(MUMIMO)是一种无线通信技术,采用基础架构节点(例如基站和接入点)上的多个天线为多个客户同时提供服务。MU-MIMO是未来无线标准中必不可少的组成部分,有望为繁忙的网络带来显著的性能提升。

人们预想随着无线系统的更新换代,基站的天线数量将会不断增加,最终形成“大规模MIMO”系统。大规模MIMO方案将MU-MIMO基站上的天线 数量增至数十个甚至数百个,以求在提高性能的同时简化基站的信号处理功能。有一种可扩展的大规模MIMO技术被称为共轭波束形成[1]。该技术的一种早期 实现方案显示出实际性能提升潜力[2]。

多用户MIMO技术离不开无线传输环境的准确信息。一个MUMIMO基础架构节点可同时服务多个用户,前提条件是具备有关每个用户无线信道的准确的最新测量信息。实时收集信道信息极具挑战性,而且陈旧或不准确的信道信息对性能影响可能非常严重。

我们设计出一款用于描述大规模MIMO信道特性的集成系统,可帮助研究人员实时分析信道的动态特性。该系统的核心部分采用基于赛灵思FPGA的 WARP硬件平台和Mango Communications的802.11参考设计,可通过莱斯大学(Rice University)的Argos平台将24个FPGA连接至96个天线[2]。Mango Communications开发的Python定制框架可用来实时控制和收集来自阵列中每个节点的数据。Mango和莱斯大学的这两款工具结合使用可提 供深入的无线协议栈信息,包括对大规模MIMO进行特性描述所需的原始信道数据。

Mango Communications802.11定制模块的重要功能是实时发送来自各个接收天线的底层基带参数,例如AGC增益、信道估计值和原始数据包内容 (甚至是含有错误的数据包)。参考设计的这项功能使莱斯大学的Argos阵列作为符合802.11标准的接入点(AP)使用,为商用Wi-Fi设备(例如 智能手机、平板电脑或笔记本电脑)提供互联网,同时实时收集阵列天线与每个客户端之间的信道数据。赛灵思FPGA是实现每个天线上的实时处理的关键。

它们将来自各个天线的数据简化成可由定制模块发送和分析的每客户端信道特性信息。

让我们来具体了解一下WARP硬件平台、Mango的802.11模块以及针对MU-MIMO的共轭波束形成策略。最后,我们还会检查特性分析过程,包括实时从Wi-Fi客户端收集无线信道测量数据,以及处理信道数据以估计可达到的MU-MIMO性能。系统组件

无线开放访问研究平台(WARP)是一款全新构建的可扩展、可编程无线平台,用于高级无线网络的原型设计。WARP能够将高性能可编程硬件与包含参考设计和支持资料的开放源码库结合在一起。

WARP项目于2006年由莱斯大学教授Ashu Sabharwal创立,最初由美国国家科学基金会(National Science Foundation)提供资金支持,目前由赛灵思持续提供支持。自此,该项目已经发展成为能够自我维持的开放源码平台,其用户遍布世界各地。Mango Communications于2008年从莱斯大学WARP项目中拆分出来,最初的目的是制造和销售莱斯WARP硬件。2012年,Mango发布了经 过彻底重新设计的WARP v3硬件。如今,Mango工程师是WARP资源库和论坛最活跃的贡献者,持续提供开发和开放源码WARP设计支持。

大规模MIMO信道测量系统的核心组成部分是Mango Communications的WARPv3硬件平台。WARP v3适用于快速、实时构建新型无线系统的原型设计。在硬件方面集成了一个赛灵思高性能Virtex®-6 FPGA,两个灵活的射频接口以及包括DDR3 DRAM和两个1Gbps以太网接口在内的多个外设。WARP v3板卡可通过Mango的双无线电FMC模块扩展至4个射频接口。图1中的硬件配置可提供具有FPGA独立数字基带连接的4个完全可编程的射频接口。

图1 – 具有双无线电FMC模块的WARP v3硬件可提供一个大FPGA、四个RF接口、存储器和两个以太网连接。

为了研究大规模MIMO系统,应该让多个WARPv3节点位于相同位置并共享电源、时钟和以太网连接。莱斯大学Argos项目能够满足这一要求。 Argos v2阵列包含24个四天线WARP v3节点,如图2所示。Argos阵列旨在支持各种大规模MIMO实验,而且特别适合同时收集所有96个阵列天线的信道测量数据。

图2 – 莱斯大学Argos v2阵列包含24个四无线电WARP v3节点,具备共享时钟和以太网连接。

这种实时处理能力对于我们的大规模MIMO信道特性描述设计来说非常重要,因为这样系统就可以不断地测量信道,并可靠地观测小于毫秒的信道特性变 化。执行该处理的FPGA定制设计正是针对WARP v3的Mango Communications 802.11参考设计。

该参考设计是802.11a/g介质访问控制层(MAC)和物理层(PHY)的实时FPGA实现方案。该设计用来与标准Wi-Fi设备进行交互操 作,起到接入点(用于Wi-Fi客户端)、客户端(访问Wi-Fi接入点)或者监控器(只能接收的网络活动无源观测器)的作用。您可以对MAC和PHY进 行定制,以探索从标准配置衍生出的变体方案。这种互操作性与可扩展性的完美结合能够实现各种规模的无线通信和网络实验。WARP v3硬件用户可免费获得802.11参考设计的完整源文件。

图3给出了参考设计架构。该设计使用两个赛灵思MicroBlaze™内核在软件中实现高电平和低电平MAC协议。MAC连接两个FPGA核,分别 用于实现PHY发送器和接收器。我们在赛灵思系统生成器中实现了这些PHY内核。发送器内核实现了完整的字节至波形流水线,可从MAC读取数据包有效载 荷,创建OFDM波形,并将波形驱动至射频接口DAC。该流水线包含编码、扰码、交织、IFFT和前同步码插入。MAC指定每个数据包的调制和编码速率; 支持802.11a/g规定的全部8种数据速率。

图3 – Mango 802.11参考设计架构包含两个用于MAC的赛灵思MicroBlazeCPU以及PHY发送器和接收器系统生成器定制内核。

接收器设计则实现了完整的波形至字节流水线,包括AGC、同步、FFT、信道估计、均衡、检测和解码。

Argos阵列中每个WARP v3节点上的FPGA都可提供接近射频接口的强大处理能力。在诸如Argos这样的大规模MIMO配置中,有大量数据需要处理。例如,当接收40MHz的 带宽时,WARP v3上的每个射频接口都会产生960Mbps的采样流(双12位40Msps的ADC)。完整Argos阵列的总量是该值的96倍,远远超出可发送到PC 和实时处理的最高值。相反,该系统能够利用FPGA实时对这些数据进行本地处理,并显著减少上游处理器的负担。

WARPnet框架针对我们的大规模MIMO信道特性描述设计,维持着与Argos阵列中每个节点的连接。每个节点都被配置为802.11监控器,可捕获来自每个接收数据包的信道估计值,并通过以太网下载这些数据包以备进一步分析。

WARPnet的完整Python源代码在WARP库中以开放源码方式提供。

FPGA 赛灵思 DSP 平板电脑 射频 无线电 DAC ADC 仿真 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)