采用可配置和组合逻辑设计的小器件也能实现大功能

时间:12-18

来源:互联网

点击:

如果您真的可以通过更少的器件实现更多功能,将会怎样?恩智浦可配置和组合逻辑器件使其成为可能——它为您提供各种方法来实现当今复杂系统中常见的“胶合”逻辑功能。

这些灵活、创新的单封装器件可让您可以配置或组合逻辑器件代替分立式逻辑解决方案,从而最终降低引脚数、器件数、系统成本和装配相关费用。因为需要处理的分立式逻辑器件数量更少,这些器件还能简化库存控制并降低认证开销。

什么是可配置逻辑?

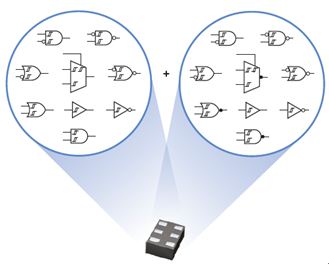

可配置逻辑可在单封装内实现9种或更多逻辑功能。以引脚配置方式决定此器件实现何种逻辑功能,因此仅使用单一器件便可实现多项系统所需的逻辑功能。

可配置逻辑 = 单个封装,九种或更多逻辑功能

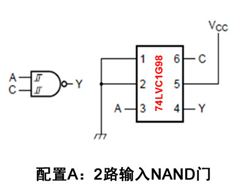

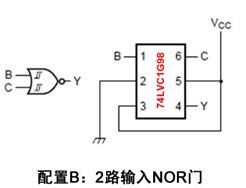

通过改变与GND、VCC(或选作器件I/O)相连的引脚,您可选择逻辑功能。以下图为例,使用74LVC1G98——一款低功耗多功能门,带施密特触发器输出。

利用可配置逻辑,则引脚配置可确定器件执行哪个逻辑功能

对于74LVC1G98而言,可用的两个功能是2路输入NAND门和2路输入NOR门。若要将74LVC1G98配置为NAND门,可选择引脚3和6作为输入、引脚4作为输出。引脚1和2连接GND,引脚5连接VCC(配置A)。若要将其作为NOR门使用,只需选择引脚1和6作为输入、引脚4作为输出。引脚2连接GND,而引脚3和5连接VCC(配置B)。74LVC1G98可代替库存中的全部2路输入NAND和2路输入NOR门,从而减少库存中必须认证和备货的元器件类型。此外,将多种器件功能归类到同一器件下可得到更高批量价位。

可配置逻辑的优势

从逻辑角度来说,可配置逻辑可降低库存成本,因为单个器件可设置为执行不同功能;还能简化器件认证,因为需认证的器件更少。恩智浦可配置逻辑解决方案还提供集成式电平转换选项,可节省电路板空间并降低系统成本,因为单个小型器件便可代替多个分立式元器件。

恩智浦可配置逻辑产品系列

恩智浦可配置逻辑产品涵盖九种基本功能,并提供这些功能的复杂变体选项。该系列包括2路输入AND、OR、NAND、NOR、XOR或XNOR门器件,加上逆变器、缓冲器和2:1多路复用器。另外,还提供集成电平转换的版本,用于混合电压系统,以及支持输出使能(EN)功能的版本。施密特触发器输入允许每个器件与较慢的转换输入实现接口,且所有器件均采用小尺寸、“深绿”封装,无卤无铅。

恩智浦可配置逻辑产品提供LVC和AUP系列,以及低压AXP逻辑系列,后者支持低至0.7 V的电压。

本文下一页:什么是组合逻辑?

什么是组合逻辑?

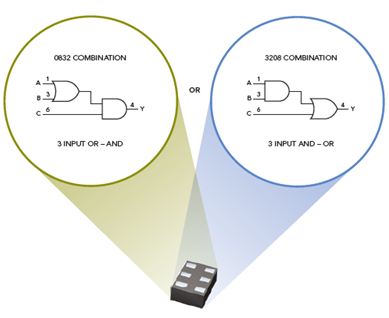

组合逻辑产品将两种或更多种不同功能集成于单封装中,让您能使用一个器件(而非多个分立式器件)执行一系列功能。这些功能可采取内部级联的方式,也可采取完全独立的方式存在。

组合逻辑 = 一个封装,两种或更多种不同功能

组合逻辑的优势

组合逻辑在具有不同逻辑功能(但互相之间很相似)的应用中优势尤为明显。它们在使用不同功能的标准组合应用中特别有用,比如手机输出级——OR门后接AND门。组合逻辑有助于快速完成此类逻辑功能的配置工作,并且能够改善信号性能,因为通过内部连接的信号可消除I/O缓冲器相关的延迟。在一个封装内集成两个或三个逻辑功能还能简化库存和制造,减少封装数,并降低引脚数和走线数量。

恩智浦组合逻辑产品系列

恩智浦组合逻辑提供低功耗AUP逻辑系列,具有单门、双门和三门等形式。

单门组合逻辑

单门器件在单个器件中集成两种不同功能。一个功能的输出通过芯片内部连接至第二个功能的输入。信号通过内部路由,因此无需I/O缓冲器,从而改善性能。此外还可降低器件引脚数,因为内部路由信号无需封装引脚,并共享电源和接地连接。

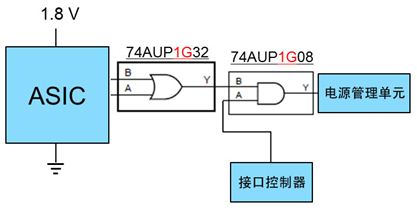

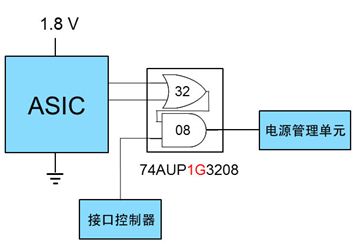

配置A:分立式逻辑解决方案

配置B:组合逻辑解决方案

此应用中,单门组合逻辑允许您使用单个器件,而非两个

双门组合逻辑

双门器件在单个器件内集成两个不同功能,但两个功能是完全独立的。这样可以节省需相邻排列的两个不同功能的系统空间。每个门的I/O信号在器件之外提供,但由于两个门共享电源和接地,因此引脚数依然低于分立式解决方案。

三门组合逻辑

三门器件在单个器件中集成三种不同功能。全部三个功能都是完全独立的,封装内不相连。由于引脚数的限制,三门器件仅可用作缓冲器或逆变器。

结论

如今,设计人员不断面对以更少的器件实现更多功能的要求。恩智浦可配置和组合逻辑解决方案通过降低系统成本、减少元器件数目和电路板走线数目,可轻松实现这一目标。这些器件还有助于限制器件认证所需的工程资源,并通过减少库存器件数达到简化库存管理、减少相关费用的目的。

- 主导闪存发展的关键技术(04-21)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)