主导闪存发展的关键技术

时间:04-21

来源:互联网

点击:

闪存几乎无处不在,特别是在移动设备中。闪存具有各种外形尺寸,随着成本的不断降低以及容量和工作寿命的不断增加,闪存不断地推动着越来越多的平台中硬盘驱动器的发展。

NAND和NOR闪存主导着固态非易失性存储器(NVM)市场,但是这些闪存并不是唯一可用的技术。不会明确地暴露闪存的外形尺寸是使用非闪存技术来替代的可能目标。比如,非闪存产品正在串行存储领域中暂露头角。

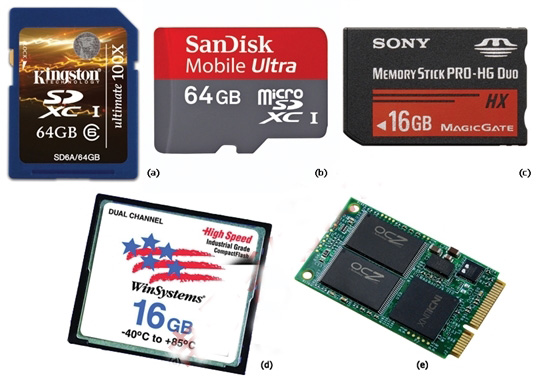

图1:闪存具有各种外形尺寸,包括SecureDigital(a)、MicroSD(b)、Sony记忆棒(c)、紧凑型闪存(d)和mSATA(e)。它们一般都采用NAND闪存

非易失性固态存储器

一方面是一次性可编程(OTP)存储器。现在,OTP存储器一般用来保存安全密钥或网络ID。它是采用诸如熔丝、反熔丝和浮栅等各种技术实现的。这种存储器还可以采用标准CMOS技术来实现。

带动NVM规模的是各种多次可编程(MTP)存储器技术,这类技术可以写入上百次甚至上千次。MTP存储器一般用来实现很少更改的启动代码。与OTP一样,MTP一般是采用CMOS技术实现的,这样就可以用在数字逻辑中。

浮栅EEPROM已经在数据存储中得到普遍的应用。由于具有写入单字节的能力、良好的耐力和数据保持能力,浮栅EEPROM已经相当流行,但是闪存技术在密度上远胜于浮栅EEPROM。EEPROM仿真常常被视为某些闪存实现方案的一种功能,它可以隐藏闪存的块擦除要求,以便能够写入单个字节。

其他的非易失性技术正在不断地提升闪存的优势,包括磁阻RAM(MRAM)、铁电RAM (FRAM)、相变存储器(PCM)以及前途无量的NVM技术。与NAND和NOR闪存等其他NVM技术相比,这些技术都具有更高的总体性能,包括写入速度、电压要求、缺少页面擦除周期、长期耐用性、数据保持能力和可扩展性。

这些技术开始是针对利基市场,在这种市场中,成本高一点并没有什么问题(至少在初期阶段是这样),其优势相当明显。它们甚至会引发SRAM与DRAM之间的激烈竞争。

德州仪器(TI)公司的16位MSP430FR57xx系列以其高达16 kB的用于数据存储和程序存储的FRAM而著称。该系列存储器具有代表性地融合了SRAM、闪存和EEPROM存储器。单个方案就可以降低库存单位(SKU)数,并简化开发人员的工作,使他们不再需要应付程序存储的RAM要求。

今后,这些可供选择的NVM技术将在更多的设计中得到应用。不过现在,闪存仍是主导的NVM技术。

闪存技术

闪存实现方案可以分成NAND和NOR方案,不同的供应商提供的方案各有不同。他们一般采用浮栅晶体管。这两种技术都表明了晶体管是如何连接和使用的,而不是将晶体管作为数字逻辑的一部分与FPGA或定制逻辑整合在一起。

NOR闪存晶体管接地和位线,这样就可以访问单个位。与NAND闪存相比,它具有更好的耐写性能。NOR闪存一般用在有代码和数据的应用中。带片上闪存的微控制器一般都会整合NOR闪存。

NAND闪存晶体管一般是成组连接至字线。这就可以实现比NOR闪存更高的密度。NAND闪存一般用于面向块的数据存储器。从晶体管的角度来看,NAND闪存不如NOR闪存可靠,因此NAND存储平台就需要使用错误检测和校正硬件或软件。NAND闪存一般用于高容量数据存储。

闪存使用擦写周期。擦除本质上是将闪存设置为1。写入则是将位设置为0,只要现有的1被改为0,就可以写入不同的数据。由于允许在没有长时间的耗电擦除周期的情况下执行操作,因此闪存文件系统可以充分利用这种特性。NAND闪存一般工作在块级别,而NOR可访问更加精细的级别。

闪存从单级单元(SLC)数据编码开始,每个存储晶体管对1或0进行编码。多级单元(MLC)闪存一般是指每单元存储2位(而不是1位)信息的能力。在晶体管级,所有的信息都是模拟的,不过与构建MLC闪存所需要的四级检测电路相比,构建一个两级检测电路更加简单。

同样,对MLC单元进行编程需要有产生四个不同级的能力。三级单元(TLC)闪存则更进了一步,这种闪存将3位或八级装入单个存储单元中,比如美光(Micron)公司的3位34nm NAND闪存芯片。

MLC或TLC存储器的明显优势是密度更高。其通常会在性能上作出折衷,尤其是耐写性能方面。

典型的SLC NAND闪存的可写次数为10万次,而SLC NOR闪存的可写次数为100万次。MLC闪存的可写次数则仅为上述次数的10分之一,TLC闪存的可写次数则更少。随着技术的进步,这些可写次数在不断地增加。SLC具有更好的耐写性能,而MLC和TLC的成本效益将更高。

闪存系统的使用寿命取决于多重因素,包括其托管方式。如果一个区域出现耗损时(即出现写入失败,无法保存正确的信息的情况时),非托管型闪存就会出现问题。错误检测系统有助于确定何时出现这种情况,不过一旦出现这种情况,设备一般也毫无用处了。更糟糕的是,其失效可能会导致相当多的问题。这也就是为什么带有内置闪存(无法跟踪耗损情况)的微控制器等器件依赖于可写次数较高的NOR闪存的原因。

有多种方法可以用来提高总系统寿命,比如耗损均衡。这种方法需要重新映射信息位置的能力。该方法对于面向块的器件最有效,尽管它可以应用到块大小的单个字中。实现耗损均衡会引起开销,因此块尺寸较大的话,效率就会更高。

耗损均衡可将写入操作分布在存储设备中。系统的使用寿命可以视为系统的总写入容量,而不是单个块的最大值。耗损均衡需要跟踪块写入使用情况以及记录和利用该信息的能力。如果出现缺陷的话,块的使用寿命往往会缩短至不到其建议的写入寿命。

在这种情况下,如果存储器被超额配置的话,则可以使用重新映射机制。额外的块或扇区在硬盘驱动器上很常见,对闪存可以采用同样的方法。唯一的区别是,如果在规则的块中检测到不可校正的错误,那么就会使用额外的块。

使用耗损均衡之后,所有的块往往就都是存储池的一部分。如果系统是以软件方式实现的,也可以根据系统所需的使用寿命来选择逻辑设备尺寸。逻辑尺寸越小,出现的“额外”块越多。

像FRAM、MRAM和PCM等其他一些技术不会出现与闪存一样的耐写能力问题。但是仍然可以使用诸如存储器过度配置和重新映射等技术,特别是在硬件缺陷等其他错误可能比较常见的大型设备中。

NAND和NOR闪存主导着固态非易失性存储器(NVM)市场,但是这些闪存并不是唯一可用的技术。不会明确地暴露闪存的外形尺寸是使用非闪存技术来替代的可能目标。比如,非闪存产品正在串行存储领域中暂露头角。

图1:闪存具有各种外形尺寸,包括SecureDigital(a)、MicroSD(b)、Sony记忆棒(c)、紧凑型闪存(d)和mSATA(e)。它们一般都采用NAND闪存

非易失性固态存储器

一方面是一次性可编程(OTP)存储器。现在,OTP存储器一般用来保存安全密钥或网络ID。它是采用诸如熔丝、反熔丝和浮栅等各种技术实现的。这种存储器还可以采用标准CMOS技术来实现。

带动NVM规模的是各种多次可编程(MTP)存储器技术,这类技术可以写入上百次甚至上千次。MTP存储器一般用来实现很少更改的启动代码。与OTP一样,MTP一般是采用CMOS技术实现的,这样就可以用在数字逻辑中。

浮栅EEPROM已经在数据存储中得到普遍的应用。由于具有写入单字节的能力、良好的耐力和数据保持能力,浮栅EEPROM已经相当流行,但是闪存技术在密度上远胜于浮栅EEPROM。EEPROM仿真常常被视为某些闪存实现方案的一种功能,它可以隐藏闪存的块擦除要求,以便能够写入单个字节。

其他的非易失性技术正在不断地提升闪存的优势,包括磁阻RAM(MRAM)、铁电RAM (FRAM)、相变存储器(PCM)以及前途无量的NVM技术。与NAND和NOR闪存等其他NVM技术相比,这些技术都具有更高的总体性能,包括写入速度、电压要求、缺少页面擦除周期、长期耐用性、数据保持能力和可扩展性。

这些技术开始是针对利基市场,在这种市场中,成本高一点并没有什么问题(至少在初期阶段是这样),其优势相当明显。它们甚至会引发SRAM与DRAM之间的激烈竞争。

德州仪器(TI)公司的16位MSP430FR57xx系列以其高达16 kB的用于数据存储和程序存储的FRAM而著称。该系列存储器具有代表性地融合了SRAM、闪存和EEPROM存储器。单个方案就可以降低库存单位(SKU)数,并简化开发人员的工作,使他们不再需要应付程序存储的RAM要求。

今后,这些可供选择的NVM技术将在更多的设计中得到应用。不过现在,闪存仍是主导的NVM技术。

闪存技术

闪存实现方案可以分成NAND和NOR方案,不同的供应商提供的方案各有不同。他们一般采用浮栅晶体管。这两种技术都表明了晶体管是如何连接和使用的,而不是将晶体管作为数字逻辑的一部分与FPGA或定制逻辑整合在一起。

NOR闪存晶体管接地和位线,这样就可以访问单个位。与NAND闪存相比,它具有更好的耐写性能。NOR闪存一般用在有代码和数据的应用中。带片上闪存的微控制器一般都会整合NOR闪存。

NAND闪存晶体管一般是成组连接至字线。这就可以实现比NOR闪存更高的密度。NAND闪存一般用于面向块的数据存储器。从晶体管的角度来看,NAND闪存不如NOR闪存可靠,因此NAND存储平台就需要使用错误检测和校正硬件或软件。NAND闪存一般用于高容量数据存储。

闪存使用擦写周期。擦除本质上是将闪存设置为1。写入则是将位设置为0,只要现有的1被改为0,就可以写入不同的数据。由于允许在没有长时间的耗电擦除周期的情况下执行操作,因此闪存文件系统可以充分利用这种特性。NAND闪存一般工作在块级别,而NOR可访问更加精细的级别。

闪存从单级单元(SLC)数据编码开始,每个存储晶体管对1或0进行编码。多级单元(MLC)闪存一般是指每单元存储2位(而不是1位)信息的能力。在晶体管级,所有的信息都是模拟的,不过与构建MLC闪存所需要的四级检测电路相比,构建一个两级检测电路更加简单。

同样,对MLC单元进行编程需要有产生四个不同级的能力。三级单元(TLC)闪存则更进了一步,这种闪存将3位或八级装入单个存储单元中,比如美光(Micron)公司的3位34nm NAND闪存芯片。

MLC或TLC存储器的明显优势是密度更高。其通常会在性能上作出折衷,尤其是耐写性能方面。

典型的SLC NAND闪存的可写次数为10万次,而SLC NOR闪存的可写次数为100万次。MLC闪存的可写次数则仅为上述次数的10分之一,TLC闪存的可写次数则更少。随着技术的进步,这些可写次数在不断地增加。SLC具有更好的耐写性能,而MLC和TLC的成本效益将更高。

闪存系统的使用寿命取决于多重因素,包括其托管方式。如果一个区域出现耗损时(即出现写入失败,无法保存正确的信息的情况时),非托管型闪存就会出现问题。错误检测系统有助于确定何时出现这种情况,不过一旦出现这种情况,设备一般也毫无用处了。更糟糕的是,其失效可能会导致相当多的问题。这也就是为什么带有内置闪存(无法跟踪耗损情况)的微控制器等器件依赖于可写次数较高的NOR闪存的原因。

有多种方法可以用来提高总系统寿命,比如耗损均衡。这种方法需要重新映射信息位置的能力。该方法对于面向块的器件最有效,尽管它可以应用到块大小的单个字中。实现耗损均衡会引起开销,因此块尺寸较大的话,效率就会更高。

耗损均衡可将写入操作分布在存储设备中。系统的使用寿命可以视为系统的总写入容量,而不是单个块的最大值。耗损均衡需要跟踪块写入使用情况以及记录和利用该信息的能力。如果出现缺陷的话,块的使用寿命往往会缩短至不到其建议的写入寿命。

在这种情况下,如果存储器被超额配置的话,则可以使用重新映射机制。额外的块或扇区在硬盘驱动器上很常见,对闪存可以采用同样的方法。唯一的区别是,如果在规则的块中检测到不可校正的错误,那么就会使用额外的块。

使用耗损均衡之后,所有的块往往就都是存储池的一部分。如果系统是以软件方式实现的,也可以根据系统所需的使用寿命来选择逻辑设备尺寸。逻辑尺寸越小,出现的“额外”块越多。

像FRAM、MRAM和PCM等其他一些技术不会出现与闪存一样的耐写能力问题。但是仍然可以使用诸如存储器过度配置和重新映射等技术,特别是在硬件缺陷等其他错误可能比较常见的大型设备中。

CMOS 仿真 电压 德州仪器 MSP430 FPGA 电路 恩智浦 半导体 NXP 传感器 嵌入式 USB 总线 连接器 电容 电子 相关文章:

- 适用于消费性市场的nano FPGA技术(09-27)

- Virtex-5推动超宽带通信和测距的发展(01-06)

- FPGA中嵌入式存储器模块的设计(03-28)

- 基于FPGA的高速图像采集系统设计(03-30)

- 利用FPGA和CPLD数字逻辑实现ADC(06-04)

- FPGA控制CLC5958型A/D转换器高速PCI采集(06-08)