FPGA研发之道(22)-交换矩阵

时间:12-09

来源:互联网

点击:

作者:阿昏豆

如果在FPGA设计中,需要多端口,大数据量的交换,那么交换矩阵则是一个不错的实现方案。交换矩阵使用的目的主要有几个,一,灵活的端口转发。通过交换矩阵灵活实现数据流的灵活交换,减少外部负责控制。 二,高效的转发效率,交换矩阵能够实现通常单一总线不能达到的转发效率,满足高吞吐量的系统的需要。三,系统设计以交换矩阵为中心,便于IP集成和模块复用。

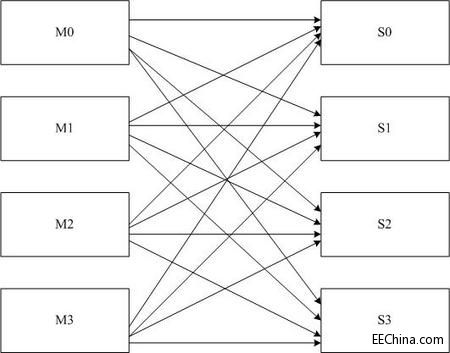

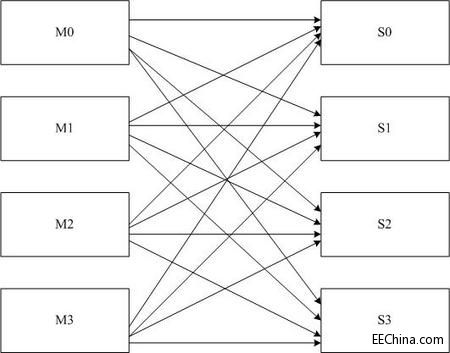

交换矩阵的实现方案较为复杂,最早的交换沿袭了共享总线式的架构,因此对于某个端口需要传输,则其他端口只能阻塞,等待总线空闲后再进行传输。而交换矩阵则是一个全互联的结构。如下图所示,如有4个输入,4个输出的交换矩阵,可认为是一个4端口的交换单元,每个端口包含一个发送接口和一个接收模块,如端口0就包含发送模块m0和接收模块s0。

假设每路传输的速率为N,则整个交换矩阵的传输速率为4N。如何实现一个简单的交换矩阵。首先可以将整速率个设计分割。将整个设计分割为接受和发送两个模块。整个交换单元可以划分为四个部分,分别是,发送模块,仲裁模块,交换模块,接收模块。

(1) 发送模块,首先根据某端口接收数据后,根据该数据帧要转发的端口,发起请求信号。

(2) 仲裁模块:根据请求信号,接收模块的忙闲状态,及各发送模块的优先级,确定当前的响应信号,如果当前的接收模块忙(上次传输未完成),则需要阻塞,等待上次传输完成(复杂的设计,可以保证高优先级能够打断当前传输,直接传输高优先级数据流,高优先级完成后,再恢复原有传输,但这种方式设计较为复杂,仿真验证的难度也较大,不建议使用)。

(3) 交换模块:根据仲裁信号确定发送模块转发的端口,交换模块本质上是多选一的MUX,而MUX的选择信号,则是由仲裁模块来进行选择。

(4) 接收模块:接收交换模块交换后的数据流,向仲裁模块返回当前模块的忙闲状态(正在接收传输信号,为忙状态,而当前无传输状态,则为闲状态)。

仲裁模块的仲裁机制,一般可以使用简单的round-robin的设计,即轮流最高优先级。也可以通过设计带加权的优先级,保证更高优先级的端口优先进行传输。

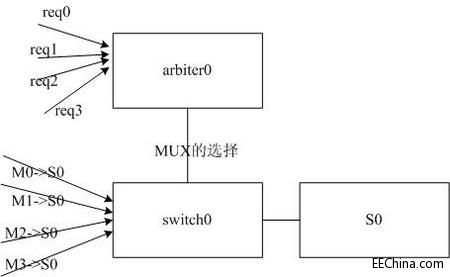

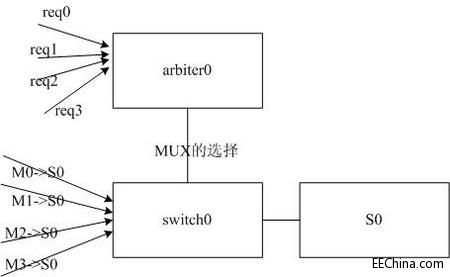

仲裁模块的仲裁设计可以分为多种,一种是整个交换矩阵使用同一个仲裁单元,每个发送模块只使用一个请求信号及请求端口号连接到仲裁模块。这种设计对整个仲裁模块设计难度较大。另一种设计,如下图所示,即每个接收单元,配置一个仲裁模块,和一个交换模块。而每个发送模块根据要发送的端口,使用多个发送的请求信号。此种设计便于系统扩展,也可简化设计。

不仅是用于高速多端口转发的数据流传输采用交换矩阵。现在,大多高速总线机制(如N主设备,M从设备之间进行数据的交换)也采用类似交换矩阵式的结构,每个从设备的连接都是多个主设备通过MUX来进行连接,这样保证多个主设备访问不同从设备时,可以实现并行的数据交换(如主设备M0访问从设备S1,主设备M1访问从设备S2,可以同时进行总线操作)。这是单一竞争式总线所不能达到的优势,但是,设计占用的逻辑量也会增加。性能的增加带来的负面影响通常就是逻辑的增加。

交换矩阵通常在基于数据包转发的FPGA设计应用中,交换矩阵的交换灵活性增加,也会增加设计复杂度,如果对于传输效率不需太多的需求,可以采用系统复用的方式(前文介绍),通过一个复用模块轮流接收各个发送端口的数据流,,再根据端口转发到各个从设备中,此种方式设计简单,但是此复用模块则会成为系统的瓶颈。根据系统的设计需求,选择适合的设计,达到性能和逻辑方面的平衡,是体现FPGA设计艺术之一。

如果在FPGA设计中,需要多端口,大数据量的交换,那么交换矩阵则是一个不错的实现方案。交换矩阵使用的目的主要有几个,一,灵活的端口转发。通过交换矩阵灵活实现数据流的灵活交换,减少外部负责控制。 二,高效的转发效率,交换矩阵能够实现通常单一总线不能达到的转发效率,满足高吞吐量的系统的需要。三,系统设计以交换矩阵为中心,便于IP集成和模块复用。

交换矩阵的实现方案较为复杂,最早的交换沿袭了共享总线式的架构,因此对于某个端口需要传输,则其他端口只能阻塞,等待总线空闲后再进行传输。而交换矩阵则是一个全互联的结构。如下图所示,如有4个输入,4个输出的交换矩阵,可认为是一个4端口的交换单元,每个端口包含一个发送接口和一个接收模块,如端口0就包含发送模块m0和接收模块s0。

假设每路传输的速率为N,则整个交换矩阵的传输速率为4N。如何实现一个简单的交换矩阵。首先可以将整速率个设计分割。将整个设计分割为接受和发送两个模块。整个交换单元可以划分为四个部分,分别是,发送模块,仲裁模块,交换模块,接收模块。

(1) 发送模块,首先根据某端口接收数据后,根据该数据帧要转发的端口,发起请求信号。

(2) 仲裁模块:根据请求信号,接收模块的忙闲状态,及各发送模块的优先级,确定当前的响应信号,如果当前的接收模块忙(上次传输未完成),则需要阻塞,等待上次传输完成(复杂的设计,可以保证高优先级能够打断当前传输,直接传输高优先级数据流,高优先级完成后,再恢复原有传输,但这种方式设计较为复杂,仿真验证的难度也较大,不建议使用)。

(3) 交换模块:根据仲裁信号确定发送模块转发的端口,交换模块本质上是多选一的MUX,而MUX的选择信号,则是由仲裁模块来进行选择。

(4) 接收模块:接收交换模块交换后的数据流,向仲裁模块返回当前模块的忙闲状态(正在接收传输信号,为忙状态,而当前无传输状态,则为闲状态)。

仲裁模块的仲裁机制,一般可以使用简单的round-robin的设计,即轮流最高优先级。也可以通过设计带加权的优先级,保证更高优先级的端口优先进行传输。

仲裁模块的仲裁设计可以分为多种,一种是整个交换矩阵使用同一个仲裁单元,每个发送模块只使用一个请求信号及请求端口号连接到仲裁模块。这种设计对整个仲裁模块设计难度较大。另一种设计,如下图所示,即每个接收单元,配置一个仲裁模块,和一个交换模块。而每个发送模块根据要发送的端口,使用多个发送的请求信号。此种设计便于系统扩展,也可简化设计。

不仅是用于高速多端口转发的数据流传输采用交换矩阵。现在,大多高速总线机制(如N主设备,M从设备之间进行数据的交换)也采用类似交换矩阵式的结构,每个从设备的连接都是多个主设备通过MUX来进行连接,这样保证多个主设备访问不同从设备时,可以实现并行的数据交换(如主设备M0访问从设备S1,主设备M1访问从设备S2,可以同时进行总线操作)。这是单一竞争式总线所不能达到的优势,但是,设计占用的逻辑量也会增加。性能的增加带来的负面影响通常就是逻辑的增加。

交换矩阵通常在基于数据包转发的FPGA设计应用中,交换矩阵的交换灵活性增加,也会增加设计复杂度,如果对于传输效率不需太多的需求,可以采用系统复用的方式(前文介绍),通过一个复用模块轮流接收各个发送端口的数据流,,再根据端口转发到各个从设备中,此种方式设计简单,但是此复用模块则会成为系统的瓶颈。根据系统的设计需求,选择适合的设计,达到性能和逻辑方面的平衡,是体现FPGA设计艺术之一。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)