FPGA研发之道(12)-设计不是凑波形(二)FIFO(下)

时间:12-04

来源:互联网

点击:

作者:阿昏豆

FIFO在FPGA设计中除了上篇所介绍的功能之外, 还有以下作为以下功能使用:

(1) 内存申请

在软件设计中,使用malloc()和free()等函数可以用于内存的申请和释放。特别是在有操作系统的环境下,可以保证系统的内存空间被动态的分配和使用,非常的方便。如果在FPGA内部实现此动态的内存分配和申请,相对来说较为复杂,例如某些需要外部数据存储且需动态改变的应用需求下,需要对FPGA外部DDR(或SRAM等)的存储空间,进行动态的分配和释放。通过使用FIFO作为内存分配器,虽然比不上软件的灵活和方便,但是使用也较为简便。

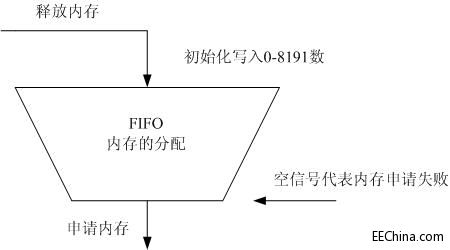

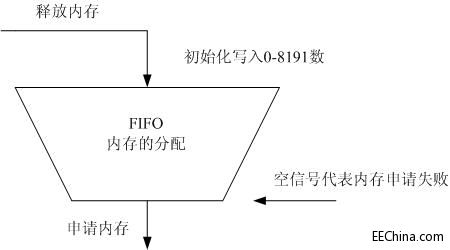

举例说明假设外部存储空间为8Mbyte,可将其划分为8192个1Kbyte空间。并将数值0-8191存储FIFO中,FIFO内部存储所标示可用的内存空间。如下图所示。

首先,进行内存的初始化,即将0-8191写入FIFO中。

如需申请内存后,从FIFO中读取值A,然后根据A的标示,写入A所指示的外部存储区(DDR)中相应的位置,即申请{A,10’h0_00} ->{A,10’h3_FF}的空间区域。

如释放内存后,即可向FIFO中写入相应的值。即可保证下次该空间能够被设计使用。

在此种设计中,FIFO承担了内存分配和释放器的角色。此时只能申请或释放最小单元倍数的内存空间,如本例所示:为1Kbit。如FIFO读空,则代表申请内存失败,需要等待其他块内存释放后再写入FIFO中,才能再次申请。

(2) 串并转换

对于串并转换,可能对于FPGA工程师来说,非常常见,但是如果有专门的IP实现此功能,可简化设计,减少出错及验证的工作量。例如:对于外部输入的需要进行串并转换的信号,并进行存储的信号,如设计进行串并转换在存储等操作,设计,可以直接通过例化读写位宽不一致的FIFO,例如1入8出的FIFO,可直接将外部输入信号直接转换成8BIT信号并进行存储后,供后续处理使用(其他的)。

(3) 业务优先级划分

通过FIFO设置不同水位线,可以划分不同的业务优先级,保证高业务优先级数据流在带宽受限时,优先通过,而低业务优先级只能在满足高优先级需求后有多余的带宽时才能通过。并且可以划分多个优先级,满足多种业务的需求。设计将在以后篇幅中详述。

(4)固定带宽设定

通过对FIFO接口的读出使能,能够保证实现固定带宽的输出,例如FIFO读接口为32bit,而读时钟为50Mhz,则输出为1.6Gbit/S。如实现固定带宽的输出(如1Gbit/S),有两种方式,一种可以通过降低时钟频率到31.25Mhz。另一种方式,可通过读信号中间插入等待周期,如果读出长度为N的数据所需时钟周期为M,则需等待(3M/5)的周期,从而降低至1Gbit/S的处理能力,这在某些需要进行流量限制的业务方式中使用。

对于FIFO来说,作为FPGA内部资源的一个常用器件,最常见应用于异步时钟域划分和缓冲数据,但不仅限于此,简化设计、减少耦合、输入输出接口固定,便于仿真和验证,都是使用FIFO带来的设计上的益处。

FIFO在FPGA设计中除了上篇所介绍的功能之外, 还有以下作为以下功能使用:

(1) 内存申请

在软件设计中,使用malloc()和free()等函数可以用于内存的申请和释放。特别是在有操作系统的环境下,可以保证系统的内存空间被动态的分配和使用,非常的方便。如果在FPGA内部实现此动态的内存分配和申请,相对来说较为复杂,例如某些需要外部数据存储且需动态改变的应用需求下,需要对FPGA外部DDR(或SRAM等)的存储空间,进行动态的分配和释放。通过使用FIFO作为内存分配器,虽然比不上软件的灵活和方便,但是使用也较为简便。

举例说明假设外部存储空间为8Mbyte,可将其划分为8192个1Kbyte空间。并将数值0-8191存储FIFO中,FIFO内部存储所标示可用的内存空间。如下图所示。

首先,进行内存的初始化,即将0-8191写入FIFO中。

如需申请内存后,从FIFO中读取值A,然后根据A的标示,写入A所指示的外部存储区(DDR)中相应的位置,即申请{A,10’h0_00} ->{A,10’h3_FF}的空间区域。

如释放内存后,即可向FIFO中写入相应的值。即可保证下次该空间能够被设计使用。

在此种设计中,FIFO承担了内存分配和释放器的角色。此时只能申请或释放最小单元倍数的内存空间,如本例所示:为1Kbit。如FIFO读空,则代表申请内存失败,需要等待其他块内存释放后再写入FIFO中,才能再次申请。

(2) 串并转换

对于串并转换,可能对于FPGA工程师来说,非常常见,但是如果有专门的IP实现此功能,可简化设计,减少出错及验证的工作量。例如:对于外部输入的需要进行串并转换的信号,并进行存储的信号,如设计进行串并转换在存储等操作,设计,可以直接通过例化读写位宽不一致的FIFO,例如1入8出的FIFO,可直接将外部输入信号直接转换成8BIT信号并进行存储后,供后续处理使用(其他的)。

(3) 业务优先级划分

通过FIFO设置不同水位线,可以划分不同的业务优先级,保证高业务优先级数据流在带宽受限时,优先通过,而低业务优先级只能在满足高优先级需求后有多余的带宽时才能通过。并且可以划分多个优先级,满足多种业务的需求。设计将在以后篇幅中详述。

(4)固定带宽设定

通过对FIFO接口的读出使能,能够保证实现固定带宽的输出,例如FIFO读接口为32bit,而读时钟为50Mhz,则输出为1.6Gbit/S。如实现固定带宽的输出(如1Gbit/S),有两种方式,一种可以通过降低时钟频率到31.25Mhz。另一种方式,可通过读信号中间插入等待周期,如果读出长度为N的数据所需时钟周期为M,则需等待(3M/5)的周期,从而降低至1Gbit/S的处理能力,这在某些需要进行流量限制的业务方式中使用。

对于FIFO来说,作为FPGA内部资源的一个常用器件,最常见应用于异步时钟域划分和缓冲数据,但不仅限于此,简化设计、减少耦合、输入输出接口固定,便于仿真和验证,都是使用FIFO带来的设计上的益处。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)