FPGA研发之道(13)-设计不是凑波形(三)RAM

时间:12-04

来源:互联网

点击:

作者:阿昏豆

在FPGA内部资源中,RAM是较为常用的一种资源。

通常实例化RAM中,一种使用为BLOCK RAM 也就是块RAM 。另外资源可以通过寄存器搭,也就是分布式RAM。前者一般用于提供较大的存储空间,后者则提供小的存储空间。

在实际应用过程中,一般使用的包括,单端口、双端口RAM,ROM等形式等不同的形式。 实际应用中FIFO也是利用RAM和逻辑一起实现的。

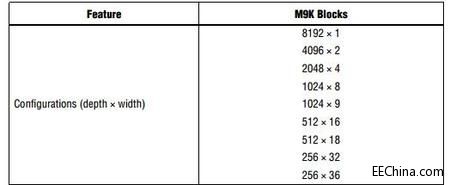

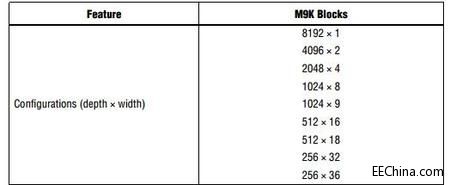

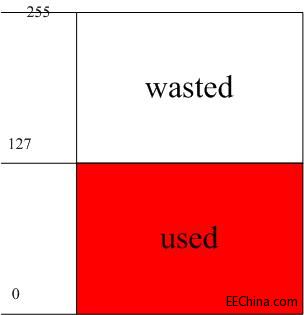

对于一块RAM中,其能够例化的深度是有限的。例如cyclone4的RAM9k中可以例化的资源如下所示:

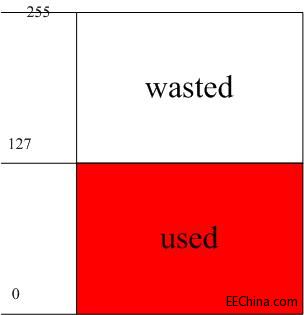

因此:例化化深度<256的RAM,其同样也需要占用一块BLOCKRAM的资源,例如例化宽度为64 深度为128的RAM,其资源为8K 。但是仍然需要占用两块BOCK RAM。也就是说,只要例化RAM深度少于256.则对于本器件9K来说,剩下的资源也是浪费。

那是不是可以例化成双端口RAM,通过高位地址区分,变为两个单端口RAM(width:32,depth:128)来使用,这样就可以节省资源了?

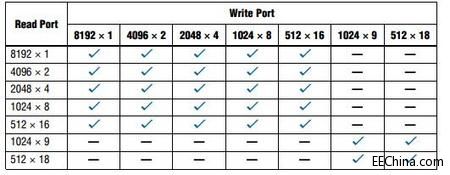

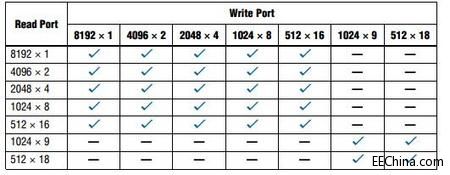

而对于双端口RAM来说,每个M9K能够配置是的最小深度就变成是512,而最大宽度为18,如下图所示,因此作为真双端口RAM使用,深度小于512的话,仍然会占用1块RAM。且宽度》18就会多占用额外的一块RAM,因此上述的节省资源的方式是不正确的。

通过查看datasheet的中RAM能够配置的方式,从而能够正确的使用RAM资源,从而达到高的利用效率。可以看出,RAM9K其应用方式受限,主要是因为RAM的端口的连接信号受限,例如:该RAM9K的读端口最大支持36根信号线,因此对于单端口其支持的宽度为36,双端口为18(两个端口,总共36根数据线),作为FPGA来说,其布线资源是有限的,不可能无限制的增加其端口数。

RAM例化时,有时需要初始化RAM,ALTERA和XLINX的初始化方法如下所示:

(1)ALTERA RAM中,例化时为MIF文件,其格式为:

DEPTH = 32; -- The size of memory in words

WIDTH = 8; -- The size of data in bits

ADDRESS_RADIX = HEX; -- The radix for address values

DATA_RADIX = HEX; -- The radix for data values

CONTENT -- start of (address : data pairs)

BEGIN

00 : 0; -- memory address : data

01 : 1;

END;

(2)在XILINX的RAM中,RAM出示化文件为COE文件,其格式为:

MEMORY_INITIALIZATION_RADIX=2; 设定进制

MEMORY_INITIALIZATION_VECTOR= 初始化向量

值得注意的是:XILINX的RAM初始化后会自动生成MIF文件,而此mif文件与ALTERA mif文件格式不同。不能用于初始化ALTERA的 RAM。

鉴于例化不同IP的复杂性,现在编译工具也支持利用VERILOG语言来描述RAM,而编译工具自动识别为RAM,自动产生相应的IP核,下面以XILINX的EDA工具为例简要介绍。

module ram(

clk, wr,addr,din,dout

);

input clk;

input [7:0] addr;

input wr;

input [31:0] din;

output [31:0] dout;

reg [31:0] mem [0:255];

reg [31:0] dout;

always@(posedge clk)

if(wr)

mem[addr] <= din;

always @(posedge clk)

dout = mem[addr] ;

endmodule

上述描述可以被描述成RAM,自动产生RAM.其例化的报告为:

=========================================================================

* HDL Synthesis *

=========================================================================

Performing bidirectional port resolution...

Synthesizing Unit .

Related source file is "ram.v".

Found 256x32-bit single-port RAM for signal .

Found 32-bit register for signal .

Summary:

inferred 1 RAM(s).

inferred 32 D-type flip-flop(s).

Unit synthesized.

=========================================================================

HDL Synthesis Report

Macro Statistics

# RAMs : 1

256x32-bit single-port RAM : 1

# Registers : 1

32-bit register : 1

=========================================================================

综上: RAM作为FPGA内部一种基本资源,掌握RAM的特性和基本用法,则是FPGA工程师的基本技能,能够充分利用FPGA内部的资源,毕竟对于FPGA来说“资源就是金钱”,节省资源就是省钱。

在FPGA内部资源中,RAM是较为常用的一种资源。

通常实例化RAM中,一种使用为BLOCK RAM 也就是块RAM 。另外资源可以通过寄存器搭,也就是分布式RAM。前者一般用于提供较大的存储空间,后者则提供小的存储空间。

在实际应用过程中,一般使用的包括,单端口、双端口RAM,ROM等形式等不同的形式。 实际应用中FIFO也是利用RAM和逻辑一起实现的。

对于一块RAM中,其能够例化的深度是有限的。例如cyclone4的RAM9k中可以例化的资源如下所示:

因此:例化化深度<256的RAM,其同样也需要占用一块BLOCKRAM的资源,例如例化宽度为64 深度为128的RAM,其资源为8K 。但是仍然需要占用两块BOCK RAM。也就是说,只要例化RAM深度少于256.则对于本器件9K来说,剩下的资源也是浪费。

那是不是可以例化成双端口RAM,通过高位地址区分,变为两个单端口RAM(width:32,depth:128)来使用,这样就可以节省资源了?

而对于双端口RAM来说,每个M9K能够配置是的最小深度就变成是512,而最大宽度为18,如下图所示,因此作为真双端口RAM使用,深度小于512的话,仍然会占用1块RAM。且宽度》18就会多占用额外的一块RAM,因此上述的节省资源的方式是不正确的。

通过查看datasheet的中RAM能够配置的方式,从而能够正确的使用RAM资源,从而达到高的利用效率。可以看出,RAM9K其应用方式受限,主要是因为RAM的端口的连接信号受限,例如:该RAM9K的读端口最大支持36根信号线,因此对于单端口其支持的宽度为36,双端口为18(两个端口,总共36根数据线),作为FPGA来说,其布线资源是有限的,不可能无限制的增加其端口数。

RAM例化时,有时需要初始化RAM,ALTERA和XLINX的初始化方法如下所示:

(1)ALTERA RAM中,例化时为MIF文件,其格式为:

DEPTH = 32; -- The size of memory in words

WIDTH = 8; -- The size of data in bits

ADDRESS_RADIX = HEX; -- The radix for address values

DATA_RADIX = HEX; -- The radix for data values

CONTENT -- start of (address : data pairs)

BEGIN

00 : 0; -- memory address : data

01 : 1;

END;

(2)在XILINX的RAM中,RAM出示化文件为COE文件,其格式为:

MEMORY_INITIALIZATION_RADIX=2; 设定进制

MEMORY_INITIALIZATION_VECTOR= 初始化向量

值得注意的是:XILINX的RAM初始化后会自动生成MIF文件,而此mif文件与ALTERA mif文件格式不同。不能用于初始化ALTERA的 RAM。

鉴于例化不同IP的复杂性,现在编译工具也支持利用VERILOG语言来描述RAM,而编译工具自动识别为RAM,自动产生相应的IP核,下面以XILINX的EDA工具为例简要介绍。

module ram(

clk, wr,addr,din,dout

);

input clk;

input [7:0] addr;

input wr;

input [31:0] din;

output [31:0] dout;

reg [31:0] mem [0:255];

reg [31:0] dout;

always@(posedge clk)

if(wr)

mem[addr] <= din;

always @(posedge clk)

dout = mem[addr] ;

endmodule

上述描述可以被描述成RAM,自动产生RAM.其例化的报告为:

=========================================================================

* HDL Synthesis *

=========================================================================

Performing bidirectional port resolution...

Synthesizing Unit .

Related source file is "ram.v".

Found 256x32-bit single-port RAM for signal .

Found 32-bit register for signal .

Summary:

inferred 1 RAM(s).

inferred 32 D-type flip-flop(s).

Unit synthesized.

=========================================================================

HDL Synthesis Report

Macro Statistics

# RAMs : 1

256x32-bit single-port RAM : 1

# Registers : 1

32-bit register : 1

=========================================================================

综上: RAM作为FPGA内部一种基本资源,掌握RAM的特性和基本用法,则是FPGA工程师的基本技能,能够充分利用FPGA内部的资源,毕竟对于FPGA来说“资源就是金钱”,节省资源就是省钱。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)