Xilinx UltraScale架构 — 业界首款ASIC级All Programmable架构

时间:07-10

来源:互联网

点击:

UltraScale架构3D集成可增强所有功能

最新Virtex UltraScale和Kintex UltraScale系列成员产品能使赛灵思第二代3D IC架构中的连接功能资源数量及相关晶片间带宽实现阶梯式增长。布线、带宽和最新3D IC大容量存储器优化接口容量的显著增加能确保新一代应用在极高的利用率水平下实现目标性能。

实现快速、智能处理

从噪声中提取更多信号,创建更加逼真的画面,以及应对无止境的数据包流量增长,所有这些都在对智能处理性能提出更高要求。与此同时,还要将成本控制在规定的预算范围内,这样就给设计带来了诸多实际限制。简言之,市场需要以更少的成本实现更高的系统性能,这是大多数电子产业永恒不变的趋势。而赛灵思的UltraScale器件非常适合满足这些多元化的设计要求。

最新的27x18位乘法器和双加法器以及关键路径优化功能显著提升了定点和IEEE 754标准浮点算法的性能与效率。UltraScale架构能够让双精度浮点运算的资源利用率实现1.5倍的效率提升,并具有更多的DSP资源数量,因此可以满足新一代应用在TMAC处理性能和集成方面的要求,并实现最优价格点。

UltraScale架构经过专门优化,可解决以数百Gbps速率运行的包处理功能有关的关键路径瓶颈问题,这些功能包括:误差校正与控制(ECC)、循环冗余校验(CRC)以及前向纠错(FEC)。增强型DSP子系统,与硬化的100 GbE MAC和Interlaken接口以及赛灵思SmartCore 包处理与流量管理IP完美结合在一起,采用最佳封装,能够实现线速高达数百Gbps的包处理功能。

提供海量I/O和存储器带宽

UltraScale架构能在显著增强高速SerDes收发器性能的同时大幅降低其功耗。Virtex UltraScale器件采用可支持5 Tbps以上串行系统带宽的新一代SerDes(收发器)。ASIC级SerDes的灵活性要高于早期器件中的SerDes,同时保留了前代产品可靠的自适应均衡功能(自动增益控制、连续时间线性均衡、判定反馈均衡以及sliding 滑动DFE)。赛灵思的自适应均衡功能可将误码率维持在无法察觉的水平(<10 17)并允许UltraScale SerDes直接驱动每秒高达数GHz的高速背板。

赛灵思UltraScale架构集成了多个DDR3/4-SDRAM存储控制器以及硬化的DDR物理层(PHY)片上模块,从而将存储器接口功能推向一个全新高度。UltraScale器件包含:

• 更多SDRAM控制器

• 更广泛的SDRAM端口

• 更快的存储器端口

硬化的SDRAM PHY模块与软核PHY相比能够将读取时延降低30%,同时它具有控制DDR4 SDRAM的能力,可将外部存储器功耗降低20%以上。

片上模块RAM(BRAM)经重新构建后可与系统中其它可编程模块性能相匹配并降低功耗。利用新的架构特性,设计人员无需使用其它片上布线或逻辑资源就能高效创建出大规模快速RAM阵列和FIFO。

UltraScale架构满足新一代系统的系统级功耗要求

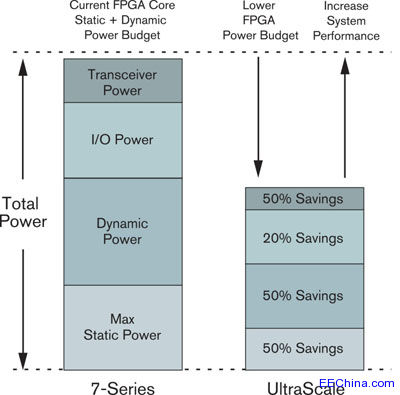

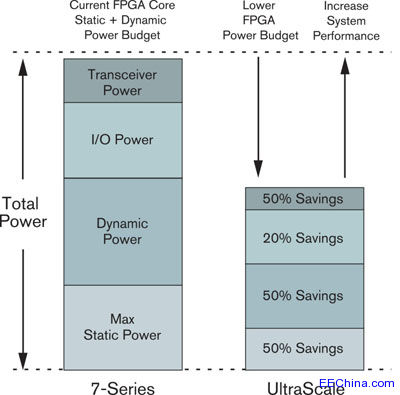

每一代All Programmable逻辑器件系列都能显著降低系统级功耗,UltraScale架构正是建立在这一传统优势之上。低功耗半导体工艺以及通过芯片与软件技术实现的宽范围静态与动态电源门控可将系统总功耗降低至赛灵思7系列FPGA(业界最低功耗的All Programmable器件)的一半。

图5:采用UltraScale架构实现最低总功耗

降低功耗对设计人员来说意味着两件事:(1)更低的功耗预算和散热管理要求;(2)更高的速度。这两点对满足新一代应用不断提高的要求极为重要。

UltraScale的IP保护与防篡改安全功能

赛灵思的安全解决方案与创新产品已经历了五代以上的发展,UltraScale All Programmable架构在这一基础上引入了多种增强型安全特性,可对载入器件内的IP提供更强的保护并实现防篡改功能,继续保持着延续赛灵思在安全解决方案领域的领先地位。UltraScale 架构在安全性方面的改进包括:更强大更先进的AES比特流解密与认证方案;更多密钥模糊处理功能;确保在编程过程中无法对加密密钥进行外部访问。这样就能得到稳定可靠的业界领先解决方案,满足不断变化的新一代安全要求。

UltraScale与Vivado协同优化 = 成功保障

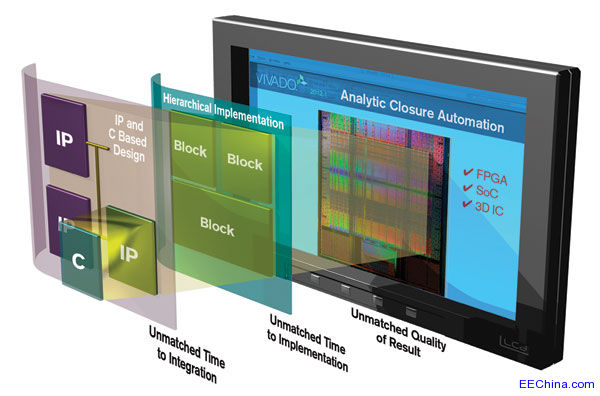

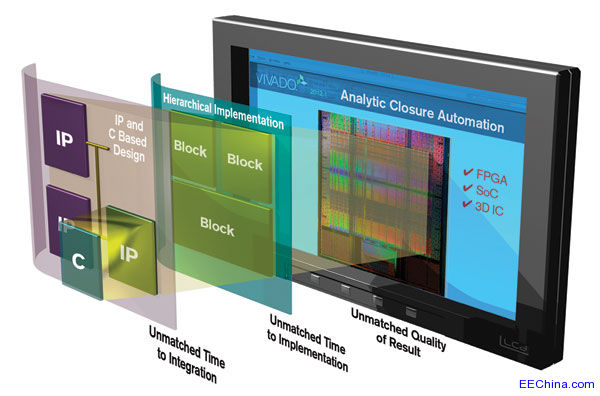

要为最严苛的应用提供前所未有的集成度、容量和ASIC级系统性能,并实现90%以上的空前器件利用率且不降低性能,这就需要采用业界独有的SoC增强型设计环境。

Vivado设计套件是一款全新的SoC增强型设计环境,最初针对赛灵思7系列器件推出,主要用于未来十年的All Programmable器件(例如UltraScale架构)。Vivado能解决可编程系统集成与实现方面的关键设计瓶颈,其生产力相对同类竞争开发环境提高了四倍。

要实现新一代设计提出的超高性能、集成度以及结果质量目标,就需要采用全新的器件布局布线方案。传统FPGA布局布线工具依靠模拟退火作为主要的布局优化算法,无法顾及拥塞程度或总导线长度等全局设计指标。要实现具备多Tb性能的设计,需要采用宽总线而且要求时钟歪斜几乎为零。因此,采用模拟退火这种不考虑总体导线长度和拥塞情况的布局布线算法是绝对不可行的。

Vivado设计套件利用多变量成本函数找出最优布局方案,这样,设计人员就可以快速确定布线方案,并使器件利用率达到90%以上且不降低性能。与采用其他解决方案相比,这种方式的运行时间更短而且结果的变化程度也更小,这样实现设计收敛所需的迭代次数就更少,并且性能和器件利用率都达到了业界前所未有的高水平。

最新Virtex UltraScale和Kintex UltraScale系列成员产品能使赛灵思第二代3D IC架构中的连接功能资源数量及相关晶片间带宽实现阶梯式增长。布线、带宽和最新3D IC大容量存储器优化接口容量的显著增加能确保新一代应用在极高的利用率水平下实现目标性能。

实现快速、智能处理

从噪声中提取更多信号,创建更加逼真的画面,以及应对无止境的数据包流量增长,所有这些都在对智能处理性能提出更高要求。与此同时,还要将成本控制在规定的预算范围内,这样就给设计带来了诸多实际限制。简言之,市场需要以更少的成本实现更高的系统性能,这是大多数电子产业永恒不变的趋势。而赛灵思的UltraScale器件非常适合满足这些多元化的设计要求。

最新的27x18位乘法器和双加法器以及关键路径优化功能显著提升了定点和IEEE 754标准浮点算法的性能与效率。UltraScale架构能够让双精度浮点运算的资源利用率实现1.5倍的效率提升,并具有更多的DSP资源数量,因此可以满足新一代应用在TMAC处理性能和集成方面的要求,并实现最优价格点。

UltraScale架构经过专门优化,可解决以数百Gbps速率运行的包处理功能有关的关键路径瓶颈问题,这些功能包括:误差校正与控制(ECC)、循环冗余校验(CRC)以及前向纠错(FEC)。增强型DSP子系统,与硬化的100 GbE MAC和Interlaken接口以及赛灵思SmartCore 包处理与流量管理IP完美结合在一起,采用最佳封装,能够实现线速高达数百Gbps的包处理功能。

提供海量I/O和存储器带宽

UltraScale架构能在显著增强高速SerDes收发器性能的同时大幅降低其功耗。Virtex UltraScale器件采用可支持5 Tbps以上串行系统带宽的新一代SerDes(收发器)。ASIC级SerDes的灵活性要高于早期器件中的SerDes,同时保留了前代产品可靠的自适应均衡功能(自动增益控制、连续时间线性均衡、判定反馈均衡以及sliding 滑动DFE)。赛灵思的自适应均衡功能可将误码率维持在无法察觉的水平(<10 17)并允许UltraScale SerDes直接驱动每秒高达数GHz的高速背板。

赛灵思UltraScale架构集成了多个DDR3/4-SDRAM存储控制器以及硬化的DDR物理层(PHY)片上模块,从而将存储器接口功能推向一个全新高度。UltraScale器件包含:

• 更多SDRAM控制器

• 更广泛的SDRAM端口

• 更快的存储器端口

硬化的SDRAM PHY模块与软核PHY相比能够将读取时延降低30%,同时它具有控制DDR4 SDRAM的能力,可将外部存储器功耗降低20%以上。

片上模块RAM(BRAM)经重新构建后可与系统中其它可编程模块性能相匹配并降低功耗。利用新的架构特性,设计人员无需使用其它片上布线或逻辑资源就能高效创建出大规模快速RAM阵列和FIFO。

UltraScale架构满足新一代系统的系统级功耗要求

每一代All Programmable逻辑器件系列都能显著降低系统级功耗,UltraScale架构正是建立在这一传统优势之上。低功耗半导体工艺以及通过芯片与软件技术实现的宽范围静态与动态电源门控可将系统总功耗降低至赛灵思7系列FPGA(业界最低功耗的All Programmable器件)的一半。

图5:采用UltraScale架构实现最低总功耗

降低功耗对设计人员来说意味着两件事:(1)更低的功耗预算和散热管理要求;(2)更高的速度。这两点对满足新一代应用不断提高的要求极为重要。

UltraScale的IP保护与防篡改安全功能

赛灵思的安全解决方案与创新产品已经历了五代以上的发展,UltraScale All Programmable架构在这一基础上引入了多种增强型安全特性,可对载入器件内的IP提供更强的保护并实现防篡改功能,继续保持着延续赛灵思在安全解决方案领域的领先地位。UltraScale 架构在安全性方面的改进包括:更强大更先进的AES比特流解密与认证方案;更多密钥模糊处理功能;确保在编程过程中无法对加密密钥进行外部访问。这样就能得到稳定可靠的业界领先解决方案,满足不断变化的新一代安全要求。

UltraScale与Vivado协同优化 = 成功保障

要为最严苛的应用提供前所未有的集成度、容量和ASIC级系统性能,并实现90%以上的空前器件利用率且不降低性能,这就需要采用业界独有的SoC增强型设计环境。

Vivado设计套件是一款全新的SoC增强型设计环境,最初针对赛灵思7系列器件推出,主要用于未来十年的All Programmable器件(例如UltraScale架构)。Vivado能解决可编程系统集成与实现方面的关键设计瓶颈,其生产力相对同类竞争开发环境提高了四倍。

要实现新一代设计提出的超高性能、集成度以及结果质量目标,就需要采用全新的器件布局布线方案。传统FPGA布局布线工具依靠模拟退火作为主要的布局优化算法,无法顾及拥塞程度或总导线长度等全局设计指标。要实现具备多Tb性能的设计,需要采用宽总线而且要求时钟歪斜几乎为零。因此,采用模拟退火这种不考虑总体导线长度和拥塞情况的布局布线算法是绝对不可行的。

Vivado设计套件利用多变量成本函数找出最优布局方案,这样,设计人员就可以快速确定布线方案,并使器件利用率达到90%以上且不降低性能。与采用其他解决方案相比,这种方式的运行时间更短而且结果的变化程度也更小,这样实现设计收敛所需的迭代次数就更少,并且性能和器件利用率都达到了业界前所未有的高水平。

DSP 赛灵思 总线 电源管理 收发器 电子 半导体 FPGA SoC 电路 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- FPGA作为协处理器在实时系统中的应用(04-08)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)

- 基于Spartan-3A DSP的安全视频分析(05-01)