基于FPGA的高速数据采集系统的设计

目前,在数据采集系统的硬件设计方案中,有采用通用单片机和USB相结合的方案,也有采用DSP和USB相结合的方案,前者虽然硬件成本低,但是时钟频率较低,难以满足数据采集系统对速度要求;后者虽然可以实现高速传输,但DSP价格过于昂贵。而利用FPGA和USB接口芯片结合的方案,具有功耗低、时钟频率高、速度快、效率高、组合形式灵活等特点,是单片机和DSP所无法比拟的。

系统总体方案

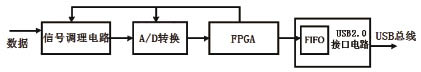

根据本系统要实现的功能,该系统硬件部分采用“信号调理电路+A/D转换电路+FPGA+USB 2.0接口芯片”的模式加以设计。系统采用可编程逻辑器件FPGA控制信号调理电路的工作,同时控制A/D转换器采样,这样通过硬件描述语言来描述可以使硬件设计如同软件一样灵活,并且FPGA可重复编程的特性提高了工作效率和设计的灵活性。另外系统所需的高速缓存FIFO是由USB 2.0接口芯片的片内资源来实现的,这样做可以降低系统成本、提高系统可靠性。USB 2.0接口芯片的固件程序由集成在芯片内的增强型8051单片机进行控制,固件程序存放在主机上,在系统上电后通过上位机驱动程序下载到芯片内部的RAM内。系统的总体方案如图1所示。

图1 数据采集系统结构图

整个硬件电路的工作流程是:当上位机发来数据采集请求,FPGA就开始启动对信号调理模块和A/D采样控制模块的控制。经过A/D转换后的数据按照一定的时序发送到USB 2.0接口芯片的端口FIFO里面,然后再把数据通过USB总线传输给上位机。

系统硬件设计与实现

本数据采集系统的硬件设计主要是基于USB 2.0的硬件数据采集卡的设计。此采集卡的作用是首先用A/D转换器对输入的电路实验数据进行采样量化,然后将采样得到的数据通过USB 2.0总线传送到上位机,以便进行后续处理。

主控芯片简介

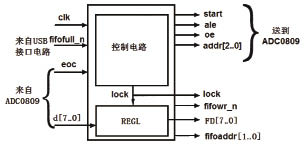

Altera公司的Cyclone II FPGA是基于Stratix II的90nm工艺推出的低成本FPGA,由于增加了DSP硬件块,在芯片总体性能上要优于Cyclone系列器件,而在成本上却仍维持Cyclone系列低成本的优点。本设计选用了Cyclone II系列中的EP2C5Q208芯片,其逻辑单元有4608个,M4K RAM有26个,锁相环有2个、乘法器模块有13个,最大用户可用I/O引脚为142个,可以满足本设计的需要。图2为EP2C5Q208的外围连接电路框图。

图2 主控芯片连接框图

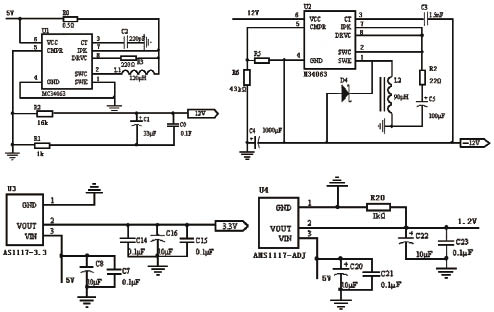

电源电路

设计电源电路之前,首先对系统中各器件所需电源的需求情况进行分析,电源电路需要提供5种直流电压才能满足系统对电源的需求:FPGA的供电电压是3.3V和1.2V;信号调理电路电压为+12V和-12V;A/D转换器ADC0809所需要的电压为5V;USB 2.0接口芯片CY7C68013需要3.3V供电。而系统只有USB总线能提供+5V电压,因此需使用开关电源进行电压转换。电压转换电路如图3所示。

图3 电源电路

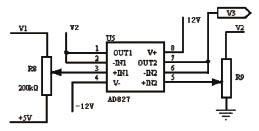

信号调理电路

信号调理电路的作用是对微弱的输入信号进行适当的调理,使其电压范围在0~5V之间,从而满足A/D转换芯片的输入电压的要求。本调理电路中采用了运算放大器芯片AD827。该芯片最高带宽为50MHz,芯片内部集成2片运放,分别用来进行信号的放大平移和衰减。信号调理电路如图4所示。

图中左半部分为第一个环节,这个环节输入电压V1,输出电压为V2,对于微弱的输入信号,可以经过调理达到正常电平范围之内。右半部分为第二个环节,这个环节是信号的衰减环节,若第一个环节得到的电压幅值较大,超过了0~5V的电压范围,则可以将此信号在第二个环节进行衰减。第二个环节的最大增益为1,通过调节电位器,可以使信号最小衰减为0。这样,信号经过信号调理电路之后,就可以满足A/D采样的要求了。

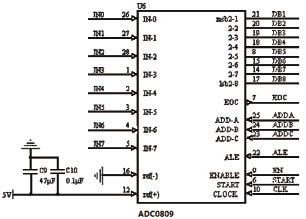

A/D采样电路

经过调理后的模拟信号需要经A/D转换芯片进行采样、量化、编码,然后将编码后的数据经过USB 2.0接口芯片传送至USB主机,A/D采样电路是整个数据采集电路的关键部分。本设计所使用的A/D采样芯片是ADC0809转换芯片,它是通过采样逐次逼近的方法完成A/D转换的。ADC0809由单一+5V电源供电,片内带有锁存功能的8路模拟多路开关,可以对8路0~5V的模拟信号分时进行转换。A/D转化器电路的连接如图5所示,其中,参考电压VREF+接+5V,VREF-接地,输入模拟电压范围为0~5V。

图5 A/D采样电路

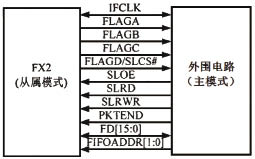

图6 从属FIFO模式连接框图

USB 2.0接口电路

Cypress公司的EZ-USB FX2系列芯片是世界上第一个集成了USB 2.0协议的微处理器,它支持12Mb/s的全速传输和480Mb/s的高速传输,可使用4种USB传输方式。本系统采用EZ-USB FX2系列中CY7C68013-56PVC芯片。该芯片集成了USB 2.0收发器、串行接口引擎SIE(Serial Interface Engine)、8.5KB的RAM、4KB的FIFO存储器、I/O口、通用可编

单片机 USB DSP FPGA 电路 51单片机 总线 Altera 电压 ADC 开关电源 放大器 Cypress 收发器 相关文章:

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- FPGA作为协处理器在实时系统中的应用(04-08)

- 我的FPGA学习历程(05-23)