利用 All Programmable FPGA、SoC 和3D IC 领先一代

时间:11-14

来源:互联网

点击:

采用 VIVADO 提高工作效率

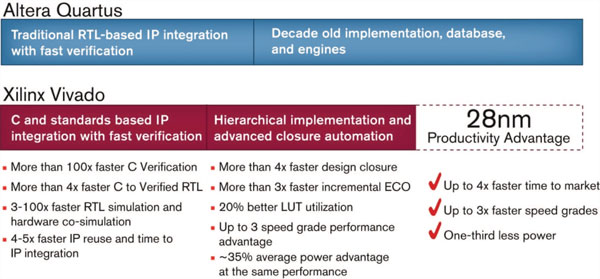

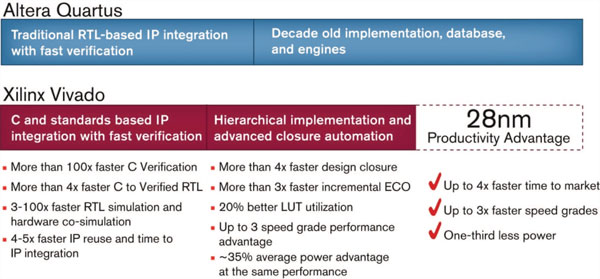

为了提高设计人员采用 28 nm 及其更高 All Programmable 器件的工作效率,赛灵思还全新开发了新一代设计环境和工具套件 Vivado ™(图 4)。开发工作耗时 4 个日历年以上,凝聚500 人多年的努力。没有这款设计套件,设计团队就不能有效地发挥赛灵思 3D IC 的潜力。

对 FPGA 和 SoC 而言,Vivado Design Suite 将设计质量结果提升了三个速度等级,将动态功耗降低了高达 50%,可路由性和资源利用率提升了 20% 以上,集成和实现速度翻了两番之多。

如欲了解关于 Vivado 的更多详情,敬请参阅 Xcell 杂志第 79 期的封面报道。

图 4:赛灵思的 Vivado 为设计人员带来一流的设计套件,大幅提升工作效率,显著加速产品上市进程。

Vivado 对支持新型 All Programmable 器件组合、实现可编程系统高度集成发挥着至关重要的作用。因此,我们关注的重点大大超越了加速实施流程和 QoR、利用尖端分析引擎和关闭自动化。为了实现出色的集成度,Vivado 支持分层架构、IP 核封装和重用、自动化 IP 核拼接以及高速验证。为了进一步加快产品上市进程,提高设计抽象化水平,Vivado 支持基于 C 设计和验证的流程,能通过高层次综合和自动化 AXI 接口生成来加速从 C 到 RTL IP 的创建和集成速度。这样,Vivado 不仅加速了实现速度,也在设计前端加快了 C 到 RTL 的集成速度。

总结

赛灵思如今开发了各种形式的可编程技术,超越了可编程硬件而涵盖软件领域,超越了数字而涵盖 AMS,超越单芯片而涵盖多芯片 3D IC 实施方案。赛灵思将这些技术整合到 All Programmable FPGA、SoC 以及 3D IC 中,可帮助设计团队提高可编程系统集成度,改进整体系统性能,降低材料清单成本,并加快向市场推出创新型产品的速度。赛灵思产品组合的变革转型可追溯到 2008 年,部分创新技术则能进一步上溯到 2006 年,其成果则是如今的产品组合技术已整整领先竞争对手一代的水平,为客户带来增值。

放眼 20nm 工艺节点,赛灵思将推出更高级的 FPGA、第二代 SoC 以及 3D IC 产品,进一步扩大领先地位,同时还将推出 Vivado 设计系统,使赛灵思的技术水平始终领先一代之遥。赛灵思开始同客户合作调节改进 SoC 和 3D IC 技术的举措领先竞争对手多年,重新定义了高速串行收发器等关键核心技术的开发和交付,改进了设计方法和工具,扩展了系统级生态系统

和供应链,并确保其质量和可靠性。

为了提高设计人员采用 28 nm 及其更高 All Programmable 器件的工作效率,赛灵思还全新开发了新一代设计环境和工具套件 Vivado ™(图 4)。开发工作耗时 4 个日历年以上,凝聚500 人多年的努力。没有这款设计套件,设计团队就不能有效地发挥赛灵思 3D IC 的潜力。

对 FPGA 和 SoC 而言,Vivado Design Suite 将设计质量结果提升了三个速度等级,将动态功耗降低了高达 50%,可路由性和资源利用率提升了 20% 以上,集成和实现速度翻了两番之多。

如欲了解关于 Vivado 的更多详情,敬请参阅 Xcell 杂志第 79 期的封面报道。

图 4:赛灵思的 Vivado 为设计人员带来一流的设计套件,大幅提升工作效率,显著加速产品上市进程。

Vivado 对支持新型 All Programmable 器件组合、实现可编程系统高度集成发挥着至关重要的作用。因此,我们关注的重点大大超越了加速实施流程和 QoR、利用尖端分析引擎和关闭自动化。为了实现出色的集成度,Vivado 支持分层架构、IP 核封装和重用、自动化 IP 核拼接以及高速验证。为了进一步加快产品上市进程,提高设计抽象化水平,Vivado 支持基于 C 设计和验证的流程,能通过高层次综合和自动化 AXI 接口生成来加速从 C 到 RTL IP 的创建和集成速度。这样,Vivado 不仅加速了实现速度,也在设计前端加快了 C 到 RTL 的集成速度。

总结

赛灵思如今开发了各种形式的可编程技术,超越了可编程硬件而涵盖软件领域,超越了数字而涵盖 AMS,超越单芯片而涵盖多芯片 3D IC 实施方案。赛灵思将这些技术整合到 All Programmable FPGA、SoC 以及 3D IC 中,可帮助设计团队提高可编程系统集成度,改进整体系统性能,降低材料清单成本,并加快向市场推出创新型产品的速度。赛灵思产品组合的变革转型可追溯到 2008 年,部分创新技术则能进一步上溯到 2006 年,其成果则是如今的产品组合技术已整整领先竞争对手一代的水平,为客户带来增值。

放眼 20nm 工艺节点,赛灵思将推出更高级的 FPGA、第二代 SoC 以及 3D IC 产品,进一步扩大领先地位,同时还将推出 Vivado 设计系统,使赛灵思的技术水平始终领先一代之遥。赛灵思开始同客户合作调节改进 SoC 和 3D IC 技术的举措领先竞争对手多年,重新定义了高速串行收发器等关键核心技术的开发和交付,改进了设计方法和工具,扩展了系统级生态系统

和供应链,并确保其质量和可靠性。

赛灵思 FPGA SoC EDA 嵌入式 半导体 ARM 仿真 DSP 收发器 电路 自动化 相关文章:

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA可帮助搜索引擎降低功耗和碳排放(09-12)

- 基于Spartan-3A DSP的安全视频分析(05-01)

- 赛灵思新版视频入门套件加快视频开发速度(05-29)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)

- 赛灵思详解新近推出的FPGA领域设计平台(12-16)