基于FPGA的行间转移面阵CCD驱动电路设计

时间:11-30

来源:互联网

点击:

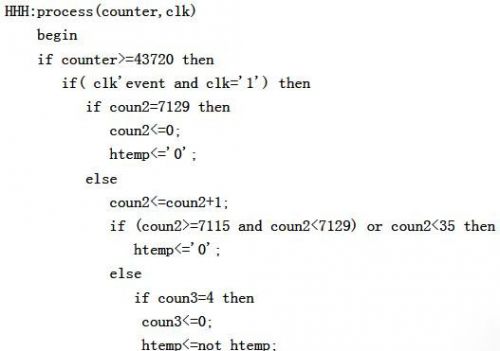

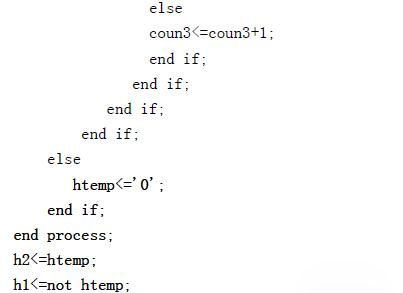

参见其使用说明书。其中实现H1和H2部分程序如下:

本文选用的FPGA是Xilinx公司的XC2S150,一共有150,000个逻辑门,满足整个系统的所有需求;采用硬件描述语言VHDL进行逻辑设计,用ModelSim仿真,关键部分的波形见图3。

6、结论

本文的创新是:先将V2三电平进行分解,之后巧妙地利用两个驱动器和钳位电路来实现三电平阶梯波形的时序驱动;采用FPGA器件来设计行间转移面阵CCD驱动时序。系统设计完成后,由示波器测试各路输出的驱动信号,所显示的波形与仿真波形一致,得到令人满意的结果。因此本文的驱动电路设计方案能够满足的KAI-0340的性能要求,可以用来驱动行间转移型面阵CCDKAI-0340S。

Source:互联网

传感器 电路 电压 DSP CPLD FPGA 电子 电流 电源模块 电容 Xilinx VHDL ModelSim 仿真 示波器 相关文章:

- 基于FPGA的高速图像采集系统设计(03-30)

- 在单个FPGA平台上采用多种工业以太网标准进行设计(03-13)

- 基于CPLD的CCD信号发生器的研究(04-08)

- 在嵌入式设计中降低CPLD的功耗(04-30)

- Xilinx FPGA的功耗优化设计(04-08)

- 基于太空级Virtex FPGA的灵活高性能计算平台(04-08)