基于FPGA的LED大屏幕控制系统设计

时间:03-25

来源:互联网

点击:

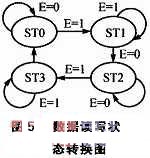

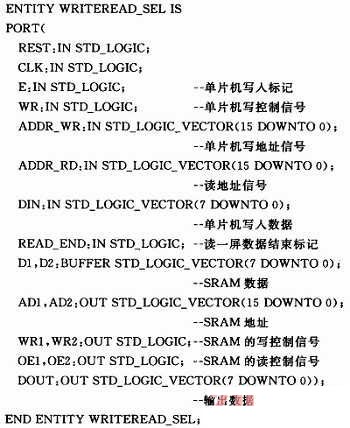

该模块采用VHDL有限状态机来实现,整个控制分为4个状态,其状态转换图如图5所示。其工作过程如下:系统开机进入初始状态ST0,单片机的写入使能端E为低电平,单片机从EEPROM中读取数据并把数据写入到SRAM1,同时FPGA读取SRAM2中的数据;当单片机数据写完一屏数据后E变为高电平,当FPGA从SRAM2中读完数据、结束信号READ_END为低电平时,进入ST1状态。

在ST1状态下,若没有新的数据写入则E保持高电平,FPGA读取SRAM1的数据,为静态显示;只有当单片机的读入控制信号E为低电平且READ_END为低电平时,进入ST2状态。在ST2状态下,单片机把数据写入SRAM2,同时FPGA读取SRAM1的数据,单片机数据写完后E变为高电平,当FPGA一屏数据读完后READ_END为低电平,进入ST3状态。在ST3状态下,如果没有新数据写入E为高电平,FPGA读取SRAM2中的数据。当单片机有新的数据写入时E变为低电平,当FPGA一屏数据读完后READ_END为低电平时,重新进入ST0状态。通过这种周而复始的交替工作完成数据的写入与读取,其端口程序如下:

3.3 读地址发生器

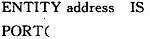

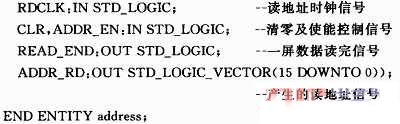

读地址发生器主要产生外部缓存器SRAM1(SRAM2)的读地址信号,使系统能正确地从存储器中读取相应的显示数据。其地址最高位为0,其余地址分别为行地址(hang[3..0])、列地址(lie[6..0])、分区地址(qu[3..0])15位有效地址信号。在16个脉冲周期内读出在SRAM1(SRAM2)中的16字节数据,其部分VHDL源程序如下:

3.4 译码器

译码器模块主要是产生16路的分区信号(低电平有效)分别控制16个锁存器,把16个分区的显示数据分别锁存在相应的锁存器中。

3.5 数据锁存器组及移位寄存器组模块

数据锁存器组模块由16个8位锁存器组成锁存器组,锁存16个分区的数据。移位寄存器组模块由16个8位移位寄存器组成,把各路锁存器中8位并行数据转换成同时输出的16路串行数据,驱动LED显示屏,实现数据的并串转换。

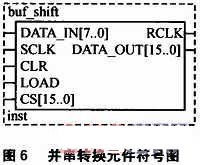

其生成的元件符号如图6所示。其中,DATA IN[7..0]为每个分区的8位并行数据输入,SCLK为移位时钟,CLR为清零信号,LOAD为数据锁存信号,CS[15..0]为16分区的输入信号(接译码器的输出),DATA_OUT[15..0]为16路的串行数据输出。

3.6 脉冲发生器

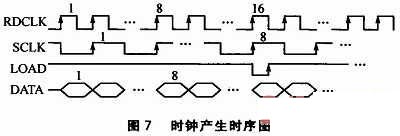

系统采用1/16的扫描方式,把数据分为16分区,16分区数据同时传送。假设刷新的频率为60 Hz(即周期为16.67 ms),每一行显示的时间约为16.67 ms/16=1.04 ms。每行有1024位,则移位脉冲周期为1.04/1024=1.02 μs,即移位频率为0.983 MHz以上才能满足要求。由于移位脉冲是数据读取模块时钟的2分频,因此系统的时钟至少1.97 MHz以上,本系统采用50 MHz时钟源。其时序图如图7所示。

其中,RDCLK为FPGA读取数据时钟;SCLK是串行输出的移位时钟,是RDCLK的2分频;LOAD是数据锁存信号,每次读完16个分区中的某个字节数据DATA后产生锁存信号,数据锁存在数据锁存器组中,其时钟是RDCLK的16分频。

4 FPGA控制模块的仿真测试

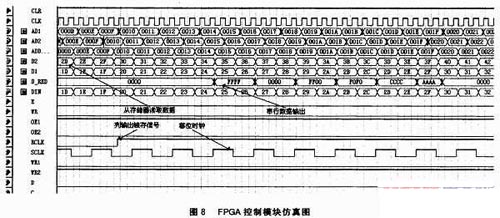

在QuartusII 5.1中建立一个工程,并建立原理图文件,把单片机与FPGA接口及数据读写模块、读地址发生器、译码器、行地址发生器、数据锁存器、移位寄存器、脉冲发生器等单元模块所生的模块元件符号连接起来,构成总控制模块逻辑图并对其功能仿真。仿真结果如图8所示,从存储器中读取16字节数据,经并串转换输出16路的串行数据。从波形图分析,功能正确,且各输出端口信号均符合时序要求。

结语

FPGA是在线可编程芯片,可以根据不同的用户要求进行不同的编程,缩短了系统的开发周期并节约了硬件的开发成本。本文以FPGA为主芯片,较完整地设计了大屏幕LED单色图文显示屏控制系统。随着LED显示屏技术的发展,FPGA与ARM或DSP等芯片的组合,必将在双色显示屏和彩色显示屏领域获得广泛的应用。

LED MCU FPGA 单片机 VHDL Quartus 仿真 电路 ARM DSP 相关文章:

- 我的FPGA学习历程(05-23)

- 适用于消费性市场的nano FPGA技术(09-27)

- Actel数模结合FPGA的远程控制器设计(05-13)

- 专用键盘接口芯片一种CPLD实现方案(06-29)

- CPLD为控制核心16位高精度数字电压表设计(06-25)

- 基于FPGA的发电机组频率测量计的实现(07-22)