CPLD为控制核心16位高精度数字电压表设计

时间:06-25

来源:互联网

点击:

1 引言

CPLD ( Complex Programmable Logic Device ) 是新型的可编程逻辑器件,与传统ASIC相比,具有设计开发周期短、设计制造成本低、开发工具先进等优点,特别适合于产品的样品开发和小批量生产。传统的数字电压表多以单片机为控制核心,芯片集成度不高,系统连线复杂,难以小型化,尤其在产品需求发生变化时,不得不重新布版、调试,增加了投资风险和成本。而采用CPLD进行产品开发,可以灵活地进行模块配置,大大缩短了开发周期,也有利于数字电压表向小型化、集成化的方向发展。

2系统原理及组成

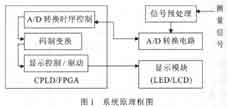

系统组成原理框图如图1所示。系统的控制核心是一片CPLD芯片,它由三个功能模块构成: A/D转换时序控制模块、码制变换模块以及显示控制/驱动模块。三个模块的功能分别为发出控制信号启动A/D转换及读取采样值、对AD采样值进行码制转换、发出控制信号驱动LED/LCD显示相应数据。

系统工作原理:测量信号经过信号预处理,变换为0~2.5V范围内的有效信号后送入A/D转换电路中,然后A/D转换时序控制模块发出控制信号,启动A/D转换器进行转换,A/D采样得到的数字信号在码制变换模块中转换为相应的显示代码,最后经显示控制/驱动模块发出控制与驱动信号,推动外部的显示模块(LED/LCD)显示相应的数据。

3CPLD功能模块设计

智能数字电压表的控制核心CPLD的三个功能模块皆用VHDL语言编程实现,下面主要介绍CPLD的三个功能模块的设计。

3.1 A/D转换时序仿真模块AD_CONTROL

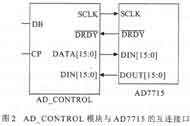

ANALOG DEVICES公司生产的AD7715是一片16位的∑-Δ ADC集成电路。它的主要特性有:3V/5V工作电压,单/双极性输入;可编程改变增益为1,2,32,128倍;在单极性输入状态下模拟电压输入范围允许为0~20mV, 0~80mV, 0~1.25V, 0~2.5V不等(有利于提高精度);三线串行接口;支持差分输入;低功耗(450 mF [email=Max@3V]Max@3V[/email])。在本系统中AD7715的作用是将0~2.5V的输入模拟信号转换为16位的高精度的数字信号供CPLD处理。AD_CONTROL模块用于控制AD7715的启动、读、写等操作。设计的AD_CONTROL模块如图2所示,其VHDL语言的ENTITY定义部分如下:

ENTITY AD_CONTROL IS

PORT(

SCLK:OUT STD_LOGIC;

DRDY:IN STD_LOGIC;

DOUT:OUT STD_LOGIC_VECTOR(15 DOWNTO 0);

DIN:IN STD_LOGIC_VECTOR(15 DOWNTO 0);

DB:OUT STD_LOGIC_VECTOR(15 DOWNTO 0);

CP:IN STD_LOGIC

);

END AD_CONTROL;

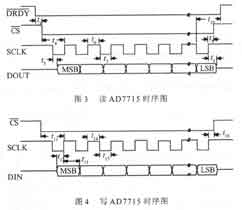

如图所示,二者的接口信号线直接连接并由AD_CONTROL模块模拟产生AD7715芯片的各个接口信号,完成ADC的启动、读、写操作。AD7715的工作模式由内部寄存器(Communications Register,Setup Register,Test Register,Data Register)中的控制字决定。内部寄存器的数据写入和读出都由CS,DRDY,SCLK信号控制。当 AD7715被访问时,SCLK脚应出现一次带上升沿的高电平,其时钟频率应为9.2kHz。这是关键信号,其他信号均以此信号作为时基。因此,CPLD中的AD_CONTROL模块的功能之一就是提供SCLK 以及其他信号的严格时序。图3、图4分别为AD_CONTROL模块读、写AD7715时序图。

3. 2 码制变换模块DATA_CONVERSION

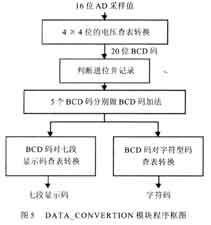

在此码制变换模块DATA_CONVERSION中主要实现的功能是将AD采样送来的16位的二进制数转换为可被LED/LCD识别的七段LED显示码或字符型LCD码。在本系统中此模块包含了这两种转换功能以适应显示端不同的配置。为了达到这一目的,首先要将16位二进制码变换为BCD码,然后再分别进行转换,得到七段显示码及字符型码。在此模块中各个BLOCK部分的码制变换的VHDL程序可通过WHEN-ELSE语句进行查表来实现。转换的过程如图5所示。

3.3 显示控制及驱动模块DISL_DRIVE

电压值的显示可由LED或LCD实现。在本系统中对于电压值的显示分为mV和V两档,所以需要在后面加上单位来明确,且本系统为低功耗系统,若用LED则功耗相对过大,所以选用了一块8×2字符型液晶显示模块MDSL81809-03,实现了低功耗,而且可带单位双排显示,字体美观大方。 DISL_DRIVE示,整个电路十分简洁。系统工作过程首先由 CPLD对AD7715及LCD进行初始化,然后当有输入信号V i(0~2.5V)到AIN+端后,由CPLD通过接口向AD7715的寄存器中写入控制字,使其对输入的模拟信号进行转换,变为16位的数字信号送到DOUT端,由CPLD经过码制变换等处理后,再通过与LCD的接口驱动并发送数据,将电压值及单模块与LCD的接口如图6所示。图中LCD的RS端需输入方波驱动,这可由CPLD编程提供。当AD7715采样完成后,由DATA_CONVERSION模块将采样数字信号转换为LCD可识别的字符型数据后,送至DISL_DRIVE模块,再由其驱动LCD,将字符型数据送到LCD的D0~D7端,实现显示。

CPLD ( Complex Programmable Logic Device ) 是新型的可编程逻辑器件,与传统ASIC相比,具有设计开发周期短、设计制造成本低、开发工具先进等优点,特别适合于产品的样品开发和小批量生产。传统的数字电压表多以单片机为控制核心,芯片集成度不高,系统连线复杂,难以小型化,尤其在产品需求发生变化时,不得不重新布版、调试,增加了投资风险和成本。而采用CPLD进行产品开发,可以灵活地进行模块配置,大大缩短了开发周期,也有利于数字电压表向小型化、集成化的方向发展。

2系统原理及组成

系统组成原理框图如图1所示。系统的控制核心是一片CPLD芯片,它由三个功能模块构成: A/D转换时序控制模块、码制变换模块以及显示控制/驱动模块。三个模块的功能分别为发出控制信号启动A/D转换及读取采样值、对AD采样值进行码制转换、发出控制信号驱动LED/LCD显示相应数据。

|

系统工作原理:测量信号经过信号预处理,变换为0~2.5V范围内的有效信号后送入A/D转换电路中,然后A/D转换时序控制模块发出控制信号,启动A/D转换器进行转换,A/D采样得到的数字信号在码制变换模块中转换为相应的显示代码,最后经显示控制/驱动模块发出控制与驱动信号,推动外部的显示模块(LED/LCD)显示相应的数据。

3CPLD功能模块设计

智能数字电压表的控制核心CPLD的三个功能模块皆用VHDL语言编程实现,下面主要介绍CPLD的三个功能模块的设计。

3.1 A/D转换时序仿真模块AD_CONTROL

ANALOG DEVICES公司生产的AD7715是一片16位的∑-Δ ADC集成电路。它的主要特性有:3V/5V工作电压,单/双极性输入;可编程改变增益为1,2,32,128倍;在单极性输入状态下模拟电压输入范围允许为0~20mV, 0~80mV, 0~1.25V, 0~2.5V不等(有利于提高精度);三线串行接口;支持差分输入;低功耗(450 mF [email=Max@3V]Max@3V[/email])。在本系统中AD7715的作用是将0~2.5V的输入模拟信号转换为16位的高精度的数字信号供CPLD处理。AD_CONTROL模块用于控制AD7715的启动、读、写等操作。设计的AD_CONTROL模块如图2所示,其VHDL语言的ENTITY定义部分如下:

ENTITY AD_CONTROL IS

PORT(

SCLK:OUT STD_LOGIC;

DRDY:IN STD_LOGIC;

DOUT:OUT STD_LOGIC_VECTOR(15 DOWNTO 0);

DIN:IN STD_LOGIC_VECTOR(15 DOWNTO 0);

DB:OUT STD_LOGIC_VECTOR(15 DOWNTO 0);

CP:IN STD_LOGIC

);

END AD_CONTROL;

|

如图所示,二者的接口信号线直接连接并由AD_CONTROL模块模拟产生AD7715芯片的各个接口信号,完成ADC的启动、读、写操作。AD7715的工作模式由内部寄存器(Communications Register,Setup Register,Test Register,Data Register)中的控制字决定。内部寄存器的数据写入和读出都由CS,DRDY,SCLK信号控制。当 AD7715被访问时,SCLK脚应出现一次带上升沿的高电平,其时钟频率应为9.2kHz。这是关键信号,其他信号均以此信号作为时基。因此,CPLD中的AD_CONTROL模块的功能之一就是提供SCLK 以及其他信号的严格时序。图3、图4分别为AD_CONTROL模块读、写AD7715时序图。

|

3. 2 码制变换模块DATA_CONVERSION

在此码制变换模块DATA_CONVERSION中主要实现的功能是将AD采样送来的16位的二进制数转换为可被LED/LCD识别的七段LED显示码或字符型LCD码。在本系统中此模块包含了这两种转换功能以适应显示端不同的配置。为了达到这一目的,首先要将16位二进制码变换为BCD码,然后再分别进行转换,得到七段显示码及字符型码。在此模块中各个BLOCK部分的码制变换的VHDL程序可通过WHEN-ELSE语句进行查表来实现。转换的过程如图5所示。

|

3.3 显示控制及驱动模块DISL_DRIVE

电压值的显示可由LED或LCD实现。在本系统中对于电压值的显示分为mV和V两档,所以需要在后面加上单位来明确,且本系统为低功耗系统,若用LED则功耗相对过大,所以选用了一块8×2字符型液晶显示模块MDSL81809-03,实现了低功耗,而且可带单位双排显示,字体美观大方。 DISL_DRIVE示,整个电路十分简洁。系统工作过程首先由 CPLD对AD7715及LCD进行初始化,然后当有输入信号V i(0~2.5V)到AIN+端后,由CPLD通过接口向AD7715的寄存器中写入控制字,使其对输入的模拟信号进行转换,变为16位的数字信号送到DOUT端,由CPLD经过码制变换等处理后,再通过与LCD的接口驱动并发送数据,将电压值及单模块与LCD的接口如图6所示。图中LCD的RS端需输入方波驱动,这可由CPLD编程提供。当AD7715采样完成后,由DATA_CONVERSION模块将采样数字信号转换为LCD可识别的字符型数据后,送至DISL_DRIVE模块,再由其驱动LCD,将字符型数据送到LCD的D0~D7端,实现显示。

CPLD 电压 单片机 LED LCD 电路 VHDL 仿真 ADC 集成电路 LTE EDA 相关文章:

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)

- Virtex-5推动超宽带通信和测距的发展(01-06)