基于CPLD的I2C总线接口设计

时间:03-22

来源:互联网

点击:

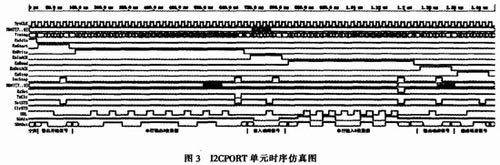

2.6 12CPORT单元

本单元是整个设计的核心,用于完成数据的I2C总线输出以及I2C总线输入数据的读入。同时产生接口模块的各种工作状态。

该单元的工作过程为:在SysCLK的下降沿分别读入工作使能信号和工作时序信号,如果此时EnIdle=‘1’则强制I2C总线进入空闲模式;如果EnStart=‘1’,则使I2C总线输出开始信号;如果EnWrite=‘1’,则使I2C总线输出8位数据信号;如果EnInACK=‘1’,则从I2C总线读入从机响应信号;如果EnRead=‘1’,则从I2C总线读入8位数据;如果EnOutACK=‘1’。则使I2C总线输出主机响应信号;如果EnStop=‘1’,则使I2C总线输出结束信号;在整个工作过程中,模块会自动根据工作情况,设置各种状态控制信号。

图3是用QuartusII9.0对该单元仿真的时序图。

2.7 PcPort单元的实现

该单元是模块与CPU的接口,CPU通过该单元向接口模块写入工作模式控制信息、需要发送的数据以及I2C工作速度控制信息;同时通过该单元读入从机响应信息、从机输出数据、发送接收寄存器状态等信息。

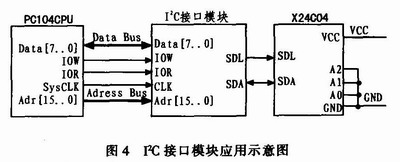

3 应用实例

该模块工作于主模式,主要应用于没有I2C专用接口的CPU通过并口方便地与具有I2C接口的外设连接并交换信息。

图4给出了CPU通过该模块与X24C04E2PROM接口的例子。

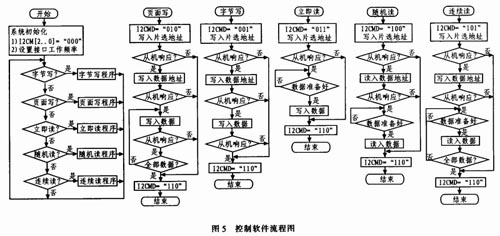

在图中,PC104 CPU通过数据总线、地址总线、读、写信号线与I2C接口模块相连,I2C接口模块则通过SDL、SDA与X24C04相连,PC104CPU输出的并行数据,经过I2C接口模块转换后变成符合I2C总线模式要求的串行数据输出到X24C04,X24C04输出的串行数据经过I2C接口模块转换后,变成并行数据供PC104CPU读取。使用该模块后CPU操作I2C总线就像操作并口一样方便。该电路的控制软件流程如图5所示。

通过上述应用实例可以看出,本文设计的接口模块只能工作于主机模式,并且在整个系统中只能有一个主机工作。在从机因处理其他工作而暂不能响应主机时,模块没有设计等待功能,只能发送总线结束信号结束当前操作,待从机空闲时再重新开始通信。

4 结论

本设计的创新点在于:通过CPLD实现并口到I2C总线接口的转换,可以使不具备I2C总线接口的CPU通过并口方便地控制I2C总线设备,使用该模块可以简化控制软件的编程,加快系统设计的实现,在I2C总线操作过程中,转换模块自动发出开始信号、结束信号,不需要CPU干预。

本文设计的I2C接口模块只能工作于主模式,只能应用于主机系统;在模块的设计中,没有考虑多主机的情况,对多主机的总线竞争没有设计仲裁功能;模块的页面读写数据数不能超过32个字节,在32个字节之内,CPU可以通过主动设置工作模式为“110”而终止当前操作,达到连续读写小于32个字节数据的目的,超过32个字节的连续数据读写操作将使模块工作错误。

总线 滤波器 电容 电路 CPLD Quartus 仿真 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA 重复配置和测试的实现(08-14)

- 经I/O优化的FPGA(04-23)

- 基于Actel FPGA的PWM IP的应用(09-17)