基于FPGA和DSP的音频采集卡的实现

时间:12-21

来源:互联网

点击:

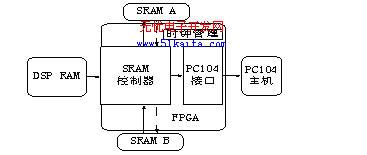

图2

4 DSP硬件和软件设计

4.1 DSP的硬件设计

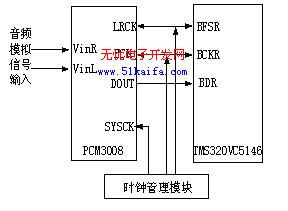

DSP采用McBSP与音频CODEC通信,系统框图(双路音频接收框图)如图3所示,McBSP依靠三个信号实现接收数据:数据线DR、帧同步线FSR和移位时钟线CLKR。DR引脚完成从音频CODEC中接收音频数据,由CLKR、FSR实现时钟和帧同步的控制。接收数据时,来自DR引脚的数据在FSR和CLKR作用下,从数据寄存器DRR中读出数据。

CLKR、FSR既可以由内部采样率发生器产生,也可以由外部设备驱动。该音频系统中,CLKR、FSR信号均来自于FPGA。

为了减轻CPU负担,音频数据的传递采用了DMA机制。 TMS320VC5416有6个可独立编程的DMA通道,每个DMA通道受各自的5个16位寄存器控制:源地址寄存器DMSRC、目的地址寄存器DMDST、单元计数寄存器DMCTR、同步事件和帧计数寄存器DMSFC、发送模式控制寄存器DMMCR。

通过设置DMA1通道与McBSP1通道结合来读取PCM3008转换完的数据为例:选择McBSP1通道的接收寄存器DRR11(41h)为DMA传送数据的首地址,并选择源地址工作在访问后不调整方式,选择DMA通道同步事件McBSP1接收事件为DMA同步事件,来实现DMA和McBSP的结合。PCM3008转换完的数据按McBSP1的设置被送到TMS320VC5416内部接收寄存器DRR11中,再由DMA将DRR11中的数读到指定数据存储区来完成数据采集。DMA在传送外部来的数据时不会影响CPU的正常运行,当DMA采集完一组规定个数的数据后产生一个DMA中断事件中断CPU,来通知CPU对其进行相应的处理,此时DMA可以按照设定继续采集下一组数据,实现了数据采集与CPU处理的并行操作。

图3

4.2 软件设计流程

程序流程如图4所示,系统上电后首先初始化CPU,McBSP,DMA寄存器,然后打开中断,当所有DMA的传输完成后,给出一个状态标志,通知CPU音频数据准备好,CPU将原始的音频数据集中在一个缓存中并开始调用音频处理算法依次处理每路音频数据,并将处理后的音频数据通过总线发送出去。然后继续等待处理下一帧音频数据,周而复始。

图4

4.3 音频压缩算法

由于该系统音频所要求的信号频率的范围是150hz-6000hz,因此必须采用一种宽频音频算法,我们设计了一种宽带语音编码。码率24kbps~64Kbps可变。其主要参数如表1:表1 音频编码的主要参数

参数 | 数值 |

音频采样率 | 16Khz |

比特率 | 24Kbps~64Kbps |

音频带宽 | 50Hz-7Khz |

音频帧长 | 20ms |

算法延迟 | 40ms |

RAM(定点) | <7.5KB |

ROM | ~20KB |

MI/s | ~15 |

5 结论

本文设计的多通道音频采集卡可以实现8路麦克风信号,2路VHF(甚高频)信号的采集与处理。24小时生成的数据量不足1.6GB,并且声音质量满足IEC 61996-2中关于音频要求的指标,该多通道音频采集卡已经成功地应用到船载航行数据记录仪中,并且通过了中国船级社(CCS)的检验,装配该多通道音频采集卡的VDR系统已经投入实用。

本文作者创新点:采用了自主的音频编码算法设计,并用DSP芯片实现,在数据存储和读取上采用了巧妙的乒乓设计。

FPGA DSP Altera ADC DAC 电压 滤波器 电路 Quartus MIPS 总线 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)