基于FPGA和DSP的音频采集卡的实现

时间:12-21

来源:互联网

点击:

1 引言

一个多通道数字音频系统必须考虑两个问题:采集到声音的质量问题和最终数字化后的音频存储的问题。由奈奎斯特定理知,如果要保证把采集到的音频信号完全无失真的恢复出来,采样率就必须至少是需采集音频信号频宽的2倍。由于现在大多数音频CODEC采用了Delta-Sigma Modulator,在保证采样率合适的情况下,声音质量一般是可以满足要求的。在船舶航行记录仪中,音频的频宽是150hz-6000hz,因此我们可以采用16khz的采样率和16位的量化位数。

按照这样的采样率,单路的音频码率为256kbps,24小时音频的数据量就高达2.76GB。为了减少最终存储器的存储空间,需要对原始的音频数据进行压缩处理。一般来说有损压缩比无损压缩的压缩比要高的多,但是同时会造成音质的下降。系统设计时应该进行适当的平衡。

本文设计的基于FPGA和DSP的多通道音频采集卡,采用Altera公司的Cyclone系列FPGA简化逻辑控制和提高硬件速度;采用TI公司的TMS320VC 5416实现音频压缩算法,在满足了音频性能指标的同时减少了最终的音频数据量,满足了系统的设计要求。

2 系统硬件结构

2.1主要芯片选型

(1) 音频CODEC芯片PCM3008

在音频CODEC芯片的选型上采用了Texas Instruments公司的PCM3008。这款音频CODEC芯片采用了16bit的△-∑ADC和DAC。其中立体声ADC具有单端电压输入,内置抗混叠滤波器。优异的性能还表现在其ADC的总谐波失真加噪声低至-84dB,信噪比高达88dB,动态范围至88dB,其内置的1/64 Decimation数字滤波器使得信号在通带内波动仅有0.05dB,阻带衰减可至-65dB。低压工作,低功耗。其采样率为8khz-48khz可选。数据传输为同步串口方式,操作方便。

(2)FPGA芯片EP1C6Q240

FPGA采用Altera公司的Cyclone系列的 EP1C6Q240实现各器件的接口控制。Cyclone系列的FPGA是Altera公司针对低成本高性能的应用而推出的,具有很高的性价比。

EP1C6Q240的最大可用IO数量185;片内92Kbit的RAM可以配为单双口RAM,ROM,FIFO等各式存储模块;两个高精度锁相环,方便地为片内的各个模块提供所需时钟;5980个LE(逻辑单元),为接口电路的实现提供丰富的逻辑资源。Altera公司的QuartusⅡ集成开发环境简便易用,内含大量IP核,其内嵌的Signal TapⅡ逻辑分析仪更是为用户的调试提供了很大方便。

(3)DSP芯片TMS320VC5416

DSP芯片采用TI公司的TMS320VC5416。TMS320VC5416是TI公司5000系列中高性能低功耗的定点DSP,它建立在C54x DSP核基础上。TMS320VC5416是一款16位定点高性能数字信号处理器, 其主要特性有: 速率最高达160MIPS; 3 条16位数据存储器总线和1条程序存储器总线; 1 个40位桶形移位器和2 个40位累加器; 1 个1717乘法器和1 个40位专用加法器; 最大8M 16位的扩展寻址空间, 内置128 k 16位的RAM 和16 k 16位的ROM; 3 个多通道缓冲串口(McBSP);其丰富的外设和强大的运算能力,使得TMS320VC5416可以进行实时的多路音频处理。在压缩的实现上,使用通用DSP芯片TMS320VC5416与使用专用的硬件压缩芯片相比,不仅可以节约成本,还可以方便地实现系统的升级和灵活的配置。

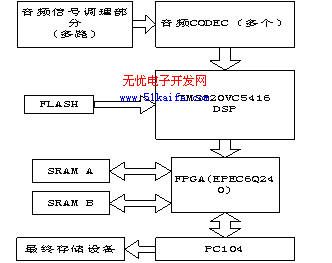

图1

2.2 系统设计思路

硬件结构设计如图1所示。多路音频信号首先通过调理部分,进入音频CODEC PCM3008,通过BCK,LRCK,DOUT三根信号线将音频数据送入DSP的 RAM内,DSP会按照一定的顺序将一帧音频数据整理好放在一个数据缓存里,并对其中的每路音频数据依次调用音频压缩算法,在下一帧音频数据到达该缓存区前将数据通过FPGA中的SRAM控制器发送到SRAM中,并告知PC104主机采集过程完毕。PC104主机通过FPGA内的PC104接口模块,将缓存SRAM中的数据读取出来。

3 FPGA的功能模块设计

FPGA的设计采用模块化的设计思想。主要模块按功能划分如图2所示。SRAM控制器采用了乒乓机制,一片处于读数据的状态,另一片处于写数据的状态,每15秒钟在PC104主机的控制下切换一次。这种操作方式时序设计简洁可靠,易于做到音频数据连续操作。收到PC104主机发出的切换命令后,待两片SRAM都处于空闲的时候,完成两片SRAM的读写切换。切换的同时,SRAM的读写的地址都会复位,而且会保存刚才15秒内的数据量信息,保证每个15秒读和写都是从零地址开始的,同时也方便读取数据。切换成功后,给出数据就绪的信号,指示主机可以读取数据。PC104接口模块负责采集卡与上位机的通讯和数据传输。

完成两片SRAM的读写切换。切换的同时,SRAM的读写的地址都会复位,而且会保存刚才15内的数据量信息,保证每个15秒读和写都是从零地址开始的,同时也方便读取数据。切换成功后,给出数据就绪的信号,指示主机可以读取数据。PC104接口模块负责采集卡与上位机的通讯和数据传输。

一个多通道数字音频系统必须考虑两个问题:采集到声音的质量问题和最终数字化后的音频存储的问题。由奈奎斯特定理知,如果要保证把采集到的音频信号完全无失真的恢复出来,采样率就必须至少是需采集音频信号频宽的2倍。由于现在大多数音频CODEC采用了Delta-Sigma Modulator,在保证采样率合适的情况下,声音质量一般是可以满足要求的。在船舶航行记录仪中,音频的频宽是150hz-6000hz,因此我们可以采用16khz的采样率和16位的量化位数。

按照这样的采样率,单路的音频码率为256kbps,24小时音频的数据量就高达2.76GB。为了减少最终存储器的存储空间,需要对原始的音频数据进行压缩处理。一般来说有损压缩比无损压缩的压缩比要高的多,但是同时会造成音质的下降。系统设计时应该进行适当的平衡。

本文设计的基于FPGA和DSP的多通道音频采集卡,采用Altera公司的Cyclone系列FPGA简化逻辑控制和提高硬件速度;采用TI公司的TMS320VC 5416实现音频压缩算法,在满足了音频性能指标的同时减少了最终的音频数据量,满足了系统的设计要求。

2 系统硬件结构

2.1主要芯片选型

(1) 音频CODEC芯片PCM3008

在音频CODEC芯片的选型上采用了Texas Instruments公司的PCM3008。这款音频CODEC芯片采用了16bit的△-∑ADC和DAC。其中立体声ADC具有单端电压输入,内置抗混叠滤波器。优异的性能还表现在其ADC的总谐波失真加噪声低至-84dB,信噪比高达88dB,动态范围至88dB,其内置的1/64 Decimation数字滤波器使得信号在通带内波动仅有0.05dB,阻带衰减可至-65dB。低压工作,低功耗。其采样率为8khz-48khz可选。数据传输为同步串口方式,操作方便。

(2)FPGA芯片EP1C6Q240

FPGA采用Altera公司的Cyclone系列的 EP1C6Q240实现各器件的接口控制。Cyclone系列的FPGA是Altera公司针对低成本高性能的应用而推出的,具有很高的性价比。

EP1C6Q240的最大可用IO数量185;片内92Kbit的RAM可以配为单双口RAM,ROM,FIFO等各式存储模块;两个高精度锁相环,方便地为片内的各个模块提供所需时钟;5980个LE(逻辑单元),为接口电路的实现提供丰富的逻辑资源。Altera公司的QuartusⅡ集成开发环境简便易用,内含大量IP核,其内嵌的Signal TapⅡ逻辑分析仪更是为用户的调试提供了很大方便。

(3)DSP芯片TMS320VC5416

DSP芯片采用TI公司的TMS320VC5416。TMS320VC5416是TI公司5000系列中高性能低功耗的定点DSP,它建立在C54x DSP核基础上。TMS320VC5416是一款16位定点高性能数字信号处理器, 其主要特性有: 速率最高达160MIPS; 3 条16位数据存储器总线和1条程序存储器总线; 1 个40位桶形移位器和2 个40位累加器; 1 个1717乘法器和1 个40位专用加法器; 最大8M 16位的扩展寻址空间, 内置128 k 16位的RAM 和16 k 16位的ROM; 3 个多通道缓冲串口(McBSP);其丰富的外设和强大的运算能力,使得TMS320VC5416可以进行实时的多路音频处理。在压缩的实现上,使用通用DSP芯片TMS320VC5416与使用专用的硬件压缩芯片相比,不仅可以节约成本,还可以方便地实现系统的升级和灵活的配置。

图1

2.2 系统设计思路

硬件结构设计如图1所示。多路音频信号首先通过调理部分,进入音频CODEC PCM3008,通过BCK,LRCK,DOUT三根信号线将音频数据送入DSP的 RAM内,DSP会按照一定的顺序将一帧音频数据整理好放在一个数据缓存里,并对其中的每路音频数据依次调用音频压缩算法,在下一帧音频数据到达该缓存区前将数据通过FPGA中的SRAM控制器发送到SRAM中,并告知PC104主机采集过程完毕。PC104主机通过FPGA内的PC104接口模块,将缓存SRAM中的数据读取出来。

3 FPGA的功能模块设计

FPGA的设计采用模块化的设计思想。主要模块按功能划分如图2所示。SRAM控制器采用了乒乓机制,一片处于读数据的状态,另一片处于写数据的状态,每15秒钟在PC104主机的控制下切换一次。这种操作方式时序设计简洁可靠,易于做到音频数据连续操作。收到PC104主机发出的切换命令后,待两片SRAM都处于空闲的时候,完成两片SRAM的读写切换。切换的同时,SRAM的读写的地址都会复位,而且会保存刚才15秒内的数据量信息,保证每个15秒读和写都是从零地址开始的,同时也方便读取数据。切换成功后,给出数据就绪的信号,指示主机可以读取数据。PC104接口模块负责采集卡与上位机的通讯和数据传输。

完成两片SRAM的读写切换。切换的同时,SRAM的读写的地址都会复位,而且会保存刚才15内的数据量信息,保证每个15秒读和写都是从零地址开始的,同时也方便读取数据。切换成功后,给出数据就绪的信号,指示主机可以读取数据。PC104接口模块负责采集卡与上位机的通讯和数据传输。

FPGA DSP Altera ADC DAC 电压 滤波器 电路 Quartus MIPS 总线 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)