基于FPGA设计EnDat编码器数据采集后续电路

时间:01-29

来源:互联网

点击:

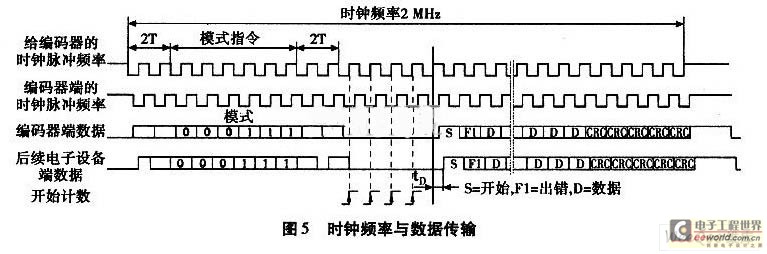

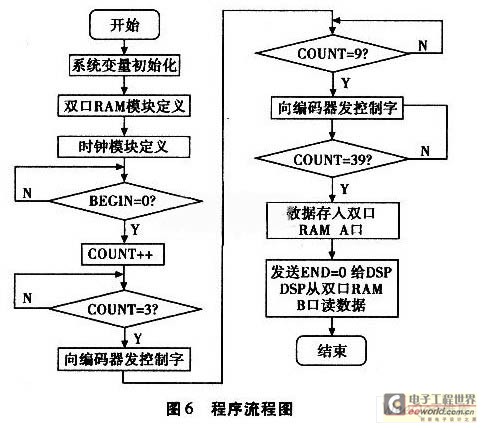

在FPGA内部实现了128 B的双口RAM空间,A口具有8位数据线,7位地址线,用于与编码器通讯,B口具有16位数据线,7位地址线,用于与DSP通讯,因为TMS320F2812为16位DSP,所以与FPGA中RAM的数据传递极为方便。DSP在每个电流环周期发送一个有效的“BEGIN”信号,19.5μs之后,码盘信号接收模块将接收到数据存入FPGA内部双口RAM的A口中,并按顺序排列成16位数据的形式,然后向DSP发送“END”信号,表示一次通讯结束,DSP接收到中断之后从FPGA的双口RAM的B口中读取数据,完成一次通讯。

对FPGA的开发采用XILINX公司的ISE集成环境,硬件描述语言为Verilog HDL语言。图6为程序流程图。

4 结束语

本文设计了一种基于FPGA的编码器接口,用以进行编码器和伺服驱动器DSP处理器之间的通讯,并且具有CRC校验等纠错功能。本文给出了硬件连接和FPGA程序设计流程,可以实现对永磁同步交流电机磁极位置准确的读取。

编码器 电子 机器人 电压 电流 电路 PWM Altera FPGA 总线 DSP Verilog 相关文章:

- 基于CPLD的开放式四轴运动控制器的设计(06-23)

- WCDMA速率适配算法的FPGA实现(07-11)

- 基于 FPGA 的 MPEG-4 编解码器(07-18)

- CPLD与绝对式编码器在高精度高速伺服单元中的应用(07-28)

- CPLD在射频卡读写器中的应用(08-02)

- 一种基于CPLD的曼彻斯特编解码器设计(08-06)