基于VHDL的16路可调速彩灯控制器设计

时间:12-28

来源:互联网

点击:

近年来,FPGA/CPLD发展迅速,随着集成电路制造工艺的不断进步,高性价比的FPGA/CPLD器件推陈出新,使FPGA/CPLD成为当今硬件设计的重要途径,与传统电路设计方法相比,FPGA/CPLD具有功能强大、开发周期短、投资少,便于追踪市场变化及时修改产品设计以及开发工具智能化等特点。在诸多FPGA/CPLD的设计语言中,VHDL语言作为一种主流的硬件描述语言,具有很强的电路描述和建模能力,能从多个层次对数字系统进行建模和描述,从而大大简化了硬件设计任务,提高了设计效率和可靠性,并在语言易读性和层次化、结构化设计方面,表现出了强大的生命力和应用潜力。

QuartusⅡ是Altera公司在21世纪初推出的FPGA/CPLD集成开发环境,是Altera公司前一代FPGA/CPLD集成开发环境Max+PlusⅡ的更新换代产品,其界面友好,使用便捷,功能强大,为设计者提供了一种与结构无关的设计环境,使设计者能方便的进行设计输入、快速处理和器件编程。

本文在QuartusⅡ开发环境下,用VHDL语言设计了一种可用于控制16路彩灯,具有4种彩灯变换模式,且变换速度可调的彩灯控制器。

1 16路可调速彩灯控制嚣设计思路

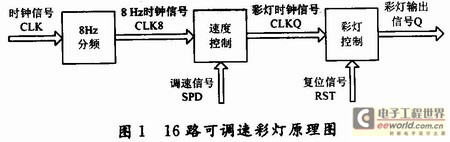

16路可调逮彩灯控制器根据功能可分为3个部分,如图1所示。其中,8 Hz分频部分用于对频率为10 MHz的时钟信号进行分频,获得频率为8 Hz的时钟信号CLK8。CLK8作为速度控制部分的基准时钟,通过计数分频方式又可获得频率分别为4 Hz,2 Hz和1 Hz的时钟信号,然后由调速信号选择其中之一作为彩灯时钟信号CLKQ,CLKQ即为彩灯控制部分的基准时钟,用于决定彩灯变换的速度,由此实现调速信号SPD对彩灯变换速度的控制,使彩灯可调速。

彩灯控制部分通过输出1个16位二进制数(即彩灯输出信号Q)来控制16个彩灯,每一位二进制数对应1个彩灯的开关,当该位数字为“1”时灯亮,该位数字为“O”时灯灭。彩灯的变换共设置4种模式:

sO模式:只亮1个灯,从最左端逐个移动到最右端,即输出信号Q从第15位开始将1个“1”依次移动到第0位;

s1模式:只亮1个灯,从最右端逐个移动到最左端,即输出信号Q从第0位开始将1个“1”依次移动到第15位;

s2模式:亮2个灯,同时从左右两端向中间移动,即输出信号Q从第15位开始将1个“1”依次移动到第8位,同时从第O位开始将1个“1”依次移动到第7位;

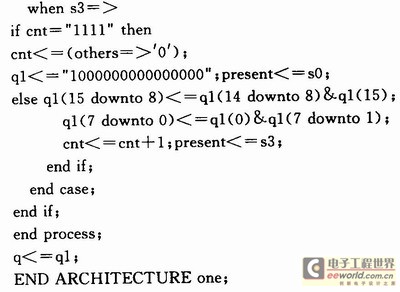

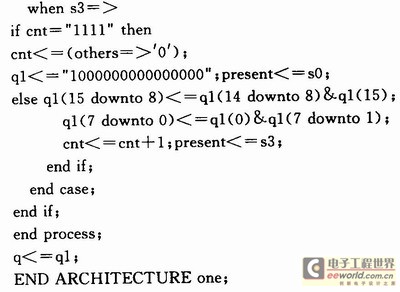

s3模式:亮2个灯,同时从中间向左右两端移动,即输出信号Q从第8位开始将1个“1”依次移动到第15位,同时从第7位开始将1个“1”依次移动到第0位。

四种模式依次循环,若复位信号RST输入为高电平,则循环中断,输出信号Q置零,彩灯全灭,RST恢复为低电平后,再次从sO模式开始循环。

2 16路可调速彩灯控制器的实现

本文所设计的16路可调速彩灯控制器,其电路符号如图2所示,其中clk为10 MHz时钟信号输入端,rst为复位控制端,spd为调速信号输入端,q为彩灯控制信号输出端。

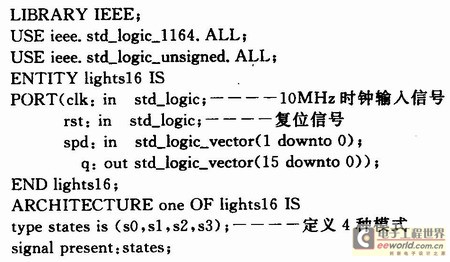

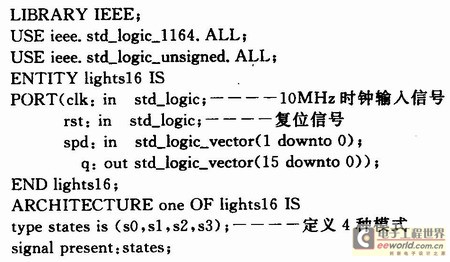

本文所设计的16路可调速彩灯控制器的VHDL代码如下所示:

值得注意的是,本文设计的16路可调速彩灯控制器使用了数据循环算法,较以往的case when语句,更加简洁,实现的功能更加强大,其具有如下特点:

(1)在硬件验证时,将速度控制端spd的pin脚接到拨码开关上,从而实现彩灯变换速度快慢的手动控制,在更进一步的设计中,也可以通过对spd信号的内部控制,实现各种变换速度的自动调整。

(2)该设计采用数据移位的方式实现彩灯的变换,更有利于彩灯变换模式的扩展。该设计虽然只设计了4种变换模式,但可以根据需要轻松的扩展至6~8种模式,甚至更多。

(3)8 Hz分频部分的分频比很大,不适于计算机仿真验证,在仿真时需要调小分频比,在硬件验证时再恢复较大的分频比。

3 仿真结果分析

本文设计的16路可调速彩灯控制器在QuartusⅡ开发环境下进行了仿真验证,仿真波形如图3所示。仿真结果分析如下:

(1)clk为时钟信号,由时钟信号的上升沿触发分频器计数;

(2)rst为复位信号输入端,当其为高电平时,彩灯控制输出信号q清零,rst恢复为低电平后彩灯控制输出信号q从sO模式重新开始循环;

(3)spd为调速信号输入端,对应于spd的“00”,“01”,“10”,“11”这4个数值,彩灯变换的速度分别为1 Hz,2 Hz,4 Hz,8 Hz;

(4)q为彩灯控制信号输出端,由图3可知,该设计成功地实现了4种变换模式的循环和各种变换速度的调节。

4 结语

设计的16路可调速彩灯控制器在QuartusⅡ开发环境下进行了仿真验证后,下载到湖北众友科技实业股份有限公司的ZYllEDAl3BE实验箱中进行了硬件验证,该实验箱使用ACEXlK系列EPlK30QC208芯片作为核心芯片,实验证明设计正确,功能完整,运行稳定。另外,本文所设计的16路可调速彩灯控制器可根据需要增加更多的变换模式,使彩灯更加绚丽多姿。

QuartusⅡ是Altera公司在21世纪初推出的FPGA/CPLD集成开发环境,是Altera公司前一代FPGA/CPLD集成开发环境Max+PlusⅡ的更新换代产品,其界面友好,使用便捷,功能强大,为设计者提供了一种与结构无关的设计环境,使设计者能方便的进行设计输入、快速处理和器件编程。

本文在QuartusⅡ开发环境下,用VHDL语言设计了一种可用于控制16路彩灯,具有4种彩灯变换模式,且变换速度可调的彩灯控制器。

1 16路可调速彩灯控制嚣设计思路

16路可调逮彩灯控制器根据功能可分为3个部分,如图1所示。其中,8 Hz分频部分用于对频率为10 MHz的时钟信号进行分频,获得频率为8 Hz的时钟信号CLK8。CLK8作为速度控制部分的基准时钟,通过计数分频方式又可获得频率分别为4 Hz,2 Hz和1 Hz的时钟信号,然后由调速信号选择其中之一作为彩灯时钟信号CLKQ,CLKQ即为彩灯控制部分的基准时钟,用于决定彩灯变换的速度,由此实现调速信号SPD对彩灯变换速度的控制,使彩灯可调速。

彩灯控制部分通过输出1个16位二进制数(即彩灯输出信号Q)来控制16个彩灯,每一位二进制数对应1个彩灯的开关,当该位数字为“1”时灯亮,该位数字为“O”时灯灭。彩灯的变换共设置4种模式:

sO模式:只亮1个灯,从最左端逐个移动到最右端,即输出信号Q从第15位开始将1个“1”依次移动到第0位;

s1模式:只亮1个灯,从最右端逐个移动到最左端,即输出信号Q从第0位开始将1个“1”依次移动到第15位;

s2模式:亮2个灯,同时从左右两端向中间移动,即输出信号Q从第15位开始将1个“1”依次移动到第8位,同时从第O位开始将1个“1”依次移动到第7位;

s3模式:亮2个灯,同时从中间向左右两端移动,即输出信号Q从第8位开始将1个“1”依次移动到第15位,同时从第7位开始将1个“1”依次移动到第0位。

四种模式依次循环,若复位信号RST输入为高电平,则循环中断,输出信号Q置零,彩灯全灭,RST恢复为低电平后,再次从sO模式开始循环。

2 16路可调速彩灯控制器的实现

本文所设计的16路可调速彩灯控制器,其电路符号如图2所示,其中clk为10 MHz时钟信号输入端,rst为复位控制端,spd为调速信号输入端,q为彩灯控制信号输出端。

本文所设计的16路可调速彩灯控制器的VHDL代码如下所示:

值得注意的是,本文设计的16路可调速彩灯控制器使用了数据循环算法,较以往的case when语句,更加简洁,实现的功能更加强大,其具有如下特点:

(1)在硬件验证时,将速度控制端spd的pin脚接到拨码开关上,从而实现彩灯变换速度快慢的手动控制,在更进一步的设计中,也可以通过对spd信号的内部控制,实现各种变换速度的自动调整。

(2)该设计采用数据移位的方式实现彩灯的变换,更有利于彩灯变换模式的扩展。该设计虽然只设计了4种变换模式,但可以根据需要轻松的扩展至6~8种模式,甚至更多。

(3)8 Hz分频部分的分频比很大,不适于计算机仿真验证,在仿真时需要调小分频比,在硬件验证时再恢复较大的分频比。

3 仿真结果分析

本文设计的16路可调速彩灯控制器在QuartusⅡ开发环境下进行了仿真验证,仿真波形如图3所示。仿真结果分析如下:

(1)clk为时钟信号,由时钟信号的上升沿触发分频器计数;

(2)rst为复位信号输入端,当其为高电平时,彩灯控制输出信号q清零,rst恢复为低电平后彩灯控制输出信号q从sO模式重新开始循环;

(3)spd为调速信号输入端,对应于spd的“00”,“01”,“10”,“11”这4个数值,彩灯变换的速度分别为1 Hz,2 Hz,4 Hz,8 Hz;

(4)q为彩灯控制信号输出端,由图3可知,该设计成功地实现了4种变换模式的循环和各种变换速度的调节。

4 结语

设计的16路可调速彩灯控制器在QuartusⅡ开发环境下进行了仿真验证后,下载到湖北众友科技实业股份有限公司的ZYllEDAl3BE实验箱中进行了硬件验证,该实验箱使用ACEXlK系列EPlK30QC208芯片作为核心芯片,实验证明设计正确,功能完整,运行稳定。另外,本文所设计的16路可调速彩灯控制器可根据需要增加更多的变换模式,使彩灯更加绚丽多姿。

FPGA CPLD 集成电路 电路 VHDL Quartus Altera 仿真 EDA 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)