基于nRF24L01和Actel FPGA的智能探测系统设计

时间:12-28

来源:互联网

点击:

设计了基于nRF24L01无线数据传输芯片和Fusion StartKit开发板的智能探测系统。通过开启nRF24L01的ACK PAYLOAD功能实现车载系统与上位机之间的双向通信,采用Actel公司带有APB3总线的8051S软核在Fusion StartKit开发板上构建片上系统,使用MFC编写Windows环境下的人机交互界面,实现了具有实时数据传送、自动避障、远程操控等功能的智能探测系统。

目前一些恶劣或危险的环境人类仍然无法置身其中进行现场检测,如出现险情的矿井地道、地形崎岖的岩洞等,很难取得现场的参数。在这种情况下只有借助于智能探测装置。因智能小车控制方便、行动灵活,对比其他载体工具更容易胜任探测任务,因此成为各种探测仪器的首选工具。

本文设计的智能探测系统以小车为载体,将所测得的现场参数通过nRF24L01无线模块实时传回上位机,具有快速灵活的特点;在实际工作时可左右转向和后退,自动躲避障碍物;同时该小车操控方便,可通过MFC搭建的人机交互界面利用鼠标和键盘对小车进行远程控制。

1、系统总体结构设计

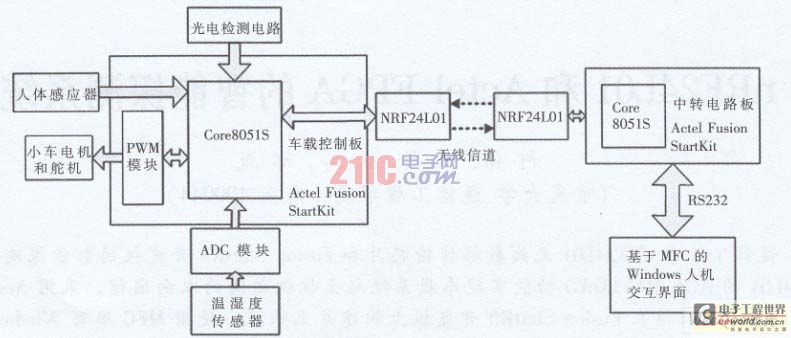

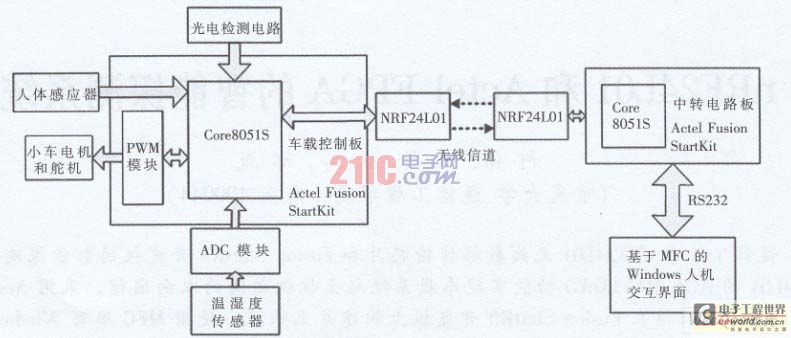

该系统基于Actel FPGA实现,采用两块Fusi。nStartkit开发板,一块作为车载控制板,另一块作为中转板。车载控制板负责采集温度、湿度、板载电压、当前路况以及人体检测等现场信息,驱动小车运行,同时通过无线发送现场信息以及接收上位机的控制命令。中转板负责将接收到的无线信号通过串口转发给PC机,同时将PC机由串口返回的控制指令利用无线模块发送给车载控制板。PC机上采用MFC编写人机交互界面,显示小车所在环境的相关信息,同时提供鼠标、键盘等完善的操控手段。系统结构如图1所示。

图1 系统结构框图

2、系统硬件设计

2、1无线数据传输芯片nRF24L01

2.1.1芯片简介H

nRF24L01是挪威NorDic公司的单片2.4 GHz无线收发一体芯片,有多达125个频道可供选择,支持1 Mb/s和2 Mb/s传输速率。该芯片采用SPI接口进行数据读写和参数配置,以寄存器映射方式对各个寄存器进行管理,同时具有自动重传、动态有效信息长度(DPL)、应答信号携带有效信息(ACK PAYLOAD)等高级功能。

2.1.2功能

动态有效信息长度(DPL)指的是发送端的nRF24L01芯片通过写人有效数据区的数据长度决定当前一帧数据的大小,而接收端则通过接收到的数据帧中的控制域信息而不是寄存器中定义的数据长度提取有效数据。这个功能极大地提高了无线信道的使用率,同时减少了冗余数据的传播,降低了数据在空中滞留的时间和数据被污染的概率。配合nRF24L0l的CRC校验和自动重传功能,在有效地降低数据误码率的同时保证了数据传输的时效性。

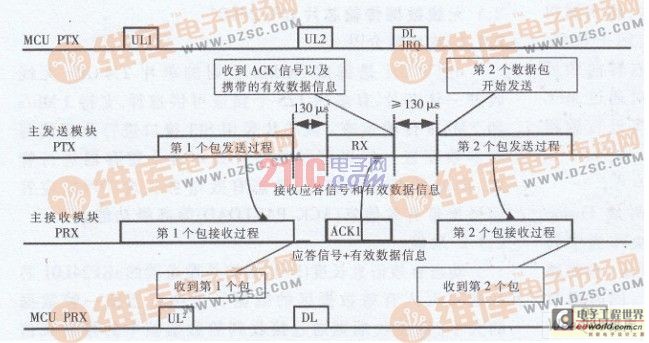

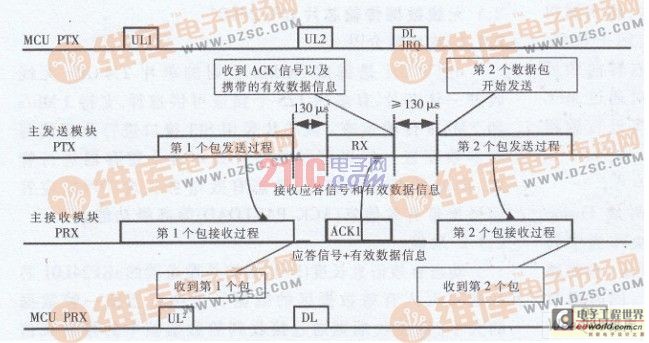

应答信号携带有效信息(ACK PAYLOAD)指nRF24L01芯片在开启自动重传和DPL的基础上实现的双向通信功能。图2为一对无线模块之间的一次携带应答有效信息的数据传输过程。主发送模块(PTX)发送完第1帧数据后,自动置为接收模式,等待主接收模块(PRX)发送应答信号或携带有效数据的应答信号。主接收模块收到主发送模块发送的第1个数据帧后,若此时有需要附加的有效数据,则在发送完ACK信号后继续发送有效数据。而主发送模块收到ACK信号后继续接收有效信号,直到空中没有残留的无线信号再开始发送第2帧信号。

使用ACK PAYLOAD可以实现车载系统和PC机的双向通信,该功能很好地解决了手动切换无线收发状态导致双方互相等待的问题,同时只在需要对车载控制板进行控制的时刻附带应答有效信息,可以减少不必要的通信过程,大大提高了系统稳定性。

图2携带ACK PAYLOAD的1次数据传输示意图

2.1.3实现功能的配置方法

要实现nRF24L01的ACK PAYLOAD功能需要经过以下步骤:首先进行无线模块的基本配置,包括发送接收模式的选择(CONFIG)、开启自动重传功能(EN_AA)、接收地址使能(EN_ADDR)、设置重传时问不为零(SET-UP RETR)等;然后同时开启DPL和ACK PAYLOAD功能,要实现这两个功能,必须在完成第一步之后用nRF24L01白带的ACTIVATE命令加上0x73数据开启默认隐藏的两个寄存器FEATURE和DYNPD。通过对这两个寄存器的设置就可以实现数据的双向通信。但要注意,接收端开启DPL后要使用R_RX PL WID命令读取当前数据帧的有效数据长度,同时使用W ACK PAY-LOAD命令将ACK PAYLOAD写入FIFO。

2.2 Core 80515架构

Core 8051S是Actel公司推出的基于APB3总线的8051lP核,兼容8051的全部指令,同时又具备许多51单片机所没有的独特功能:

(1)具有可配置的JTAG接口调试功能,可利用Flash_Pro下载器作为其调试工具;优化指令执行速度,内部设置流水线,可实现单个时钟周期执行一条指令,且是普通51单片机的12倍。

(2)采用APB3外设总线结构和SER寄存器内存映射方式管理外设,将外部扩展的64 KB数据空间中的最高4 KB作为APB3外设的寄存器内存映射地址,每个APB3外设占据256 B的地址,因此最多可添加16个外设。

(3)使用CoreConsole软件以图形化界面的方式添加Core8051S以及其他外设,既直观又方便。

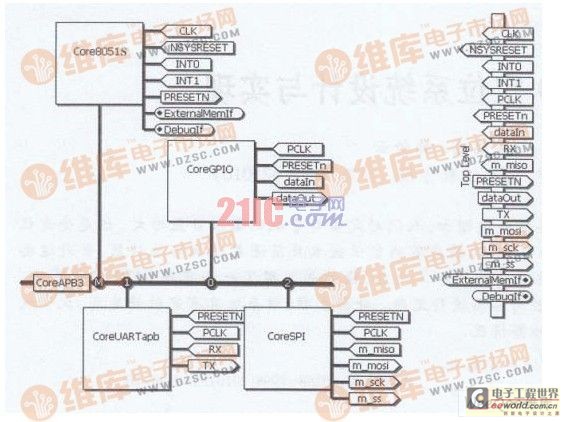

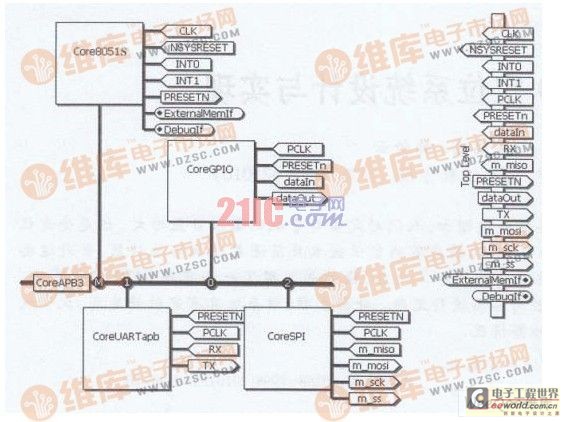

图3是以CoreConsole开发的、基于Core805lS和APB3总线的50PC系统的典型架构。该软件的开发流程与Altera公司基于NIOS Ⅱ处理器的soPc开发流程类似,同时又具有其独特优势:在系统不复杂、控制部分远多于计算处理时,使用Core805⊥s可灵活迅速地进行开发,通过安装ISA—Actel5 1为Keil提供调试驱动可直接使用Keil编写代码并进行在线程序调试,而优化后的指令执行速度可满足大部分应用的要求。

图3 CoreConsole下基于Core8051S的开发实例

本系统设计步骤:

(1)利用CoreConsole以图形化方式设计片上系统所需的总线及外设,包括SPI、PWM、GP10、UART等模块;配置各模块与APB3总线之间的连接关系,正确分配外设地址;然后生成.Ⅴ文件导人Actel集成开发环境Libero。

(2)使用Libero的Flash Memory System Builder将Fu_S10n内部的Flash模块配置为Core8051S的外部程序空问。如果有必要还可以将Fusi。n StartKit开发板上的SRAM作为Core8051S的外部数据空间使用。

(3)将工程编译综合后下载到开发板上,通过Keil编写程序并进行调试。

目前一些恶劣或危险的环境人类仍然无法置身其中进行现场检测,如出现险情的矿井地道、地形崎岖的岩洞等,很难取得现场的参数。在这种情况下只有借助于智能探测装置。因智能小车控制方便、行动灵活,对比其他载体工具更容易胜任探测任务,因此成为各种探测仪器的首选工具。

本文设计的智能探测系统以小车为载体,将所测得的现场参数通过nRF24L01无线模块实时传回上位机,具有快速灵活的特点;在实际工作时可左右转向和后退,自动躲避障碍物;同时该小车操控方便,可通过MFC搭建的人机交互界面利用鼠标和键盘对小车进行远程控制。

1、系统总体结构设计

该系统基于Actel FPGA实现,采用两块Fusi。nStartkit开发板,一块作为车载控制板,另一块作为中转板。车载控制板负责采集温度、湿度、板载电压、当前路况以及人体检测等现场信息,驱动小车运行,同时通过无线发送现场信息以及接收上位机的控制命令。中转板负责将接收到的无线信号通过串口转发给PC机,同时将PC机由串口返回的控制指令利用无线模块发送给车载控制板。PC机上采用MFC编写人机交互界面,显示小车所在环境的相关信息,同时提供鼠标、键盘等完善的操控手段。系统结构如图1所示。

图1 系统结构框图

2、系统硬件设计

2、1无线数据传输芯片nRF24L01

2.1.1芯片简介H

nRF24L01是挪威NorDic公司的单片2.4 GHz无线收发一体芯片,有多达125个频道可供选择,支持1 Mb/s和2 Mb/s传输速率。该芯片采用SPI接口进行数据读写和参数配置,以寄存器映射方式对各个寄存器进行管理,同时具有自动重传、动态有效信息长度(DPL)、应答信号携带有效信息(ACK PAYLOAD)等高级功能。

2.1.2功能

动态有效信息长度(DPL)指的是发送端的nRF24L01芯片通过写人有效数据区的数据长度决定当前一帧数据的大小,而接收端则通过接收到的数据帧中的控制域信息而不是寄存器中定义的数据长度提取有效数据。这个功能极大地提高了无线信道的使用率,同时减少了冗余数据的传播,降低了数据在空中滞留的时间和数据被污染的概率。配合nRF24L0l的CRC校验和自动重传功能,在有效地降低数据误码率的同时保证了数据传输的时效性。

应答信号携带有效信息(ACK PAYLOAD)指nRF24L01芯片在开启自动重传和DPL的基础上实现的双向通信功能。图2为一对无线模块之间的一次携带应答有效信息的数据传输过程。主发送模块(PTX)发送完第1帧数据后,自动置为接收模式,等待主接收模块(PRX)发送应答信号或携带有效数据的应答信号。主接收模块收到主发送模块发送的第1个数据帧后,若此时有需要附加的有效数据,则在发送完ACK信号后继续发送有效数据。而主发送模块收到ACK信号后继续接收有效信号,直到空中没有残留的无线信号再开始发送第2帧信号。

使用ACK PAYLOAD可以实现车载系统和PC机的双向通信,该功能很好地解决了手动切换无线收发状态导致双方互相等待的问题,同时只在需要对车载控制板进行控制的时刻附带应答有效信息,可以减少不必要的通信过程,大大提高了系统稳定性。

图2携带ACK PAYLOAD的1次数据传输示意图

2.1.3实现功能的配置方法

要实现nRF24L01的ACK PAYLOAD功能需要经过以下步骤:首先进行无线模块的基本配置,包括发送接收模式的选择(CONFIG)、开启自动重传功能(EN_AA)、接收地址使能(EN_ADDR)、设置重传时问不为零(SET-UP RETR)等;然后同时开启DPL和ACK PAYLOAD功能,要实现这两个功能,必须在完成第一步之后用nRF24L01白带的ACTIVATE命令加上0x73数据开启默认隐藏的两个寄存器FEATURE和DYNPD。通过对这两个寄存器的设置就可以实现数据的双向通信。但要注意,接收端开启DPL后要使用R_RX PL WID命令读取当前数据帧的有效数据长度,同时使用W ACK PAY-LOAD命令将ACK PAYLOAD写入FIFO。

2.2 Core 80515架构

Core 8051S是Actel公司推出的基于APB3总线的8051lP核,兼容8051的全部指令,同时又具备许多51单片机所没有的独特功能:

(1)具有可配置的JTAG接口调试功能,可利用Flash_Pro下载器作为其调试工具;优化指令执行速度,内部设置流水线,可实现单个时钟周期执行一条指令,且是普通51单片机的12倍。

(2)采用APB3外设总线结构和SER寄存器内存映射方式管理外设,将外部扩展的64 KB数据空间中的最高4 KB作为APB3外设的寄存器内存映射地址,每个APB3外设占据256 B的地址,因此最多可添加16个外设。

(3)使用CoreConsole软件以图形化界面的方式添加Core8051S以及其他外设,既直观又方便。

图3是以CoreConsole开发的、基于Core805lS和APB3总线的50PC系统的典型架构。该软件的开发流程与Altera公司基于NIOS Ⅱ处理器的soPc开发流程类似,同时又具有其独特优势:在系统不复杂、控制部分远多于计算处理时,使用Core805⊥s可灵活迅速地进行开发,通过安装ISA—Actel5 1为Keil提供调试驱动可直接使用Keil编写代码并进行在线程序调试,而优化后的指令执行速度可满足大部分应用的要求。

图3 CoreConsole下基于Core8051S的开发实例

本系统设计步骤:

(1)利用CoreConsole以图形化方式设计片上系统所需的总线及外设,包括SPI、PWM、GP10、UART等模块;配置各模块与APB3总线之间的连接关系,正确分配外设地址;然后生成.Ⅴ文件导人Actel集成开发环境Libero。

(2)使用Libero的Flash Memory System Builder将Fu_S10n内部的Flash模块配置为Core8051S的外部程序空问。如果有必要还可以将Fusi。n StartKit开发板上的SRAM作为Core8051S的外部数据空间使用。

(3)将工程编译综合后下载到开发板上,通过Keil编写程序并进行调试。

总线 FPGA 电压 单片机 51单片机 Altera Keil PWM 传感器 红外 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA 重复配置和测试的实现(08-14)

- 经I/O优化的FPGA(04-23)

- 基于Actel FPGA的PWM IP的应用(09-17)