基于FPGA的多路数字量采集模块设计

时间:12-07

来源:互联网

点击:

4.1 频率信号采集

由于频率信号只需体现出其频率大小即可,因此采集频率信号时只记录该信号两沿间的时间。即就是设定一个16位的计数器T,计数器的值随主时钟累加,当判断到该信号有变化时,就将计数器的值T1送人缓存,然后将该计数器清零。计数器的值继续累加,直到该信号下一次变化,再将计数器的值T2送入缓存,计数器再清零,以此类推,来记录该信号两沿间的时间。

4.2 脉冲信号采集

采集脉冲信号需记录该信号的脉宽以及相对于同步信号的延迟。记录方法是:使用一个单独的进程,定义一个24位的计数器TB,当同步信号的上升沿到来时开始计数,当同步信号的下一个上升沿到来时,该计数器清零。另一个进程判断15路脉冲信号中有一路信号变化时,将当前计数器TB的值送人缓存,并将当前所有脉冲信号的电平状态都送入缓存。

4.3 数据的编帧和解帧

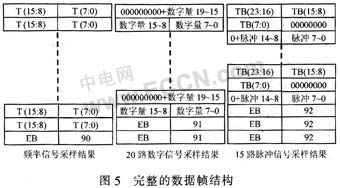

在数据采集部分中,当同步信号的上升沿到来时,将3个帧标志分别写入3个缓存,频率信号数据的帧标志为EB90;20路数字信号的帧标志为2个EB91;15路脉冲信号数据的帧标志为3个EB92。读取数据模块中,当同步信号的下降沿到来时,开始读取缓存的数据送至外部FIFO,并判断当读取一个EB90后,开始读取缓存的数据,并送入外部FIFO;当读到两个EB91后,读取缓存的数据,并送入外部FIFO;当读到3个EB92后表明一帧数据读取完毕,等待下一个同步信号的下降沿后再开始读取下一帧数据。由于外部FIFO是16位,所以数据中不满16位的都用0将数据补充完整,完整的数据帧结构如图5所示。

上位机收到一帧数据后进行解帧处理,对于频率信号数据,将这些T值相加并求平均得出T’,再乘以2,由于系统时钟是120 MHz,所以2T’/120为频率信号周期(μs级),然后求倒数即可得出该信号的频率值。

20路数字量信号数据直接显示其电平状态。脉冲信号数据则先判断哪一路(多路)脉冲信号发生变化,再判断该信号(几路信号)的电平状态。若为高电平,则对应的时间应为TBa;若为低电平,则对应的时间应为TBb。TBa即为该脉冲信号相对于同步信号的延迟,而TBb-TBa的值即为该脉冲信号的正脉冲脉宽。

5 结束语

针对测控系统监测信号数量较多的问题,提出了一种基于FPGA的多路数字量采集与处理模块,设计了相应的电路和FPGA逻辑。在综合调试成功的基础上,该多路数字量采集模块已成功应用于某测试系统。

由于频率信号只需体现出其频率大小即可,因此采集频率信号时只记录该信号两沿间的时间。即就是设定一个16位的计数器T,计数器的值随主时钟累加,当判断到该信号有变化时,就将计数器的值T1送人缓存,然后将该计数器清零。计数器的值继续累加,直到该信号下一次变化,再将计数器的值T2送入缓存,计数器再清零,以此类推,来记录该信号两沿间的时间。

4.2 脉冲信号采集

采集脉冲信号需记录该信号的脉宽以及相对于同步信号的延迟。记录方法是:使用一个单独的进程,定义一个24位的计数器TB,当同步信号的上升沿到来时开始计数,当同步信号的下一个上升沿到来时,该计数器清零。另一个进程判断15路脉冲信号中有一路信号变化时,将当前计数器TB的值送人缓存,并将当前所有脉冲信号的电平状态都送入缓存。

4.3 数据的编帧和解帧

在数据采集部分中,当同步信号的上升沿到来时,将3个帧标志分别写入3个缓存,频率信号数据的帧标志为EB90;20路数字信号的帧标志为2个EB91;15路脉冲信号数据的帧标志为3个EB92。读取数据模块中,当同步信号的下降沿到来时,开始读取缓存的数据送至外部FIFO,并判断当读取一个EB90后,开始读取缓存的数据,并送入外部FIFO;当读到两个EB91后,读取缓存的数据,并送入外部FIFO;当读到3个EB92后表明一帧数据读取完毕,等待下一个同步信号的下降沿后再开始读取下一帧数据。由于外部FIFO是16位,所以数据中不满16位的都用0将数据补充完整,完整的数据帧结构如图5所示。

上位机收到一帧数据后进行解帧处理,对于频率信号数据,将这些T值相加并求平均得出T’,再乘以2,由于系统时钟是120 MHz,所以2T’/120为频率信号周期(μs级),然后求倒数即可得出该信号的频率值。

20路数字量信号数据直接显示其电平状态。脉冲信号数据则先判断哪一路(多路)脉冲信号发生变化,再判断该信号(几路信号)的电平状态。若为高电平,则对应的时间应为TBa;若为低电平,则对应的时间应为TBb。TBa即为该脉冲信号相对于同步信号的延迟,而TBb-TBa的值即为该脉冲信号的正脉冲脉宽。

5 结束语

针对测控系统监测信号数量较多的问题,提出了一种基于FPGA的多路数字量采集与处理模块,设计了相应的电路和FPGA逻辑。在综合调试成功的基础上,该多路数字量采集模块已成功应用于某测试系统。

MCU FPGA VHDL 电路 USB 单片机 电压 电流 电路图 二极管 IDT Xilinx 相关文章:

- 我的FPGA学习历程(05-23)

- FPGA设计学习经验小谈(05-23)

- 在单个FPGA平台上采用多种工业以太网标准进行设计(03-13)

- FPGA的在应用编程技术研究(04-24)

- 基于CPLD与单片机的高速数据采集系统(04-08)

- Actel数模结合FPGA的远程控制器设计(05-13)