基于FPGA的多路数字量采集模块设计

时间:12-07

来源:互联网

点击:

1 引言

测控系统常常需要处理所采集到的各种数字量信号。通常测控系统采用通用MCU完成系统任务。但当系统中采集信号量较多时,仅依靠MCU则难以完成系统任务。针对这一问题,提出一种基于FPGA技术的多路数字量采集模块。利用FPGA的I/O端口数多且可编程设置的特点,配以VHDL编写的FPGA内部逻辑,实现采集多路数字量信号。

2 模块设计方案

2.1 功能要求

该数字量采集模块主要功能是采集输入的36路数字及脉冲信号,并将编帧后的信号数据上传给上位机,上位机经解包处理后显示信号相应的状态进行判断。

根据设计要求,所测量的36路数字信号中,有15路正脉冲信号。它们均由一个同步脉冲信号触发,因此需要测量这些正脉冲的宽度和相对于同步信号脉冲的延时。

要求采集步长不能大于10 ns,即采集频率高于100 MHz。而其他数字信号需要显示高低电平状态,其中一路信号是固定频率信号,需测量其频率值。上位机要求显示所采集信号的状态。

2.2 模块原理框图

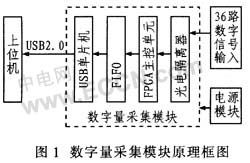

FPGA内部逻辑功能强大,外围电路设计基于简单、可靠的原则。该模块由FIFO、USB2.0单片机、光电隔离器等部分组成。36路数字信号经光电隔离器进入FPGA主控单元,以供采集;FPGA处理采集到的信号,转换成数据进行编帧,然后写入FIFO。USB单片机提取FIFO中的数据,通过USB电缆传送给上位机,上位机将传送来的数据解帧,然后显示所有信号状态。模块通过电源接口向各个部分供电。其原理框图如图1所示。

3 模块电路设计

3.1 FPGA配置电路

FPGA是采用XILINX公司的Spantan-II系列XC2S100E,该系列器件的内核采用2.5 V供电,工作频率高达200 MHz;I/O端口供电电压为3.3 V,可承受5 V的输入高电平。Spartan-II系列的FPGA具有丰富的I/O端口资源。其I/O端口输出缓冲器接收高达24 mA源出电流和48 mA灌入电流。

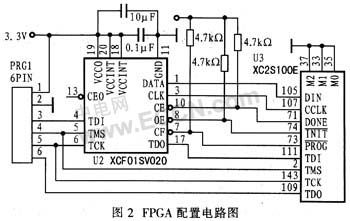

由于FPGA基于RAM工艺技术,掉电后不能保存信息,因此需要

一个外置存储器来保存信息。采用一次可编程的PROM(高有效或低有效)XCF01SV020,其复位引脚的极性可编程设置,供电电压为3.3 V。

XCF01SVO20的DONE、INIT、CCLK信号来自于FPGA XC2S100E。系统上电后,首先FPGA初始化,INIT、DONE置低。INIT置低后复位PROM,此时由于PROM的CE为低,因此选取PROM,从而可将数据流从DATA引脚输入到FPGA的DIN引脚。配置完成后,FPGA将DONE接高,PROM处于低功耗的待机模式,并将DATA引脚置为高阻态。图2为FPGA配置电路图。

3.2 光电隔离电路

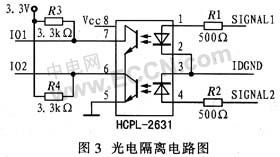

采用高速光电耦合器HCPL-2631,其开关频率高达10 MHz,而输人数字信号频率为120 kHz,完全满足要求。由于光电耦合器件以光为媒介传输信息,可使输入输出隔离,由于光电耦合器的输入回路为发光二极管,其输入阻抗很小,而干扰源的内阻较大,根据分压原理可知,馈送到光电耦合器输入端的噪声干扰电压变得很小,从而能有效抑制尖峰脉冲及各种噪声干扰,具有较强的抗干扰性能;另外由于光电隔离器的两端采用不同的接地方式,因此数字信号地和模块地被完全隔离。图3为光电隔离电路图。

3.3 FIFO电路

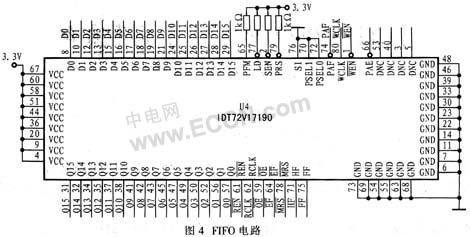

FIFO电路采用IDT公司的IDT72V17190器件,该器件采用3.3 V电压供电,16位64 KB容量的FIFO,工作时钟高达100 MHz。如图4所示,FIFO的数据输入D0~D15及PAF、WCLK、WEN均与FPGA相连。数据输出Q0~Q15及REN、RCLK、OE、EF、MRS、HF、FF均与USB2.0单片机相连。读FIFO状态时,USB2.0单片机给出FIFO复位信号MRS和使能信号OE,然后判断FIFO的状态信号EF(空)和HF(半满)。当FIFO半满且非空,即EF为高,HF为低时,给出FIFO读使能信号REN和读时钟RCLK,从FIFO中读出数据;写FIFO时,FPGA判断FIFO的PAF(几乎满)信号,如果该信号无效,则给出写使能WEN和写时钟WCLK,将数据写入FIFO。

4 FPGA内部逻辑设计

FPGA内部逻辑主要分为数字信号采集、数据缓存和数据读取、FIFO控制。根据要求,信号采集又分为频率信号采集、20路数字信号采集和15路脉冲信号采集。系统同时采集三组信号,再送入外部FIFO中缓存。由于脉冲信号的数据量较大,时序不匹配,因此在信号采集完后数据还应缓存,然后再经数据编帧送至外部FIFO。内部缓存利用VHDL编写模块,但是更简易的方法是利用FPGA内部的双口RAM。因此,FPGA选用Xilinx公司的XCF2S-100E,其内部集成5 KB容量的RAM,足够内部缓存使用。数据经信号采集后送人缓存,然后由读取模块读出再送入外部FIFO,整个模块采用120 MHz的时钟,可以满足要求大于100 MHz的时钟频率。采集20路数字信号的方法是当信号变化时,就将当前所有数字信号的电平状态都送入缓存,而对于频率信号和脉冲信号的采集则采用如下方法。

测控系统常常需要处理所采集到的各种数字量信号。通常测控系统采用通用MCU完成系统任务。但当系统中采集信号量较多时,仅依靠MCU则难以完成系统任务。针对这一问题,提出一种基于FPGA技术的多路数字量采集模块。利用FPGA的I/O端口数多且可编程设置的特点,配以VHDL编写的FPGA内部逻辑,实现采集多路数字量信号。

2 模块设计方案

2.1 功能要求

该数字量采集模块主要功能是采集输入的36路数字及脉冲信号,并将编帧后的信号数据上传给上位机,上位机经解包处理后显示信号相应的状态进行判断。

根据设计要求,所测量的36路数字信号中,有15路正脉冲信号。它们均由一个同步脉冲信号触发,因此需要测量这些正脉冲的宽度和相对于同步信号脉冲的延时。

要求采集步长不能大于10 ns,即采集频率高于100 MHz。而其他数字信号需要显示高低电平状态,其中一路信号是固定频率信号,需测量其频率值。上位机要求显示所采集信号的状态。

2.2 模块原理框图

FPGA内部逻辑功能强大,外围电路设计基于简单、可靠的原则。该模块由FIFO、USB2.0单片机、光电隔离器等部分组成。36路数字信号经光电隔离器进入FPGA主控单元,以供采集;FPGA处理采集到的信号,转换成数据进行编帧,然后写入FIFO。USB单片机提取FIFO中的数据,通过USB电缆传送给上位机,上位机将传送来的数据解帧,然后显示所有信号状态。模块通过电源接口向各个部分供电。其原理框图如图1所示。

3 模块电路设计

3.1 FPGA配置电路

FPGA是采用XILINX公司的Spantan-II系列XC2S100E,该系列器件的内核采用2.5 V供电,工作频率高达200 MHz;I/O端口供电电压为3.3 V,可承受5 V的输入高电平。Spartan-II系列的FPGA具有丰富的I/O端口资源。其I/O端口输出缓冲器接收高达24 mA源出电流和48 mA灌入电流。

由于FPGA基于RAM工艺技术,掉电后不能保存信息,因此需要

一个外置存储器来保存信息。采用一次可编程的PROM(高有效或低有效)XCF01SV020,其复位引脚的极性可编程设置,供电电压为3.3 V。

XCF01SVO20的DONE、INIT、CCLK信号来自于FPGA XC2S100E。系统上电后,首先FPGA初始化,INIT、DONE置低。INIT置低后复位PROM,此时由于PROM的CE为低,因此选取PROM,从而可将数据流从DATA引脚输入到FPGA的DIN引脚。配置完成后,FPGA将DONE接高,PROM处于低功耗的待机模式,并将DATA引脚置为高阻态。图2为FPGA配置电路图。

3.2 光电隔离电路

采用高速光电耦合器HCPL-2631,其开关频率高达10 MHz,而输人数字信号频率为120 kHz,完全满足要求。由于光电耦合器件以光为媒介传输信息,可使输入输出隔离,由于光电耦合器的输入回路为发光二极管,其输入阻抗很小,而干扰源的内阻较大,根据分压原理可知,馈送到光电耦合器输入端的噪声干扰电压变得很小,从而能有效抑制尖峰脉冲及各种噪声干扰,具有较强的抗干扰性能;另外由于光电隔离器的两端采用不同的接地方式,因此数字信号地和模块地被完全隔离。图3为光电隔离电路图。

3.3 FIFO电路

FIFO电路采用IDT公司的IDT72V17190器件,该器件采用3.3 V电压供电,16位64 KB容量的FIFO,工作时钟高达100 MHz。如图4所示,FIFO的数据输入D0~D15及PAF、WCLK、WEN均与FPGA相连。数据输出Q0~Q15及REN、RCLK、OE、EF、MRS、HF、FF均与USB2.0单片机相连。读FIFO状态时,USB2.0单片机给出FIFO复位信号MRS和使能信号OE,然后判断FIFO的状态信号EF(空)和HF(半满)。当FIFO半满且非空,即EF为高,HF为低时,给出FIFO读使能信号REN和读时钟RCLK,从FIFO中读出数据;写FIFO时,FPGA判断FIFO的PAF(几乎满)信号,如果该信号无效,则给出写使能WEN和写时钟WCLK,将数据写入FIFO。

4 FPGA内部逻辑设计

FPGA内部逻辑主要分为数字信号采集、数据缓存和数据读取、FIFO控制。根据要求,信号采集又分为频率信号采集、20路数字信号采集和15路脉冲信号采集。系统同时采集三组信号,再送入外部FIFO中缓存。由于脉冲信号的数据量较大,时序不匹配,因此在信号采集完后数据还应缓存,然后再经数据编帧送至外部FIFO。内部缓存利用VHDL编写模块,但是更简易的方法是利用FPGA内部的双口RAM。因此,FPGA选用Xilinx公司的XCF2S-100E,其内部集成5 KB容量的RAM,足够内部缓存使用。数据经信号采集后送人缓存,然后由读取模块读出再送入外部FIFO,整个模块采用120 MHz的时钟,可以满足要求大于100 MHz的时钟频率。采集20路数字信号的方法是当信号变化时,就将当前所有数字信号的电平状态都送入缓存,而对于频率信号和脉冲信号的采集则采用如下方法。

MCU FPGA VHDL 电路 USB 单片机 电压 电流 电路图 二极管 IDT Xilinx 相关文章:

- 我的FPGA学习历程(05-23)

- FPGA设计学习经验小谈(05-23)

- 在单个FPGA平台上采用多种工业以太网标准进行设计(03-13)

- FPGA的在应用编程技术研究(04-24)

- 基于CPLD与单片机的高速数据采集系统(04-08)

- Actel数模结合FPGA的远程控制器设计(05-13)