用EDA设计全数字三相昌闸管触发器IP软核

时间:11-09

来源:互联网

点击:

3 IP软核的仿真及验证

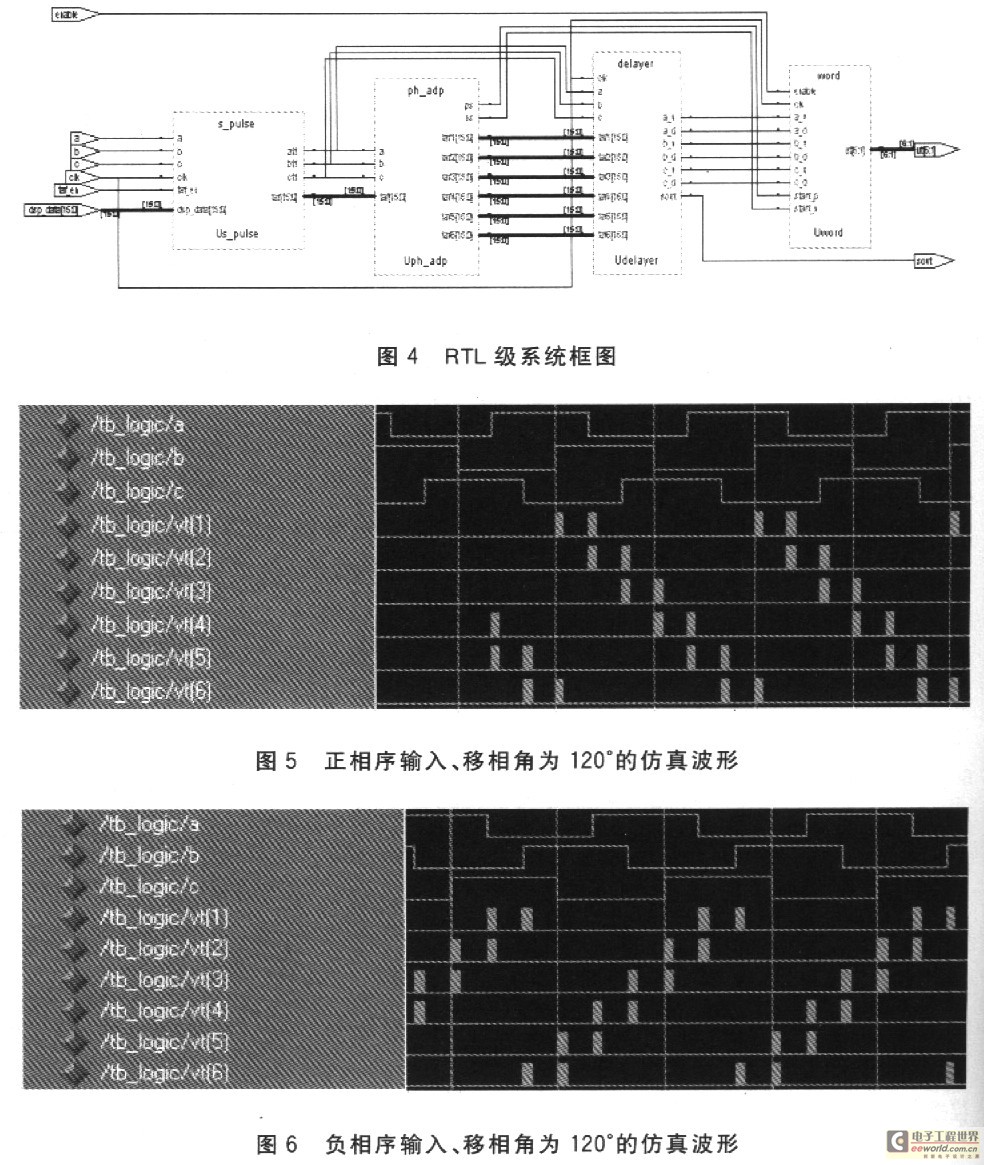

为了验证该IP软核的逻辑功能,需要对其进行功能仿真。编写testbench,在仿真软件Modelsim中对顶层模块进行功能模块。使用testbench可以对所设计的功能模块进行灵活的仿真,以检验IP软核在正、负相序输入以及各种移相角时的输出是否正确。图5和图6分别为正、负相序输入时移相角为120°的仿真波形。

由仿真结果可以看出,该IP核的逻辑功能正确。用QuARTUSII进行编译后,下载到Altera公司的新一代CPLDMAXII系列的EPMl270中,能够实现精确的移相以及相序自适应。

4 结论

按照IP软核的设计流程,完成了全数字二二相晶闸管移相触发器的设计。该方法解决了不同移相范围触发脉冲输出的问题,并实现了相序自适应,为三相晶闸管移相触发电路的应用提供了有效的可复用设计手段,使得整个控制系统的设计得以简化。该IP软核的设计已成功应用于基于TMS320LF2407A的直流电机调速系统中。

为了验证该IP软核的逻辑功能,需要对其进行功能仿真。编写testbench,在仿真软件Modelsim中对顶层模块进行功能模块。使用testbench可以对所设计的功能模块进行灵活的仿真,以检验IP软核在正、负相序输入以及各种移相角时的输出是否正确。图5和图6分别为正、负相序输入时移相角为120°的仿真波形。

由仿真结果可以看出,该IP核的逻辑功能正确。用QuARTUSII进行编译后,下载到Altera公司的新一代CPLDMAXII系列的EPMl270中,能够实现精确的移相以及相序自适应。

4 结论

按照IP软核的设计流程,完成了全数字二二相晶闸管移相触发器的设计。该方法解决了不同移相范围触发脉冲输出的问题,并实现了相序自适应,为三相晶闸管移相触发电路的应用提供了有效的可复用设计手段,使得整个控制系统的设计得以简化。该IP软核的设计已成功应用于基于TMS320LF2407A的直流电机调速系统中。

半导体 电路 EDA VHDL 变压器 仿真 Altera CPLD 相关文章:

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA 上同步开关噪声的分析(04-05)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)