用EDA设计全数字三相昌闸管触发器IP软核

时间:11-09

来源:互联网

点击:

IP(Intellectual Propcrty)就是常说的知识产权。美国Dataquest咨询公司将半导体产业的IP定义为用于ASIC、ASSP和PLD等当中,并且是预先设计好的电路模块。IP核模块有行为(Behavior)、结构(Structure)和物理(Physical)_三级不同程度的设计。根据描述功能行为的不同,IP核分为三类。即软核(Soft IP Corc)、完成结构描述的固核(Firm IP Core)和基于物理描述并经过工艺验证的硬核(Hard IP Core)。IP软核通常是用HDL文奉形式提交给用户,它经过RTL级设计优化和功能验证,但其中不含有任何具体的物理信息。据此,用户可以综合出正确的门电路级设计网表,并可以进行后续的结构设计,具有很大的灵活性;借助于EDA综合工具可以很容易地与其他外部逻辑电路合成一体,根据各种不同半导体工艺,设计成具有不同性能的器件。本文利用先进的EDA软件,用VHDL硬件描述语言采用自顶向下的模块化设计方法,完成了具有相序自适应功能的双脉冲数字移相触发器的IP软核设计。

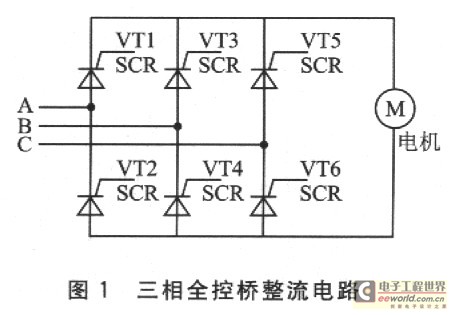

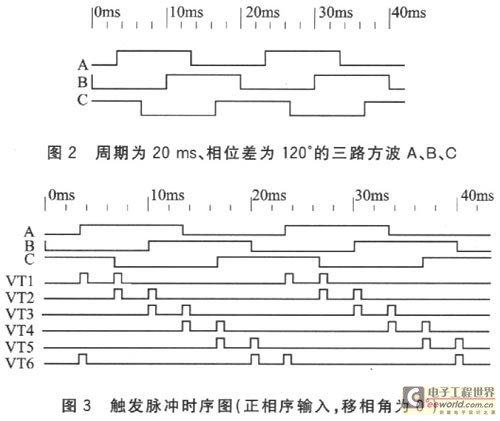

1 三相全控桥整流电路

如图1所示,三相全控桥整流电路由6只晶闸管组成。共阴极组侧和共阳级组侧的各3只晶闸管相互换流,在电源的一个周期内获得6次换流的脉动波形。三相全控桥整流电路在任何时刻必须保证有两个不同组别的晶闸管同时导通才能构成回路。换流只在本组内进行,每隔120°换流一次。由于共阴级组与共阳级组的换流点相隔60°,所以每隔60°有一个元件换流。同组内各晶闸管的触发脉冲相位差为120°,接在同一相的两个元件的触发脉冲相位差为180°,而相邻两脉冲的相位差是60°。

2 IP软核设计

2.1 触发脉冲输出设计思路

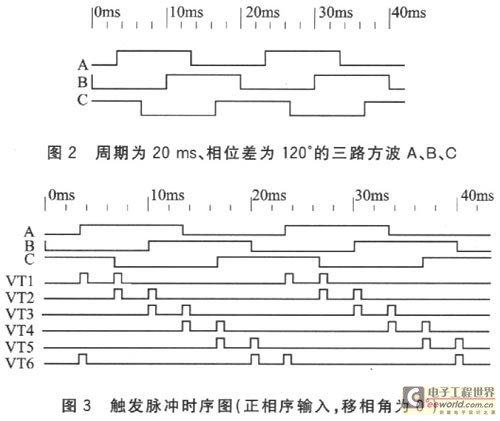

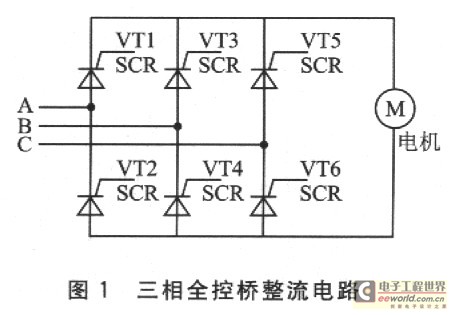

本设计的触发脉冲移相是以三相的自然换相点为基准的,三相电源U、V、W输入经过两两相减并整流以后得到周期为20 ms、相位差为120°的三路方波A、B、C(如图2所示),作为顶层模块的同步输入。分析触发脉冲可以发现,不管移相触发角为多少,以A相的过零点作为同步点,则从同步点开始的一个周期360°内,必然产生6次输出脉冲。本设计采用双窄脉冲,每次有两路输出。6个晶闸管的触发分别由A、B、C的正、负电平周期内进行延时。例如:A的正电平周期内,以A的上升沿为起始点,经过由移相角决定的延时后,发出VTl的触发脉冲;在双窄脉冲应用中,同时发出VT6的触发脉冲。触发脉冲时序图如图3昕示。

可以实现从自然换相点开始0°~180°的延时,设计思路简单直观,而通常设计则须区分不同的移相范围。在外部输入6MHz的时钟时,可以实现精度为O.003°的移相,同时还可实现相序自适应。

2.2 IP软核设计思路

采用层次化的设汁思想,将模块分为顶层模块和子模块,各模块均使用VHDL语言进行设计。顶层模块(Trigger)决定整个设计的输入/输出接口和各个子模块的连接关系。设计思路为:移相角的输入由并行的16位数据线输入,并保存在移相角寄存器中;A、B、C三相输入作为移相触发输出的基准,根据移相角寄存器中的延时值对相应晶闸管的触发脉冲进行延时;触发脉冲由VTl~VT6输出,CLK是时钟输入,SOUT是周期为3.3ms的同步输出。共有4个子模块s_pulse、ph_adp、delayer和word。

s_pulse模块将A、B、C_三相输入通过D触发器实现时钟同步,由TAF_EN信号输入作为移相角的更新使能。当TAF_EN为1时,用并行的l6位数据口D0~D15的数据更新移相角寄存器中的数值。

ph_adp模块根据A、B、C三相输入完成相序的判断。相序的判断基于以下算法;当A相(U-V)的上升沿到来时,如果A、B、C三相输入的电平为101,则为正相序(U、V、W)输入;如果A、B、C三相输入的电平为110,则为负相序(U、W、V)输入。模块输出信号ps、ns分别作为正、负相序的标志。

delayer模块产生宽度为O.8 ms的触发脉冲。触发脉冲的产生分别以三相输入的上升、下降沿为基准,根据移相角寄存器中的值,由CLK触发的计数器完成6个触发脉冲的延时。例如:以同步输入A相的上升沿为基准,由CLK触发计数器开始计数,当计数值达到移相角寄存器中的值后,送出一个宽度为0.8 ms的触发脉冲VTl;三相输入的上升、下降沿分别采用各自的计数器。

word模块完成触发脉冲的调制。调制频率为10 kHz,使得每个触发脉冲内有8个子脉冲,通过脉冲变压器对6个晶闸管的门极控制,并根据相序标志ps、ns以正确的顺序送出触发脉冲。

正相序时的触发脉冲顺序为:VTl→VT2→VT3→VT4→VT5→VT6→VTl。

负相序时的触发脉冲顺序为:VT6→V15→VT4→VT3→VT2→VT1→VT6。

2.3 IP软核设计实现

本设计中,IP软核由VHDL语言编写实现,使用synplicity公司的Synplify Pro完成编译和综合。综合以后的RTL级系统框图如图4所示。

可以根据具体系统所用的不同器件进行综合,再使用不同器件厂商的布局布线工具产生编程文件,然后下载到具体器什中,就完成了该IP软核的应用实现。

1 三相全控桥整流电路

如图1所示,三相全控桥整流电路由6只晶闸管组成。共阴极组侧和共阳级组侧的各3只晶闸管相互换流,在电源的一个周期内获得6次换流的脉动波形。三相全控桥整流电路在任何时刻必须保证有两个不同组别的晶闸管同时导通才能构成回路。换流只在本组内进行,每隔120°换流一次。由于共阴级组与共阳级组的换流点相隔60°,所以每隔60°有一个元件换流。同组内各晶闸管的触发脉冲相位差为120°,接在同一相的两个元件的触发脉冲相位差为180°,而相邻两脉冲的相位差是60°。

2 IP软核设计

2.1 触发脉冲输出设计思路

本设计的触发脉冲移相是以三相的自然换相点为基准的,三相电源U、V、W输入经过两两相减并整流以后得到周期为20 ms、相位差为120°的三路方波A、B、C(如图2所示),作为顶层模块的同步输入。分析触发脉冲可以发现,不管移相触发角为多少,以A相的过零点作为同步点,则从同步点开始的一个周期360°内,必然产生6次输出脉冲。本设计采用双窄脉冲,每次有两路输出。6个晶闸管的触发分别由A、B、C的正、负电平周期内进行延时。例如:A的正电平周期内,以A的上升沿为起始点,经过由移相角决定的延时后,发出VTl的触发脉冲;在双窄脉冲应用中,同时发出VT6的触发脉冲。触发脉冲时序图如图3昕示。

可以实现从自然换相点开始0°~180°的延时,设计思路简单直观,而通常设计则须区分不同的移相范围。在外部输入6MHz的时钟时,可以实现精度为O.003°的移相,同时还可实现相序自适应。

2.2 IP软核设计思路

采用层次化的设汁思想,将模块分为顶层模块和子模块,各模块均使用VHDL语言进行设计。顶层模块(Trigger)决定整个设计的输入/输出接口和各个子模块的连接关系。设计思路为:移相角的输入由并行的16位数据线输入,并保存在移相角寄存器中;A、B、C三相输入作为移相触发输出的基准,根据移相角寄存器中的延时值对相应晶闸管的触发脉冲进行延时;触发脉冲由VTl~VT6输出,CLK是时钟输入,SOUT是周期为3.3ms的同步输出。共有4个子模块s_pulse、ph_adp、delayer和word。

s_pulse模块将A、B、C_三相输入通过D触发器实现时钟同步,由TAF_EN信号输入作为移相角的更新使能。当TAF_EN为1时,用并行的l6位数据口D0~D15的数据更新移相角寄存器中的数值。

ph_adp模块根据A、B、C三相输入完成相序的判断。相序的判断基于以下算法;当A相(U-V)的上升沿到来时,如果A、B、C三相输入的电平为101,则为正相序(U、V、W)输入;如果A、B、C三相输入的电平为110,则为负相序(U、W、V)输入。模块输出信号ps、ns分别作为正、负相序的标志。

delayer模块产生宽度为O.8 ms的触发脉冲。触发脉冲的产生分别以三相输入的上升、下降沿为基准,根据移相角寄存器中的值,由CLK触发的计数器完成6个触发脉冲的延时。例如:以同步输入A相的上升沿为基准,由CLK触发计数器开始计数,当计数值达到移相角寄存器中的值后,送出一个宽度为0.8 ms的触发脉冲VTl;三相输入的上升、下降沿分别采用各自的计数器。

word模块完成触发脉冲的调制。调制频率为10 kHz,使得每个触发脉冲内有8个子脉冲,通过脉冲变压器对6个晶闸管的门极控制,并根据相序标志ps、ns以正确的顺序送出触发脉冲。

正相序时的触发脉冲顺序为:VTl→VT2→VT3→VT4→VT5→VT6→VTl。

负相序时的触发脉冲顺序为:VT6→V15→VT4→VT3→VT2→VT1→VT6。

2.3 IP软核设计实现

本设计中,IP软核由VHDL语言编写实现,使用synplicity公司的Synplify Pro完成编译和综合。综合以后的RTL级系统框图如图4所示。

可以根据具体系统所用的不同器件进行综合,再使用不同器件厂商的布局布线工具产生编程文件,然后下载到具体器什中,就完成了该IP软核的应用实现。

半导体 电路 EDA VHDL 变压器 仿真 Altera CPLD 相关文章:

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA 上同步开关噪声的分析(04-05)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)