在Virtex-5 FPGA芯片中使用CRC硬模块

时间:11-09

来源:互联网

点击:

CRC模块

CRC 的硬件实现使用一个简单的 LFSR。这种电路虽然实现起来简单,但对于一个n位数据流来说,要占用n个时钟周期来计算CRC值。在必须以较高速度处理数据帧的高速数据网络应用中,这样的延迟是无法忍受的。这类高速网络应用迫切需要对并行数据流实现CRC生成和校验。

Virtex-5 LXT/SXT器件中实现的CRC模块可帮助设计人员加速校验和计算。

Virtex-5 LXT/SXT器件中的 CRC硬模块基于CRC32多项式。Virtex-5 FPGA含有CRC32和 CRC64 两种硬模块,能以一个时钟周期的延迟为4位和8位数据输出生成CRC。其界面简单易用。硬模块对给定的消息流起着CRC计算器的作用,同时提供一些针对 CRC的参数作为输入。CRC的比较功能已经超出硬模块的范围,应集成到FPGA架构中。

FPGA 中的每个CRC硬模块异步计算一个32位校验和。

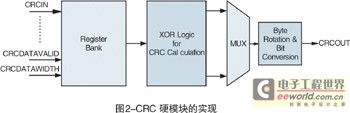

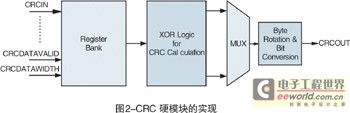

图2是说明硬模块架构的模块级图。CRC硬模块提供一个位反演和字节反转的输出。

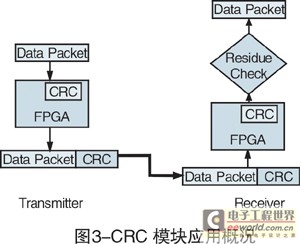

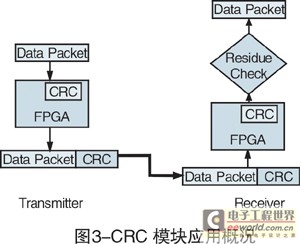

图3所示为CRC硬模块的应用概况。在发射器上,CRC经计算后附加到给定数据包的尾部。在接收器上,对连带发射器所附加的CRC一起接收到的整个数据包重新计算CRC。

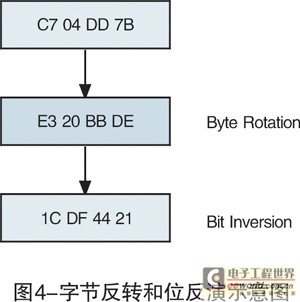

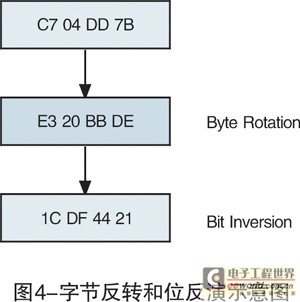

所收数据包的有效性用剩余法来确定。对于本例中的CRC32多项式来说,剩余值的计算结果将是十六进制的1CDF4421,这其实就是 C704DDB7的位反演和字节反转值。字节反转和位反演的概念如图4所示。

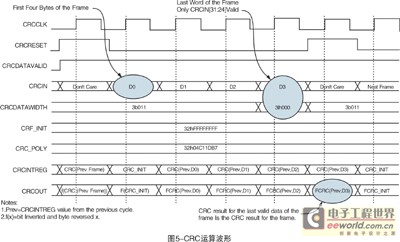

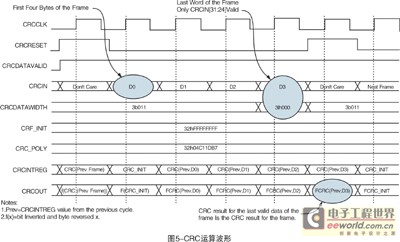

图5所示为正常CRC运算的波形

我们还提供一个LogiCORETM CRC 向导,其中为 Virtex-5 器件中的CRC硬模块提供一个LocalLink封装。其内核还提供了一个说明如何使用 CRC 硬模块的设计实例。此外,内核提供了各种选项,如流水线处理、补数计算和转置。

结论

Xilinx FPGA中的CRC模块使设计人员能够轻松地将检错机制加入到各种设计中。可以用CORE GeneratorTM软件中提供的CRC Wizard IP加入符合不同协议(如 Aurora 和 PCI Express)的检错功能。

CRC 的硬件实现使用一个简单的 LFSR。这种电路虽然实现起来简单,但对于一个n位数据流来说,要占用n个时钟周期来计算CRC值。在必须以较高速度处理数据帧的高速数据网络应用中,这样的延迟是无法忍受的。这类高速网络应用迫切需要对并行数据流实现CRC生成和校验。

Virtex-5 LXT/SXT器件中实现的CRC模块可帮助设计人员加速校验和计算。

Virtex-5 LXT/SXT器件中的 CRC硬模块基于CRC32多项式。Virtex-5 FPGA含有CRC32和 CRC64 两种硬模块,能以一个时钟周期的延迟为4位和8位数据输出生成CRC。其界面简单易用。硬模块对给定的消息流起着CRC计算器的作用,同时提供一些针对 CRC的参数作为输入。CRC的比较功能已经超出硬模块的范围,应集成到FPGA架构中。

FPGA 中的每个CRC硬模块异步计算一个32位校验和。

图2是说明硬模块架构的模块级图。CRC硬模块提供一个位反演和字节反转的输出。

图3所示为CRC硬模块的应用概况。在发射器上,CRC经计算后附加到给定数据包的尾部。在接收器上,对连带发射器所附加的CRC一起接收到的整个数据包重新计算CRC。

所收数据包的有效性用剩余法来确定。对于本例中的CRC32多项式来说,剩余值的计算结果将是十六进制的1CDF4421,这其实就是 C704DDB7的位反演和字节反转值。字节反转和位反演的概念如图4所示。

图5所示为正常CRC运算的波形

我们还提供一个LogiCORETM CRC 向导,其中为 Virtex-5 器件中的CRC硬模块提供一个LocalLink封装。其内核还提供了一个说明如何使用 CRC 硬模块的设计实例。此外,内核提供了各种选项,如流水线处理、补数计算和转置。

结论

Xilinx FPGA中的CRC模块使设计人员能够轻松地将检错机制加入到各种设计中。可以用CORE GeneratorTM软件中提供的CRC Wizard IP加入符合不同协议(如 Aurora 和 PCI Express)的检错功能。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 迄今为止最牛的ASIC验证平台(05-22)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)