利用Virtex-5系统监控器加强系统管理和诊断

时间:11-09

来源:互联网

点击:

系统集成

除了能够利用JTAG TAP轻松访问系统监控器之外,还可以通过FPGA架构访问系统监控器的控制和状态寄存器。利用FPGA架构可以在任何时刻对这些寄存器进行配置和读取。允许通过JTAG TAP控制器和架构接口对系统监控器的寄存器进行双重访问,并提供了相应的仲裁方案来管理可能出现的争用现象。

在设计中例示系统监控器,并在FPGA配置过程中对其初始化时,还能够定义这些寄存器的内容。因此,可以对系统监控器进行配置使其以用户自定义的运行(后配置)模式启动。架构接口就是我们所熟知的动态重配置端口(DRP)。DRP是一个并行的16位同步数据端口(类似于block RAM)。

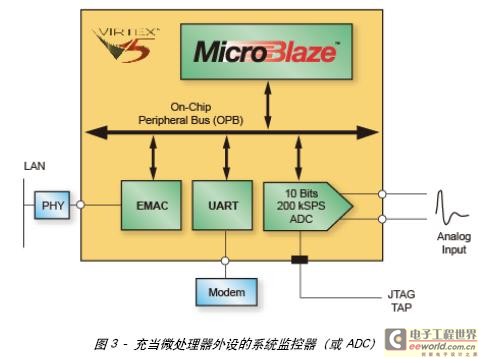

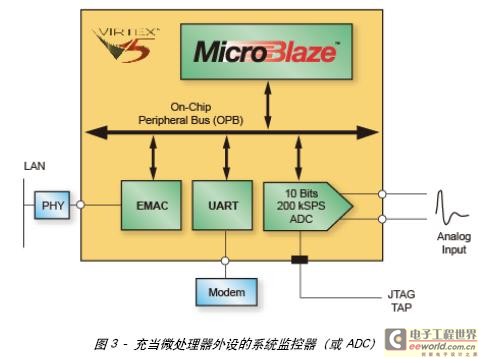

对于需要对系统监控器进行更多控制的高级应用(此时)而言,DRP能够让系统监控器轻松地映射到硬/软微处理器的外设地址空间中。图3显示了一个典型系统管理应用,这里MicroBlaze处理器运行一个类似于协议的智能平台管理接口(IPMI),并且通过管理通道(如以太网,甚至是简单的UART/调制解调器)与系统主机进行通信。

系统监控器还以通用ADC的形式提供了一个重要的微处理器外设。这是业界首次将微控制器中常见的模拟外设集成到FPGA中。此外,该系统还可以完全控制ADC操作。ADC提供了大量采样模式,并且支持单极、双极和全差分模拟输入方案。

本文小结

Virtex-5系统监控器为一般的片上和外部环境监控需求提供了一个大大简化了的解决方案。其功能访问需要极少的开发和设计工作。通过将系统监控器和JTAG TAP控制器连接在一起,JTAG功能已经延伸到新的应用领域,从而实现了新的测试能力。我们非常希望收到您对本文所提到的任何专题的意见和反馈信息,特别是我们的开发队伍如何更好地为您的系统监控和测试需求提供支持。

除了能够利用JTAG TAP轻松访问系统监控器之外,还可以通过FPGA架构访问系统监控器的控制和状态寄存器。利用FPGA架构可以在任何时刻对这些寄存器进行配置和读取。允许通过JTAG TAP控制器和架构接口对系统监控器的寄存器进行双重访问,并提供了相应的仲裁方案来管理可能出现的争用现象。

在设计中例示系统监控器,并在FPGA配置过程中对其初始化时,还能够定义这些寄存器的内容。因此,可以对系统监控器进行配置使其以用户自定义的运行(后配置)模式启动。架构接口就是我们所熟知的动态重配置端口(DRP)。DRP是一个并行的16位同步数据端口(类似于block RAM)。

对于需要对系统监控器进行更多控制的高级应用(此时)而言,DRP能够让系统监控器轻松地映射到硬/软微处理器的外设地址空间中。图3显示了一个典型系统管理应用,这里MicroBlaze处理器运行一个类似于协议的智能平台管理接口(IPMI),并且通过管理通道(如以太网,甚至是简单的UART/调制解调器)与系统主机进行通信。

系统监控器还以通用ADC的形式提供了一个重要的微处理器外设。这是业界首次将微控制器中常见的模拟外设集成到FPGA中。此外,该系统还可以完全控制ADC操作。ADC提供了大量采样模式,并且支持单极、双极和全差分模拟输入方案。

本文小结

Virtex-5系统监控器为一般的片上和外部环境监控需求提供了一个大大简化了的解决方案。其功能访问需要极少的开发和设计工作。通过将系统监控器和JTAG TAP控制器连接在一起,JTAG功能已经延伸到新的应用领域,从而实现了新的测试能力。我们非常希望收到您对本文所提到的任何专题的意见和反馈信息,特别是我们的开发队伍如何更好地为您的系统监控和测试需求提供支持。

传感器 电压 FPGA Xilinx ADC PCB 电流 相关文章:

- 基于FPGA的高速图像采集系统设计(03-30)

- 在单个FPGA平台上采用多种工业以太网标准进行设计(03-13)

- 基于CPLD的CCD信号发生器的研究(04-08)

- 在嵌入式设计中降低CPLD的功耗(04-30)

- Xilinx FPGA的功耗优化设计(04-08)

- 基于太空级Virtex FPGA的灵活高性能计算平台(04-08)