一种基于FPGA的复数浮点协方差矩阵实现

时间:11-09

来源:互联网

点击:

2 仿真结果

可编程逻辑设计有许多内在规律可循,其中一项就是面积和速度的平衡与互换原则。面积和速度是一对对立统一的矛盾体,要求一个设计同时具备设计面积最小,运行频率最高,这是不现实的。于是基于面积优先原则和速度优先原则,本文分别设计了协方差矩阵的串行处理方案和并行处理方案,并用Altera\stratix\EP1S20F780C7进行板上调试。其调试结果表明,串行处理方案占用的资源是并行处理方案的1/4,但其运算速度却是后者的11倍。

2.1 串行处理方案仿真结果

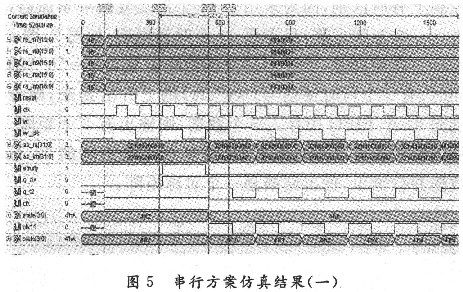

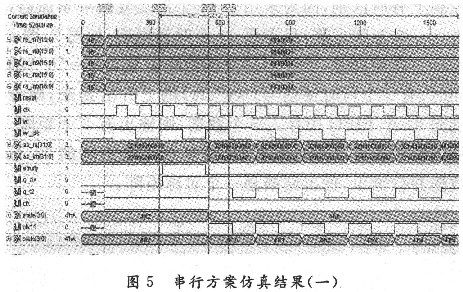

如图5所示,clk为运算的总控制时钟;reset为复位控制信号,高电平有效;rd为读使能信号,低电平有效;wr为写使能信号,低电平有效;wr_clk为写时钟信号,上升沿触发;q_clk为读时钟信号,上升沿触发;ab_re(31:O)和ab_im(31:O)为乘法器输出的实部和虚部。q_t2为矩阵乘累加模块的同步时钟信号;clkll,state(3:O),clkl和state(3:0)是状态机的控制信号,控制矩阵运算规则。

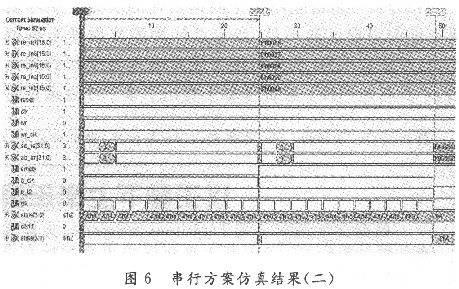

如图5所示,在100 ns时reset信号有效(即reset=‘1’),所有状态清零。从335~635 ns间,写使能信号有效(wr=‘O’)且有两个写时钟信号的上升沿到来,即向任意一个通道的FIFO中存入两个快拍采样数据,最后输出结果应该有两个矩阵,如图6所示。当FIFO为空时,运算停止,所有状态清零。等待新采样数据的到来。

图5中,在350 ns时,读使能有效(rd=‘0’)且有一个读时钟信号的上升沿到来,所以empty信号存在短暂的不空(empty=‘O’)状态,捕获到这个信息,便触发单稳态触发器模块,产生具有121个clk时钟周期长度,占空比为120:1的q_clk信号,进行FIFO的读操作。

在350~535 ns时间段,因为写时钟信号没有到来,所以FIFO为空(empty=‘1’)。从550 ns~24.75 μs时间段读时钟信号没有上升沿到来,整个设计处于第一个矩阵的运算过程中,即运算一个矩阵所需要的时间为24.2 μs。与此同时,第二个数据写入FIFO,empty一直处于不空状态(empty=‘O’)。

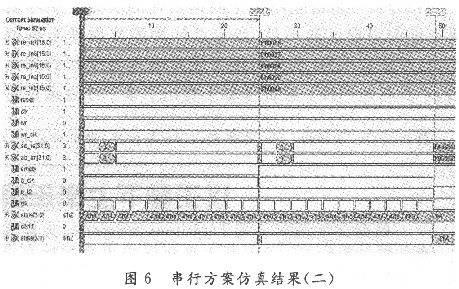

在第一个矩阵运算结束之后,即24.6μs时,系统检测到empty=‘0’,开始读数据并触发第二个矩阵运算的时钟控制信号。如图6所示,在24.6μs时,empty=‘1’。FIFO中的第二个数据被读出,处于空状态。从24.85~49.05μs进入第二个矩阵的运算周期。

在仿真时,输人数据为16位的定点数(1+j1;O+jO;2+j2;3+j3;4+j4;5+j5,6+j6;7+j7;8+j8;9+j9;A+jA),输出结果为32位的单精度浮点数。选择的主时钟周期为200 ns。在实际调试过程中,整个系统可以在50 MHz主时钟频率下正常工作。

2.2 并行处理方案仿真结果

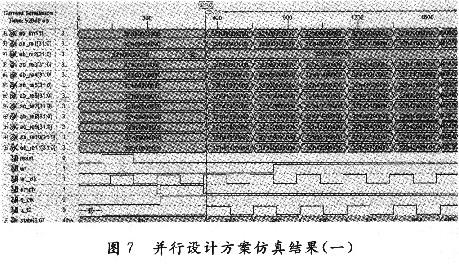

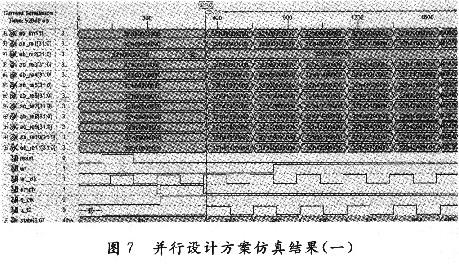

并行方案运算原理与串行方案的一样,只是在时钟控制上有所区别,因为采用了11个浮点复数乘累加器,进行一次矩阵运算,只需要11个时钟周期,如图7,图8所示。在仿真时,设置在写使能信号有效(wr=‘O’)的同时,有3个写时钟信号(wr_clk)的上升沿到来,即分别向22个FIF0中存入3个数据,则输出有3个矩阵。从图7中还可以清楚地看出,运算结果是矩阵的11行数据并行输出,输出结果是一个对称矩阵。

3 结语

在分析了目前应用于空间谱估计的协方差矩阵运算在硬件实现上的不足,如定点计算的数据动态范围小,运算精度不高,且只适用于特定阵列模型和的阵元数,不具备通用性。在此基础上提出了基于浮点运算的通用型协方差矩阵的实现方案。仿真结果表明,本文所提出的实现方案采用的是复数乘法运算,最终结果得到的是复共轭对称矩阵,适合利用任意的阵列模型和阵元数得到与之相对应的协方差矩阵。这就拓展了协方差矩阵运算的应用范围,且整个运算过程采用的是浮点运算,提高了整个运算的精度。

可编程逻辑设计有许多内在规律可循,其中一项就是面积和速度的平衡与互换原则。面积和速度是一对对立统一的矛盾体,要求一个设计同时具备设计面积最小,运行频率最高,这是不现实的。于是基于面积优先原则和速度优先原则,本文分别设计了协方差矩阵的串行处理方案和并行处理方案,并用Altera\stratix\EP1S20F780C7进行板上调试。其调试结果表明,串行处理方案占用的资源是并行处理方案的1/4,但其运算速度却是后者的11倍。

2.1 串行处理方案仿真结果

如图5所示,clk为运算的总控制时钟;reset为复位控制信号,高电平有效;rd为读使能信号,低电平有效;wr为写使能信号,低电平有效;wr_clk为写时钟信号,上升沿触发;q_clk为读时钟信号,上升沿触发;ab_re(31:O)和ab_im(31:O)为乘法器输出的实部和虚部。q_t2为矩阵乘累加模块的同步时钟信号;clkll,state(3:O),clkl和state(3:0)是状态机的控制信号,控制矩阵运算规则。

如图5所示,在100 ns时reset信号有效(即reset=‘1’),所有状态清零。从335~635 ns间,写使能信号有效(wr=‘O’)且有两个写时钟信号的上升沿到来,即向任意一个通道的FIFO中存入两个快拍采样数据,最后输出结果应该有两个矩阵,如图6所示。当FIFO为空时,运算停止,所有状态清零。等待新采样数据的到来。

图5中,在350 ns时,读使能有效(rd=‘0’)且有一个读时钟信号的上升沿到来,所以empty信号存在短暂的不空(empty=‘O’)状态,捕获到这个信息,便触发单稳态触发器模块,产生具有121个clk时钟周期长度,占空比为120:1的q_clk信号,进行FIFO的读操作。

在350~535 ns时间段,因为写时钟信号没有到来,所以FIFO为空(empty=‘1’)。从550 ns~24.75 μs时间段读时钟信号没有上升沿到来,整个设计处于第一个矩阵的运算过程中,即运算一个矩阵所需要的时间为24.2 μs。与此同时,第二个数据写入FIFO,empty一直处于不空状态(empty=‘O’)。

在第一个矩阵运算结束之后,即24.6μs时,系统检测到empty=‘0’,开始读数据并触发第二个矩阵运算的时钟控制信号。如图6所示,在24.6μs时,empty=‘1’。FIFO中的第二个数据被读出,处于空状态。从24.85~49.05μs进入第二个矩阵的运算周期。

在仿真时,输人数据为16位的定点数(1+j1;O+jO;2+j2;3+j3;4+j4;5+j5,6+j6;7+j7;8+j8;9+j9;A+jA),输出结果为32位的单精度浮点数。选择的主时钟周期为200 ns。在实际调试过程中,整个系统可以在50 MHz主时钟频率下正常工作。

2.2 并行处理方案仿真结果

并行方案运算原理与串行方案的一样,只是在时钟控制上有所区别,因为采用了11个浮点复数乘累加器,进行一次矩阵运算,只需要11个时钟周期,如图7,图8所示。在仿真时,设置在写使能信号有效(wr=‘O’)的同时,有3个写时钟信号(wr_clk)的上升沿到来,即分别向22个FIF0中存入3个数据,则输出有3个矩阵。从图7中还可以清楚地看出,运算结果是矩阵的11行数据并行输出,输出结果是一个对称矩阵。

3 结语

在分析了目前应用于空间谱估计的协方差矩阵运算在硬件实现上的不足,如定点计算的数据动态范围小,运算精度不高,且只适用于特定阵列模型和的阵元数,不具备通用性。在此基础上提出了基于浮点运算的通用型协方差矩阵的实现方案。仿真结果表明,本文所提出的实现方案采用的是复数乘法运算,最终结果得到的是复共轭对称矩阵,适合利用任意的阵列模型和阵元数得到与之相对应的协方差矩阵。这就拓展了协方差矩阵运算的应用范围,且整个运算过程采用的是浮点运算,提高了整个运算的精度。

- 数字下变频的FPGA实现(05-12)

- 用FPGA实现音频采样率的转换(02-07)

- 基于FPGA的任意时延伪码序列产生方法(04-12)

- 基于FPGA实现变采样率FIR滤波器的研究(04-13)

- 基于CPLD的CCD信号发生器的研究(04-08)

- 利用FPGA和CPLD数字逻辑实现ADC(06-04)