基于FPGA的高速PID控制器设计与仿真

时间:11-09

来源:互联网

点击:

- 4 系统实现与功能仿真

整个PID控制器的系统设计采用自顶向下的设计方法和模块化的设计思想,即先由PTD控制器的自然语言描述得到VHDL的系统行为描述,然后对系统分解为误差A/D变换部件、PID运算部件、控制增量D/A变换以及协调三者的控制状态机等四个主要模块。

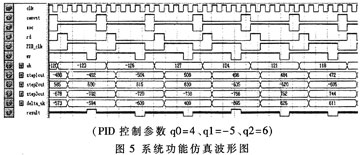

Altera公司专用EDA软件QuartusII支持原理图与VHDL语言混合输入设计方式,除PID运算部件采用原理图输入设计方式以外,其余三个部件均采用VHDL输入设计方式。系统仿真时,如果将系统的最高工作速率设定为120MHz,则采样速率为24MHz。功能仿真波形图如图5所示。

通过对增量式数字PID控制算法的优化处理,显著提高了系统的工作速度。仿真结果表明,拥有较低转换速率的A/D变换技术成为提高系统运行速度的瓶颈。就本设计采用的闪烁型A/D器件而言,减少状态机等待A/D转换结束信号EOC(见图4)的时间,即提高A/D转换的速率是提高系统整体工作速率的关键。

本设计中所采用的增量式数字PID控制算法的设计思想可以应用到有限长单位脉冲响应(FIR)滤波器和无限长单位脉冲响应(ⅡR)滤波器的FPGA设计中,并且同样可以使用流水线优化技术以提高工作速度。同时,由于PLD设计和专用ASIC设计的通用性,在PLD设计平台上所完成的设计可以很自然地过渡到专用ASIC的设计工作中,进一步提高了系统的可靠性和集成度。

自动化 FPGA Altera Quartus 仿真 ADI ADC DAC VHDL 单片机 嵌入式 EDA 滤波器 相关文章:

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- FPGA 重复配置和测试的实现(08-14)

- FPGA 设计工具视点(10-15)

- 让“您”居于FPGA的用户专用设计环境中(12-14)

- FPGA中嵌入式存储器模块的设计(03-28)