数字图像空域滤波算法的FPGA设计与实现

时间:11-09

来源:互联网

点击:

3 仿真综合结果

第2节介绍了本文中在FPGA平台上设计实现数字图像空域滤波算法的高速数字滤波器FIR的过程,其中主要考虑的是缩短关键路径、提高数据吞吐率。本节给出仿真和综合后的结果比较表。本文中,测试图像选用的是256×256大小、8 b的灰度图像,设计软件是XILINX公司的ISE集成综合开发环境,仿真工具是Modelsim SE 5.8b,综合工具是ISE自带的综合软件XST,实现芯片是XILINX公司的XC2V1000。仿真、综合结果表明,设计电路完全符合要求。

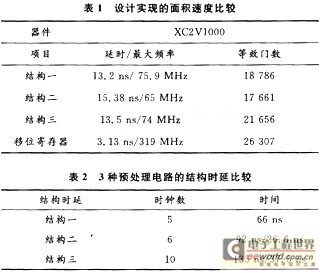

下面给出根据上述不同的FIR滤波结构设计的,用于实现空域滤波算法的3种电路结构的综合结果比较表。

从表1可以看出:从资源占用角度看,结构三的等效门数最多,结构二的最少。从延时/最大频率可以看出,结构一最好。

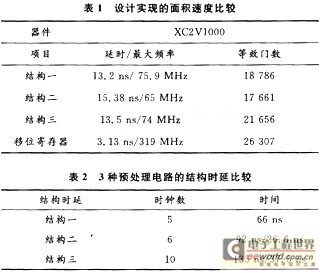

3种结构的结构时延比较数据,如表2所示。

4 结 语

本文论述了数字图像空域滤波算法以及FIR滤波器的基本设计方法,在对关键路径分析的基础上,引入流水线设计提高运算速度,提出了滤波器的3种设计结构,给出了滤波器的设计过程,通过仿真和综合结果可以看出,有效地节省了硬件资源,大大减小了硬件体积,增加了系统的可靠性。

第2节介绍了本文中在FPGA平台上设计实现数字图像空域滤波算法的高速数字滤波器FIR的过程,其中主要考虑的是缩短关键路径、提高数据吞吐率。本节给出仿真和综合后的结果比较表。本文中,测试图像选用的是256×256大小、8 b的灰度图像,设计软件是XILINX公司的ISE集成综合开发环境,仿真工具是Modelsim SE 5.8b,综合工具是ISE自带的综合软件XST,实现芯片是XILINX公司的XC2V1000。仿真、综合结果表明,设计电路完全符合要求。

下面给出根据上述不同的FIR滤波结构设计的,用于实现空域滤波算法的3种电路结构的综合结果比较表。

从表1可以看出:从资源占用角度看,结构三的等效门数最多,结构二的最少。从延时/最大频率可以看出,结构一最好。

3种结构的结构时延比较数据,如表2所示。

4 结 语

本文论述了数字图像空域滤波算法以及FIR滤波器的基本设计方法,在对关键路径分析的基础上,引入流水线设计提高运算速度,提出了滤波器的3种设计结构,给出了滤波器的设计过程,通过仿真和综合结果可以看出,有效地节省了硬件资源,大大减小了硬件体积,增加了系统的可靠性。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)