数字图像空域滤波算法的FPGA设计与实现

时间:11-09

来源:互联网

点击:

在图像通信、遥感图像分析、医学成像诊断等应用领域,为了便于显示、观察或进行进一步的处理,常常需要对原始的数字图像进行特征提取(如边缘检测、边缘锐化)、噪声平滑滤波、几何校正等处理,这类图像处理技术称为图像的预处理。在实际应用中,空域滤波算法被广泛地应用于图像的预处理技术中。

空域滤波算法是图像增强技术的一种,直接对图像的象素进行处理,不需要进行变换。常见的滤波算子如锐化算子、高通算子、平滑算子等,可以完成图像的边缘提取、噪声去除等处理。这些滤波算子尽管功能不同,实现方法却都是类似的,都是通过模板卷积的方法来实现的。

VLSI技术的迅猛发展为数字图像实时处理技术提供了硬件基础,其中FPGA(现场可编程门阵列)的特点使其非常适用于数字图像处理。本文研究的就是在FPGA设计平台上设计硬件电路,实现数字图像的空域滤波算法。

1 数字图像空域滤波算法

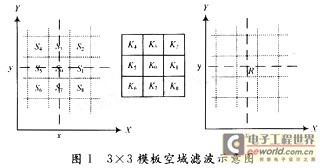

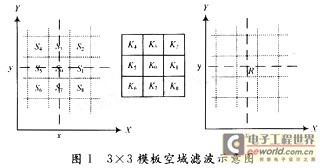

数字图像空域滤波算法的实现步骤如图1所示,左边的部分是要处理的图像的某一部分,中间是对图像进行处理的3×3模板。

具体的处理步骤是:

将模板在图像上漫游,并将模板中心与图中某个象素位置重合;

将模板上的系数与模板下对应的象素相乘;

将所有的乘积相加。

把和(模板的输出响应)赋给图像中对应模板中心位置的象素。图1中所示是图像的一部分,S0~S8是象素点的灰度值,K0~K8是3×3的模板系数。用这个3×3模板来进行空域滤波的过程是:将模板中心点,即模板系数为K0的点所在位置,与图像中灰度值为S0的点重合,模板的输出响应R为:

R=K0*S0+K1*S1+…+K8*S8 (1)

这样增强后的图像在原来位置为(x,y)处的象素点的灰度值就由S0变为R。如果对图像中的每个象素点都这样进行模板操作,就可以得到增强后的图像在所有位置的新灰度值。如果在设计滤波器时给模板系数赋予不同的值,就可以得到不同的高通、低通效果。

本文采用的图像是256×256大小的灰度图像,滤波模板3×3大小。如何设计硬件电路来完成上述空域滤波算法,分析上述算法实现过程,可以得出结论,实现空域滤波算法可采用3个三阶的FIR滤波器+延时单元来描述。

2 FIR数字滤波器的FPGA设计

在设计实现空域滤波算法的3个三阶的FIR滤波器+延时单元的电路时,要考虑的主要问题是:如何缩短硬件电路设计时的关键路径以及提高系统的数据吞吐率。为解决这些实际的FPGA设计中的关键问题,在具体设计电路时,主要从以下几个方面进行考虑:

2.1 FIR数字滤波器与流水线结构

现代微处理器、数字信号处理器、高速数字系统设计中都广泛应用了流水线(Pipelining)技术,其核心设计思想是把一个周期内执行的逻辑操作分成几步较小的操作,在多个高速的时钟周期内完成。每一次逻辑小操作的结果都存储在寄存器中,被高速时钟同步,在下一流水线单元使用,因而是速度优化中最常用的技术之一,可以大大地提高数字系统的总体运行速度。

下面分析一下三阶的FIR滤波器的基本结构和采用了流水线技术后的FIR结构,以及FIR滤波器的数据广播结构。

三阶有限冲击响应(FIR)数字滤波器可以表示如下:

y(n)=ax(n)+bx(n-1)+cx(n-2) (2)

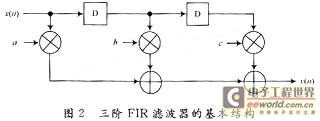

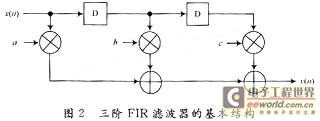

这个三阶的FIR滤波器实现的结构,如图2所示。

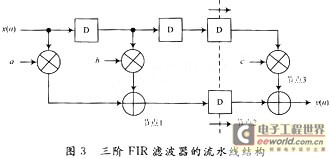

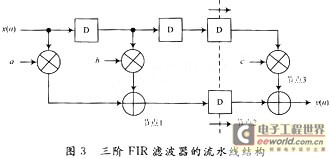

图2中,这种结构的FIR滤波器的关键路径(处理一个新样点的最小时间)由1个乘法器和2个加法器的时间来限定。如果采样周期小于这个最小时间的话,那么这种结构的FIR滤波器就不能满足要求。这时就要考虑流水技术。采用流水线技术可以缩短关键路径,如图3所示。

在流水线结构的FIR滤波器中,启动当前的迭代计算时,节点2的加法器正在完成前次迭代结果的计算。因此,这时的关键路径由1个乘法器和2个加法器的时间缩短为1个乘法器和1个加法器的时间。

采用在结构中适当插入流水线锁存器来减小关键路径长度的流水技术时,锁存器的插入并不是随意的。当把数据流图切开时,数据方向要一致向前。这样加入的流水线,才不会影响功能。图3中,插入流水线锁存器时,就是沿着结构中数据流的正向,在上下两个路径均加入了锁存器,这样FIR滤波器的逻辑才不会混乱。一种结构的速度(时钟周期),通常由任意两个锁存器之间、一个输入与一个锁存器间、一个锁存器与一个输出间或输入与输出间路径中最长的路径限定。流水线锁存器可以有效地缩短最长路径。

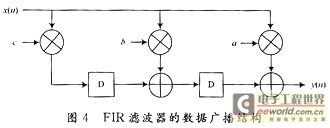

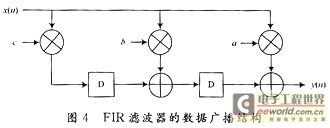

除了以上两种FIR滤波结构外,还有一种数据广播结构的FIR数字滤波器,这种结构通过转置结构来缩短关键路径,同时不需要引入任何的流水线锁存器。具体的改造方法是:改变输入和输出;颠倒信号流程的方向;由一个分支来取代加法器,反之亦然。数据广播结构的FIR数字滤波器如图4所示。

在这种结构中,数据不是存储下来,而是同时广播到所有的乘法器。这种结构的关键路径和图3中插人流水线锁存器的FIR滤波器结构的关键路径一样。但是对输入不需要额外的移位寄存器,对部分积的和也不需要额外的流水线就能达到很高的通过率。这就是FIR滤波器数据广播结构的优点。

本文在设计空域滤波算法电路时,就是分别采取了以上介绍的3种不同的FIR数字滤波器结构形式。

2.2 乘法器模块的硬件设计

从式(1)的模板运算表达式和式(2)的FIR滤波器表达式可以看出,完成模板运算和实现FIR数字滤波还有一个重要的环节,就是乘法运算。乘法器模块是影响空域滤波算法的运算速度的关键模块之一。

乘法运算基本上可以分为两步:一是求出所有的基本乘积项,二是将所有的基本乘积项相加。因此,要设计快速的乘法器电路模块,就要针对这两步进行改进,一方面要减少部分积的数目,同时另一方面要提高部分积求和阵列的累加速度。因此,为了加快乘法器模块的运算速度,在设计乘法器电路时,特别考虑到了采用基4-BOOTH算法来减少部分和的数目,同时采用Wallace Tree减少阵列乘法器中部分积加法阵列的进位传输延迟,加快整个加法阵列的运算速度。

基4-BOOTH算法的基本原理是对乘数进行编码,根据编码表来产生部分积,一次只考虑3位:本位、相邻高位、相邻低位。Wallace Tree比较规则,易于布局布线,这种方法不是直接将所有的部分积完全的一对一地相加,而是采用将各个部分积中具有相同权重的数据位相加合并。通常采用全加器(Full Adder)来完成相同权重的位相加。采用一位全加器,那么Wallace树的每一层,就可以将部分积的向量数目按照3:2的比例缩减。也可以采用2个全加器,来获得4:2的缩减比例。本文中采用3:2计数器(全加器)来进行部分和缩减,这样当部分积的数目很多时,采用Wallace Tree乘法器来缩减部分和速度很快。

空域滤波算法是图像增强技术的一种,直接对图像的象素进行处理,不需要进行变换。常见的滤波算子如锐化算子、高通算子、平滑算子等,可以完成图像的边缘提取、噪声去除等处理。这些滤波算子尽管功能不同,实现方法却都是类似的,都是通过模板卷积的方法来实现的。

VLSI技术的迅猛发展为数字图像实时处理技术提供了硬件基础,其中FPGA(现场可编程门阵列)的特点使其非常适用于数字图像处理。本文研究的就是在FPGA设计平台上设计硬件电路,实现数字图像的空域滤波算法。

1 数字图像空域滤波算法

数字图像空域滤波算法的实现步骤如图1所示,左边的部分是要处理的图像的某一部分,中间是对图像进行处理的3×3模板。

具体的处理步骤是:

将模板在图像上漫游,并将模板中心与图中某个象素位置重合;

将模板上的系数与模板下对应的象素相乘;

将所有的乘积相加。

把和(模板的输出响应)赋给图像中对应模板中心位置的象素。图1中所示是图像的一部分,S0~S8是象素点的灰度值,K0~K8是3×3的模板系数。用这个3×3模板来进行空域滤波的过程是:将模板中心点,即模板系数为K0的点所在位置,与图像中灰度值为S0的点重合,模板的输出响应R为:

R=K0*S0+K1*S1+…+K8*S8 (1)

这样增强后的图像在原来位置为(x,y)处的象素点的灰度值就由S0变为R。如果对图像中的每个象素点都这样进行模板操作,就可以得到增强后的图像在所有位置的新灰度值。如果在设计滤波器时给模板系数赋予不同的值,就可以得到不同的高通、低通效果。

本文采用的图像是256×256大小的灰度图像,滤波模板3×3大小。如何设计硬件电路来完成上述空域滤波算法,分析上述算法实现过程,可以得出结论,实现空域滤波算法可采用3个三阶的FIR滤波器+延时单元来描述。

2 FIR数字滤波器的FPGA设计

在设计实现空域滤波算法的3个三阶的FIR滤波器+延时单元的电路时,要考虑的主要问题是:如何缩短硬件电路设计时的关键路径以及提高系统的数据吞吐率。为解决这些实际的FPGA设计中的关键问题,在具体设计电路时,主要从以下几个方面进行考虑:

2.1 FIR数字滤波器与流水线结构

现代微处理器、数字信号处理器、高速数字系统设计中都广泛应用了流水线(Pipelining)技术,其核心设计思想是把一个周期内执行的逻辑操作分成几步较小的操作,在多个高速的时钟周期内完成。每一次逻辑小操作的结果都存储在寄存器中,被高速时钟同步,在下一流水线单元使用,因而是速度优化中最常用的技术之一,可以大大地提高数字系统的总体运行速度。

下面分析一下三阶的FIR滤波器的基本结构和采用了流水线技术后的FIR结构,以及FIR滤波器的数据广播结构。

三阶有限冲击响应(FIR)数字滤波器可以表示如下:

y(n)=ax(n)+bx(n-1)+cx(n-2) (2)

这个三阶的FIR滤波器实现的结构,如图2所示。

图2中,这种结构的FIR滤波器的关键路径(处理一个新样点的最小时间)由1个乘法器和2个加法器的时间来限定。如果采样周期小于这个最小时间的话,那么这种结构的FIR滤波器就不能满足要求。这时就要考虑流水技术。采用流水线技术可以缩短关键路径,如图3所示。

在流水线结构的FIR滤波器中,启动当前的迭代计算时,节点2的加法器正在完成前次迭代结果的计算。因此,这时的关键路径由1个乘法器和2个加法器的时间缩短为1个乘法器和1个加法器的时间。

采用在结构中适当插入流水线锁存器来减小关键路径长度的流水技术时,锁存器的插入并不是随意的。当把数据流图切开时,数据方向要一致向前。这样加入的流水线,才不会影响功能。图3中,插入流水线锁存器时,就是沿着结构中数据流的正向,在上下两个路径均加入了锁存器,这样FIR滤波器的逻辑才不会混乱。一种结构的速度(时钟周期),通常由任意两个锁存器之间、一个输入与一个锁存器间、一个锁存器与一个输出间或输入与输出间路径中最长的路径限定。流水线锁存器可以有效地缩短最长路径。

除了以上两种FIR滤波结构外,还有一种数据广播结构的FIR数字滤波器,这种结构通过转置结构来缩短关键路径,同时不需要引入任何的流水线锁存器。具体的改造方法是:改变输入和输出;颠倒信号流程的方向;由一个分支来取代加法器,反之亦然。数据广播结构的FIR数字滤波器如图4所示。

在这种结构中,数据不是存储下来,而是同时广播到所有的乘法器。这种结构的关键路径和图3中插人流水线锁存器的FIR滤波器结构的关键路径一样。但是对输入不需要额外的移位寄存器,对部分积的和也不需要额外的流水线就能达到很高的通过率。这就是FIR滤波器数据广播结构的优点。

本文在设计空域滤波算法电路时,就是分别采取了以上介绍的3种不同的FIR数字滤波器结构形式。

2.2 乘法器模块的硬件设计

从式(1)的模板运算表达式和式(2)的FIR滤波器表达式可以看出,完成模板运算和实现FIR数字滤波还有一个重要的环节,就是乘法运算。乘法器模块是影响空域滤波算法的运算速度的关键模块之一。

乘法运算基本上可以分为两步:一是求出所有的基本乘积项,二是将所有的基本乘积项相加。因此,要设计快速的乘法器电路模块,就要针对这两步进行改进,一方面要减少部分积的数目,同时另一方面要提高部分积求和阵列的累加速度。因此,为了加快乘法器模块的运算速度,在设计乘法器电路时,特别考虑到了采用基4-BOOTH算法来减少部分和的数目,同时采用Wallace Tree减少阵列乘法器中部分积加法阵列的进位传输延迟,加快整个加法阵列的运算速度。

基4-BOOTH算法的基本原理是对乘数进行编码,根据编码表来产生部分积,一次只考虑3位:本位、相邻高位、相邻低位。Wallace Tree比较规则,易于布局布线,这种方法不是直接将所有的部分积完全的一对一地相加,而是采用将各个部分积中具有相同权重的数据位相加合并。通常采用全加器(Full Adder)来完成相同权重的位相加。采用一位全加器,那么Wallace树的每一层,就可以将部分积的向量数目按照3:2的比例缩减。也可以采用2个全加器,来获得4:2的缩减比例。本文中采用3:2计数器(全加器)来进行部分和缩减,这样当部分积的数目很多时,采用Wallace Tree乘法器来缩减部分和速度很快。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)