子带分解的自适应滤波器的FPGA实现

时间:11-09

来源:互联网

点击:

自适应滤波器已经广泛应用于信道均衡、回声取消、系统识别、频谱估计等各个方面。基于子带分解的自适应滤波在提高收敛性能的同时又节省了一定的计算量。基于子带分解的自适应滤波是先将输入信号与参考信号经过分解滤波器组进行子带分解、抽取、子带自适应滤波、内插、通过合成滤波器组得到输出信号。基于子带分解的自适应滤波器的优点:

(1)由于对信号的抽取,使完成自适应滤波所需的计算量得以减少;

(2)在子带进行自适应滤波使收敛性能有所提高。

1 基于子带分解的自适应滤波结构

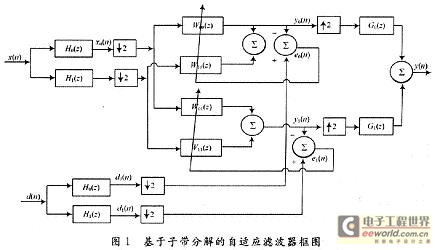

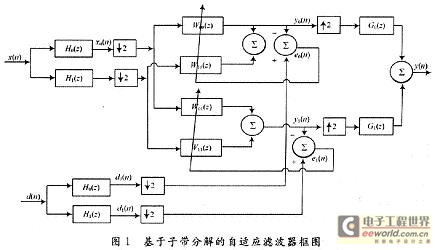

基于子带分解的自适应滤波,其时域结构如图1所示。将输入信号x(n)和参考信号d(n)分别进行子带分解,抽取,在子带上进行自适应滤波,再将子带上的估计信号y0(n)和y1(n)经内插和合成滤波器组得到最后的合成信号。其中滤波器W00(n)和W11(n)是两个子带上的自适应滤波器,而W01(n)和W10(n)表示子带间自适应滤波器。这是由于滤波器组均是FIR滤波器,不可能有锐截止的理想特性,只能以长度为代价来换取近似的特性;这时在严格采样下得到的子带信号必然有混叠,需加入子带间滤波以消除其影响。这里的子带自适应滤波器采用基于NLMS算法自适应滤波器。NLMS算法和LMS算法相比。虽然计算量稍有增加,但可使得自适应滤波器收敛速度大大提高。

2 双通道滤波器组的设计

本文采用的分析和综合滤波器之间的关系如下:

H1(z)=H0(-z),G1(z)=-2H0(-z),G0(z)=2H1(-z)。由上述表达式可知设计的关键是设计H0(z),只要H0(z)确定,H1(z),G0(z),G1(z)也可确定。本文采用等波纹逼近设计法进行滤波器设计。该方法设计的滤波器呈现等波纹频响特性。等波纹逼近设计法设计的滤波器具有如下优点:

(1)由于误差均匀分布于整个频带,对固定的阶数N,可以得到最优良的滤波特性;

(2)通带最平坦,阻带最小衰减达到最大。

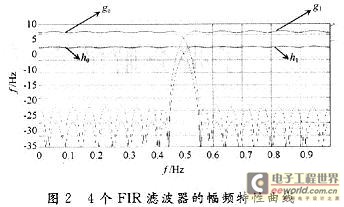

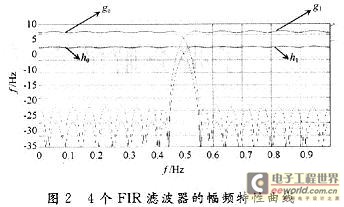

Matlab集成了一套强大的滤波器设计工具FDATOOL,可以完成多种滤波器的设计、分析和性能评估。本文中FPGA硬件实现部分用到的4个FIR滤波器的频率特性曲线见图2。

3 系统建模与仿真

DSP Builder是Altera公司推出的一个面向DSP开发的系统级工具,它是作为Matlab的一个Simulink工具箱(ToolBox)出现的。DSP Bui-lder作为Simulink中的一个工具箱,使得在使用FPGA设计DSP系统时完全可以通过Simulink的图形化界面进行,只需简单地进行DSP Builder工具箱中的模块调用即可。

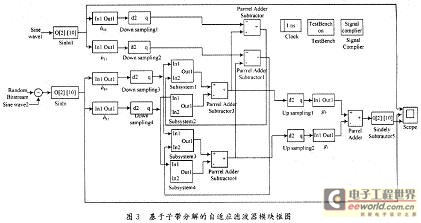

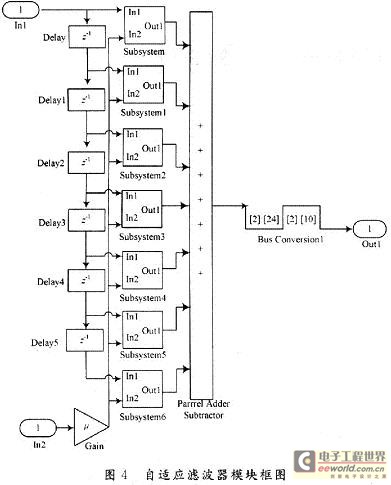

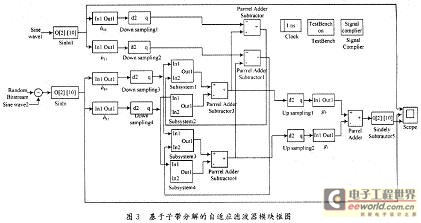

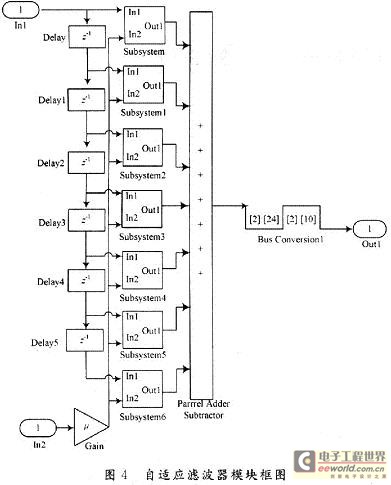

图3中的基于子带分解的自适应滤波器模块框图系统由分析滤波器子系统h00,h01,h10,h11,综合滤波器子系统g00,g01、抽取,插值,加法,减法器,自适应滤波器等模块组成。h00和h10是完全一模一样的低通滤波器,h01和h11是完全一模一样的高通滤波器。h00,h01,g00,g01的幅频特性曲线见图2。h00对应图2中的h0,h01对应图中的h1,g00对应图中的g0,g01对应图中的g1。Subysteml,Subyst-em2,Subystem3,Subystem4是自适应滤波器。Subystem2,Subystem3自适应滤波器的阶数是Subysteml,Subystem4阶数的1/20。期望信号由sine wavel模块提供,输入信号由Sine wave2和Random Bitstream叠加在一起的信号组成。系统所需的模块都是直接调用DSP builder中的模块。Subystem2是7阶NLMS算法自适应滤波器,其框图见图4。如果调高提高收敛速度,则可增加延迟模块、自适应子系统模块,加法器模块即可,但需消耗更多的硬件资源。

自适应滤波器模块主要由延迟单元,权值更新子系统、加法器模块,乘法器模块组成。它是将抽取过后的信号进行自适应滤波。

FIR滤波器的单位冲激响应是有限长的,其z变换为

。分析和综合滤波器系统主要由延迟单元、加法器、加法器模块组成。分析和综合滤波器不可能有锐截止的理想特性,必须通过增加阶数来逼近。分析滤波器子系统h00,h01,h10,h11,综合滤波器子系统g00,g01均采用横截型结构。

权值更新子系统模块主要由乘法器、除法器、加法器、延迟单元、总线类型转换等模块组成。该子系统主要完成滤波器的权值更新。w(k+1)=w(k)+μ/γ+xT(k)x(k)e(k)x(k)运算和wi(k)xi(k)运算。

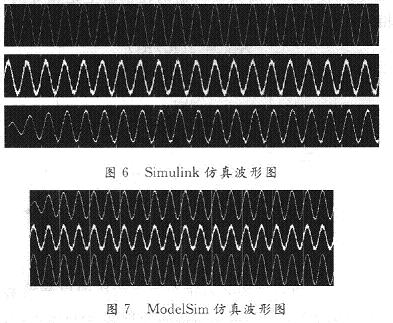

4 仿真

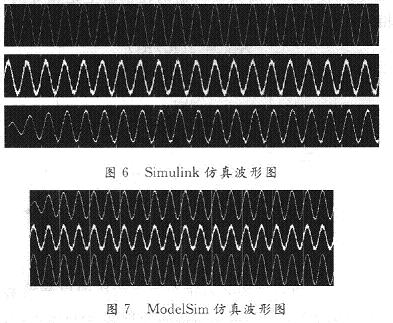

Matlab的Simulink环境具有强大的图形化仿真验证功能,用DSP Builder模块设计好一个新的模型后,可以直接在Simulink中进行算法级、系统级仿真验证。该设计的Simulink仿真如图6所示,输出信号含有毛刺,这说明输出信号与期望信号还有一定的稳态误差。可以通过增加滤波器的阶数,或修改步长控制参数μ,以达到更好的效果。

运行Signal complier可将通过Simulink的模块文件(.mdl)转换成通过的硬件描述语言VHDL文件;运行Testbench(测试平台)可将Sine wavel、Sinewavel+noise、Clock转换成针对HDL仿真器ModelSim的测试文件。由图7可知输出信号Sine out逐渐趋于稳定,逼近与期望信号sine wavel,因此设计结果满足要求,能够实现自适应过程。

(1)由于对信号的抽取,使完成自适应滤波所需的计算量得以减少;

(2)在子带进行自适应滤波使收敛性能有所提高。

1 基于子带分解的自适应滤波结构

基于子带分解的自适应滤波,其时域结构如图1所示。将输入信号x(n)和参考信号d(n)分别进行子带分解,抽取,在子带上进行自适应滤波,再将子带上的估计信号y0(n)和y1(n)经内插和合成滤波器组得到最后的合成信号。其中滤波器W00(n)和W11(n)是两个子带上的自适应滤波器,而W01(n)和W10(n)表示子带间自适应滤波器。这是由于滤波器组均是FIR滤波器,不可能有锐截止的理想特性,只能以长度为代价来换取近似的特性;这时在严格采样下得到的子带信号必然有混叠,需加入子带间滤波以消除其影响。这里的子带自适应滤波器采用基于NLMS算法自适应滤波器。NLMS算法和LMS算法相比。虽然计算量稍有增加,但可使得自适应滤波器收敛速度大大提高。

2 双通道滤波器组的设计

本文采用的分析和综合滤波器之间的关系如下:

H1(z)=H0(-z),G1(z)=-2H0(-z),G0(z)=2H1(-z)。由上述表达式可知设计的关键是设计H0(z),只要H0(z)确定,H1(z),G0(z),G1(z)也可确定。本文采用等波纹逼近设计法进行滤波器设计。该方法设计的滤波器呈现等波纹频响特性。等波纹逼近设计法设计的滤波器具有如下优点:

(1)由于误差均匀分布于整个频带,对固定的阶数N,可以得到最优良的滤波特性;

(2)通带最平坦,阻带最小衰减达到最大。

Matlab集成了一套强大的滤波器设计工具FDATOOL,可以完成多种滤波器的设计、分析和性能评估。本文中FPGA硬件实现部分用到的4个FIR滤波器的频率特性曲线见图2。

3 系统建模与仿真

DSP Builder是Altera公司推出的一个面向DSP开发的系统级工具,它是作为Matlab的一个Simulink工具箱(ToolBox)出现的。DSP Bui-lder作为Simulink中的一个工具箱,使得在使用FPGA设计DSP系统时完全可以通过Simulink的图形化界面进行,只需简单地进行DSP Builder工具箱中的模块调用即可。

图3中的基于子带分解的自适应滤波器模块框图系统由分析滤波器子系统h00,h01,h10,h11,综合滤波器子系统g00,g01、抽取,插值,加法,减法器,自适应滤波器等模块组成。h00和h10是完全一模一样的低通滤波器,h01和h11是完全一模一样的高通滤波器。h00,h01,g00,g01的幅频特性曲线见图2。h00对应图2中的h0,h01对应图中的h1,g00对应图中的g0,g01对应图中的g1。Subysteml,Subyst-em2,Subystem3,Subystem4是自适应滤波器。Subystem2,Subystem3自适应滤波器的阶数是Subysteml,Subystem4阶数的1/20。期望信号由sine wavel模块提供,输入信号由Sine wave2和Random Bitstream叠加在一起的信号组成。系统所需的模块都是直接调用DSP builder中的模块。Subystem2是7阶NLMS算法自适应滤波器,其框图见图4。如果调高提高收敛速度,则可增加延迟模块、自适应子系统模块,加法器模块即可,但需消耗更多的硬件资源。

自适应滤波器模块主要由延迟单元,权值更新子系统、加法器模块,乘法器模块组成。它是将抽取过后的信号进行自适应滤波。

FIR滤波器的单位冲激响应是有限长的,其z变换为

。分析和综合滤波器系统主要由延迟单元、加法器、加法器模块组成。分析和综合滤波器不可能有锐截止的理想特性,必须通过增加阶数来逼近。分析滤波器子系统h00,h01,h10,h11,综合滤波器子系统g00,g01均采用横截型结构。

权值更新子系统模块主要由乘法器、除法器、加法器、延迟单元、总线类型转换等模块组成。该子系统主要完成滤波器的权值更新。w(k+1)=w(k)+μ/γ+xT(k)x(k)e(k)x(k)运算和wi(k)xi(k)运算。

4 仿真

Matlab的Simulink环境具有强大的图形化仿真验证功能,用DSP Builder模块设计好一个新的模型后,可以直接在Simulink中进行算法级、系统级仿真验证。该设计的Simulink仿真如图6所示,输出信号含有毛刺,这说明输出信号与期望信号还有一定的稳态误差。可以通过增加滤波器的阶数,或修改步长控制参数μ,以达到更好的效果。

运行Signal complier可将通过Simulink的模块文件(.mdl)转换成通过的硬件描述语言VHDL文件;运行Testbench(测试平台)可将Sine wavel、Sinewavel+noise、Clock转换成针对HDL仿真器ModelSim的测试文件。由图7可知输出信号Sine out逐渐趋于稳定,逼近与期望信号sine wavel,因此设计结果满足要求,能够实现自适应过程。

滤波器 FPGA 仿真 DSP Altera 低通滤波器 总线 VHDL ModelSim 相关文章:

- 数字下变频的FPGA实现(05-12)

- 用FPGA实现音频采样率的转换(02-07)

- 基于FPGA的任意时延伪码序列产生方法(04-12)

- 基于FPGA实现变采样率FIR滤波器的研究(04-13)

- 基于CPLD的CCD信号发生器的研究(04-08)

- 利用FPGA和CPLD数字逻辑实现ADC(06-04)