如何用FPGA实现原型板原理图的验证

时间:11-09

来源:互联网

点击:

FPGA原型板网表的仿真

至此顶层Verilog文件中包含了原型板上除工具删除的元件外的所有元件。设计师可以复用DUT功能验证使用的已有仿真环境。这种方法的优点在于,可以复用相同的测试向量和验证环境验证原理图。

任何验证环境的基本原理都是一样的,即为DUT提供某种形式的测试向量,然后对测试结果与期望值进行比较。根据设计的复杂性有多种达成的方式。通过下面这个非常简单的例子就很好理解了。例子是一个基于x86处理器的SOC。为了简单起见,我们只考虑图1所示SOC中的少量重要元件。DUT由x86处理器、主桥(Host Bridge)、SDRAM控制器和PCI桥组成。在验证环境中,为了提高仿真速度,可以把x86处理器看作是一个BFM,同时提供某种PCI从模型。简单地说,x86 BFM具有某种形式的读/写命令,能产生总线周期,因此设计可以运行起来。

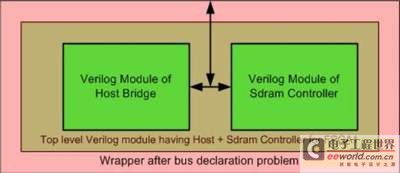

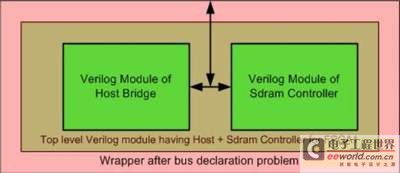

图3:Verilog模块创建wrapper以匹配元件的引脚

如图2所示,主桥和SDRAM控制器被映射进FPGA1,PCI桥被映射时FPGA2。由脚本产生的顶层Verilog文件包含如图2所示的所有元件。至此就可以在验证环境中方便地使用这个顶层Verilog文件,并附于相同的验证测试向量。要注意的是还需要为各个Verilog模块创建wrapper以匹配元件的引脚。对于SDRAM和PCI槽道来说,可以使用与RTL验证环境中使用的相同模型(即SDRAM模型和PCI主/从模型)。参考图3,将FPGA1作为案例进行说明。

由于只对环境作了少量修改,如在编译列表中增加很少的Verilog文件(wrapper模型),用新创建的文件替换顶层文件,因此可以对原理图列表实施验证。这些事情可以通过简单的perl或shell脚本实现自动处理,整个任务将减少到仅指定一些特殊选项,同时从命令行运行仿真。

如果有任何错误的连接,或某些连接被遗忘,那么仿真结果就会有相应的提示。这种方法可以实现对与模拟元件的连接的部分测试,因为这部分元件有的从网表中删除了,有的被等效行为模型所代替。然而,有些错误还是可以被检出的。

硅片生成板网表的仿真

上述方法同样可以用来仿真设计用于测试最终硅片的电路板的网表。这种方法更适用于对这些板的验证,因为正常情况下制造出来的许多板其芯片的并行测试都是可以完成的。此外,通过某种途径配置FPGA引脚可以消除基于FPGA的板上的错误。下面继续以上文的例子说明如何将同一概念应用到硅片生成板上。

如图1所示,硅片等效于DUT。根据相同的流程创建一个Verilog网表,这个网表将DUT看作是板上的一个芯片和其它外围设备。这是在验证环境中必须使用的顶层文件。现在我们已经有了DUT的完整Verilog描述,因此只需要创建图4所示的Verilog wrapper,让引脚输出与电路板上的芯片相匹配。

综上所述,这个网表是可以利用以前使用的同一测试向量进行操作的。

本文小结

这种方法已经过测试,目前正用于原理图的验证。该方法为原理图验证增加了新的方案。原型/生成板的原理图的验证和错误检测可以在极易产生严重问题并影响设计周期的早期阶段进行。另外,验证无需额外的开销,因为这种方法基于的是业界常说的‘复用’原理,在本案例中复用的是测试向量和验证环境。

图4:Verilog wrapper让引脚输出与电路板上的芯片相匹配

至此顶层Verilog文件中包含了原型板上除工具删除的元件外的所有元件。设计师可以复用DUT功能验证使用的已有仿真环境。这种方法的优点在于,可以复用相同的测试向量和验证环境验证原理图。

任何验证环境的基本原理都是一样的,即为DUT提供某种形式的测试向量,然后对测试结果与期望值进行比较。根据设计的复杂性有多种达成的方式。通过下面这个非常简单的例子就很好理解了。例子是一个基于x86处理器的SOC。为了简单起见,我们只考虑图1所示SOC中的少量重要元件。DUT由x86处理器、主桥(Host Bridge)、SDRAM控制器和PCI桥组成。在验证环境中,为了提高仿真速度,可以把x86处理器看作是一个BFM,同时提供某种PCI从模型。简单地说,x86 BFM具有某种形式的读/写命令,能产生总线周期,因此设计可以运行起来。

图3:Verilog模块创建wrapper以匹配元件的引脚

如图2所示,主桥和SDRAM控制器被映射进FPGA1,PCI桥被映射时FPGA2。由脚本产生的顶层Verilog文件包含如图2所示的所有元件。至此就可以在验证环境中方便地使用这个顶层Verilog文件,并附于相同的验证测试向量。要注意的是还需要为各个Verilog模块创建wrapper以匹配元件的引脚。对于SDRAM和PCI槽道来说,可以使用与RTL验证环境中使用的相同模型(即SDRAM模型和PCI主/从模型)。参考图3,将FPGA1作为案例进行说明。

由于只对环境作了少量修改,如在编译列表中增加很少的Verilog文件(wrapper模型),用新创建的文件替换顶层文件,因此可以对原理图列表实施验证。这些事情可以通过简单的perl或shell脚本实现自动处理,整个任务将减少到仅指定一些特殊选项,同时从命令行运行仿真。

如果有任何错误的连接,或某些连接被遗忘,那么仿真结果就会有相应的提示。这种方法可以实现对与模拟元件的连接的部分测试,因为这部分元件有的从网表中删除了,有的被等效行为模型所代替。然而,有些错误还是可以被检出的。

硅片生成板网表的仿真

上述方法同样可以用来仿真设计用于测试最终硅片的电路板的网表。这种方法更适用于对这些板的验证,因为正常情况下制造出来的许多板其芯片的并行测试都是可以完成的。此外,通过某种途径配置FPGA引脚可以消除基于FPGA的板上的错误。下面继续以上文的例子说明如何将同一概念应用到硅片生成板上。

如图1所示,硅片等效于DUT。根据相同的流程创建一个Verilog网表,这个网表将DUT看作是板上的一个芯片和其它外围设备。这是在验证环境中必须使用的顶层文件。现在我们已经有了DUT的完整Verilog描述,因此只需要创建图4所示的Verilog wrapper,让引脚输出与电路板上的芯片相匹配。

综上所述,这个网表是可以利用以前使用的同一测试向量进行操作的。

本文小结

这种方法已经过测试,目前正用于原理图的验证。该方法为原理图验证增加了新的方案。原型/生成板的原理图的验证和错误检测可以在极易产生严重问题并影响设计周期的早期阶段进行。另外,验证无需额外的开销,因为这种方法基于的是业界常说的‘复用’原理,在本案例中复用的是测试向量和验证环境。

图4:Verilog wrapper让引脚输出与电路板上的芯片相匹配

快速原型 FPGA 仿真 电路 Verilog VHDL 总线 电容 电阻 电感 相关文章:

- 基于FPGA的液晶显示驱动IP核的实现(07-24)

- 使用新型Virtex FPGA开发小型软件无线电平台SFF SDR(09-17)

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)