基于SoPC目标板Flash编程设计的创建及应用

时间:11-08

来源:互联网

点击:

4 目标板Flash编程设计的应用

以一个最小SoPC系统流水灯为例,说明目标板Flash编程设计在实际Flash编程中的应用。

4.1 NiosII CPU生成

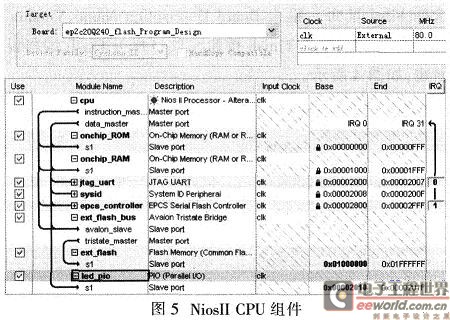

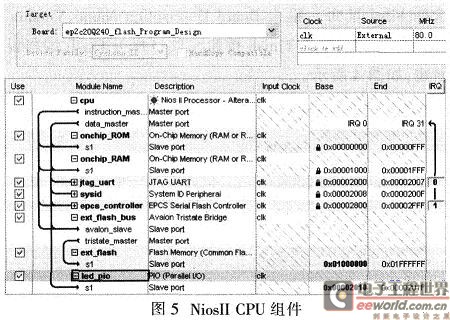

在Altera SoPC Builder图形界面中,首先在Target选项区中Board下拉列表框中选择刚创建的目标板Flash编程设计,并指定NiosII系统的时钟。然后添加系统所需的外设元件,设置各外设元件的参数。分配Base Address和IRQ。添加完组件后如图5所示。

添加完组件后,在Nios II More“cpu”Settings中设置复位地址和异常地址。如果Nios程序下载到Flash中,则复位地址设为ext_flash;如果下载到EPCS中,则复位地址设为epcs_controller。最后在System Generation中点击Generation按钮生成NiosII CPU。

4.2 构建最小SOPC系统

在QuartusII中构建最小SoPC系统。此SoPC系统由NiosII CPU模块、PLL模块和系统复位模块组成。在系统的顶层模块中分别添加SoPC Builder生成的NiosII CPU,PLL模块及系统复位模块构成最小的SoPC系统。由于目标板上时钟是50 MHz,而构建NiosII CPU时钟设为80 MHz,故需通过Mega Wizard Plug-In Manager生成PLL模块,将系统时钟提高到80 MHz。添加完模块后,再添加输入/输出端口,并连接引脚与端口,命名端口名(建议端口命名与实际电路中的网络标号相同)。然后分配引脚,并设置相关参数。编译工程生成FPGA的配置文件*.sof,并利用QuartusII的Programmer下载到FPGA或EPCS中。

4.3 Nios程序生成及Flash编程

启动NiosII IDE,建立和编译一个简单的LED流水灯的Nios应用程序。在Nios应用程序调试正确后,单击菜单[Tools]下的[Flash Programmer],弹出Flash Programmer编程界面。选中Flash Programmer,单击New按钮创建一个FlashProgrammer配置。在Flash Programmer界面中选择Main选项卡,设置Flash Programmer相关参数。

如果选中Program software project into flash memory project项,表示将工程的*.elf文件写入Flash(EPCS或CFI Flash)存储器中。将*.elf文件写入Flash的过程时,如果工程没有编译连接,会自动进行工程的编译连接。对于*.elf文件的编程,Flash Programmer窗口中并没有存储器和偏移地址的设置,存储器和偏移地址由是SOPC Builder中Reset Address指向的存储器和设置的偏移地址决定。如果将ResetAddress指向CFI F1ash.偏移地址从0x0HD开始,那么FlashProgrammer就会从CFI Flash的基地址+0x00开始烧写数据;如果将Reset Address指向epcs_controller,偏移地址从Ox00开始,那么Flash Programmer就会从EPCS的基地址+配置数据空间+Ox00开始烧写数据。

如果选中Program FPGA configuration data into hardware-image region of flash memory,可将FPGA配置数据写入Flash(EPCS或CFI Flash)。选择作为硬件系统的FPGA配置文件*.sof,指定配置文件的硬件配置映像名及存储的偏移地址。如果在制作目标板Flash编程设计时,指定可将配置文件编程到CFIFlash,并指定多个偏移地址,此项就可选择编程地址,从而将配置文件编程到用户指定的存储器地址空间。对于将配置文件编程到EPCS,偏移地址只能从Ox00开始。如果选择Program file into a flash memory选项,能将指定的二进制文件写入指定的Flash(EPCS或CFI Flash)存储地址空间。

在Flash Programmer界面中选择Target Connection选项卡,设置当前所用的下载电缆及JTAG器件。然后单击Program F1ash对Flash进行编程(EPCS或CFIFlash)。如果看到图6所示的提示消息,则Flash编程已经成功,说明目标板Flash编程设计创建成功。

5 结语

实现SoPC目标板Flash编程设计的创建,并通过一个最小SoPC系统说明目标板Flash编程设计在Flash编程中的应用及Flash编程的方法。通过实验验证了目标板Flash编程设计创建方法的正确性,并能对Flash编程。

以一个最小SoPC系统流水灯为例,说明目标板Flash编程设计在实际Flash编程中的应用。

4.1 NiosII CPU生成

在Altera SoPC Builder图形界面中,首先在Target选项区中Board下拉列表框中选择刚创建的目标板Flash编程设计,并指定NiosII系统的时钟。然后添加系统所需的外设元件,设置各外设元件的参数。分配Base Address和IRQ。添加完组件后如图5所示。

添加完组件后,在Nios II More“cpu”Settings中设置复位地址和异常地址。如果Nios程序下载到Flash中,则复位地址设为ext_flash;如果下载到EPCS中,则复位地址设为epcs_controller。最后在System Generation中点击Generation按钮生成NiosII CPU。

4.2 构建最小SOPC系统

在QuartusII中构建最小SoPC系统。此SoPC系统由NiosII CPU模块、PLL模块和系统复位模块组成。在系统的顶层模块中分别添加SoPC Builder生成的NiosII CPU,PLL模块及系统复位模块构成最小的SoPC系统。由于目标板上时钟是50 MHz,而构建NiosII CPU时钟设为80 MHz,故需通过Mega Wizard Plug-In Manager生成PLL模块,将系统时钟提高到80 MHz。添加完模块后,再添加输入/输出端口,并连接引脚与端口,命名端口名(建议端口命名与实际电路中的网络标号相同)。然后分配引脚,并设置相关参数。编译工程生成FPGA的配置文件*.sof,并利用QuartusII的Programmer下载到FPGA或EPCS中。

4.3 Nios程序生成及Flash编程

启动NiosII IDE,建立和编译一个简单的LED流水灯的Nios应用程序。在Nios应用程序调试正确后,单击菜单[Tools]下的[Flash Programmer],弹出Flash Programmer编程界面。选中Flash Programmer,单击New按钮创建一个FlashProgrammer配置。在Flash Programmer界面中选择Main选项卡,设置Flash Programmer相关参数。

如果选中Program software project into flash memory project项,表示将工程的*.elf文件写入Flash(EPCS或CFI Flash)存储器中。将*.elf文件写入Flash的过程时,如果工程没有编译连接,会自动进行工程的编译连接。对于*.elf文件的编程,Flash Programmer窗口中并没有存储器和偏移地址的设置,存储器和偏移地址由是SOPC Builder中Reset Address指向的存储器和设置的偏移地址决定。如果将ResetAddress指向CFI F1ash.偏移地址从0x0HD开始,那么FlashProgrammer就会从CFI Flash的基地址+0x00开始烧写数据;如果将Reset Address指向epcs_controller,偏移地址从Ox00开始,那么Flash Programmer就会从EPCS的基地址+配置数据空间+Ox00开始烧写数据。

如果选中Program FPGA configuration data into hardware-image region of flash memory,可将FPGA配置数据写入Flash(EPCS或CFI Flash)。选择作为硬件系统的FPGA配置文件*.sof,指定配置文件的硬件配置映像名及存储的偏移地址。如果在制作目标板Flash编程设计时,指定可将配置文件编程到CFIFlash,并指定多个偏移地址,此项就可选择编程地址,从而将配置文件编程到用户指定的存储器地址空间。对于将配置文件编程到EPCS,偏移地址只能从Ox00开始。如果选择Program file into a flash memory选项,能将指定的二进制文件写入指定的Flash(EPCS或CFI Flash)存储地址空间。

在Flash Programmer界面中选择Target Connection选项卡,设置当前所用的下载电缆及JTAG器件。然后单击Program F1ash对Flash进行编程(EPCS或CFIFlash)。如果看到图6所示的提示消息,则Flash编程已经成功,说明目标板Flash编程设计创建成功。

5 结语

实现SoPC目标板Flash编程设计的创建,并通过一个最小SoPC系统说明目标板Flash编程设计在Flash编程中的应用及Flash编程的方法。通过实验验证了目标板Flash编程设计创建方法的正确性,并能对Flash编程。

集成电路 嵌入式 SoC 电路 FPGA Altera 单片机 CPLD PCB Quartus LED 相关文章:

- 周立功:如何兼顾学习ARM与FPGA(05-23)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- FPGA 重复配置和测试的实现(08-14)

- 适用于消费性市场的nano FPGA技术(09-27)

- 赛灵思“授之以渔”理论:危机中如何巧降成本(06-04)