多通道同步数据采集及压缩系统的设计方案

时间:11-08

来源:互联网

点击:

4 DSP部分设计

4.1 DSP程序设计流程

设备上电DSP复位后,由其内部固化的自引导程序(BOOT)将存于Flash存储器的程序和数据搬移至内部RAM中,然后DSP开始读取压缩算法的应用程序,继续运行。DSP的工作流程为:首先初始化DSP的CSL函数库,然后初始化PLL、GPIO及相关中断寄存器,等待中断。

采集模块16位数据通过总线不断写入。FIFO1中。程序通过控制其半满(HF)信号,即当数据超过半满时,HF信号低电平有效,将触发一次中断通知 DSP,DSP则进入中断后把2048字节的数据从输入FIFO1中读入到DSP所指向的SDRAM的空间中,DSP在处理完中断的空闲时间内进行高速压缩。将压缩数据与原数据相比较,若压缩数据小于原数据,就把压缩数据写入DSP的软FIFO中,否则,就将原数据写入DSP的软FIFO中。

最终,DSP把软FIFO中得压缩数据写入输出FIFO2中,等待发送模块将数据上传至遥测系统。

4.2 数据压缩算法选择

压缩编码信源信息在解压缩时能够完全恢复,也即在压缩和解压缩过程中信源信息无损失,该编码方法称为无损压缩,经常使用的无损压缩方法有Shannon-Fano编码,Huffman编码,游程(Run-length)编码,IZW (Lempel-Ziv-Welch)编码和算术编码(ARC)等。这里重点讨论ARC算法和LZW算法。ARC算法的思想就像查字典。众所周知.英文词典的编排方式是按首字母排序,首字母相同的词继续按第二字母排序,以此类推。实际应用算术编码更巧妙。利用字符出现的概率对0~1区间分割,然后用0~1 之间的一个小数对数据编码,原始数据越多,这个小数点后的位数就越多。

LZW编码是围绕称为词典的转换表完成的。该转换表用来存放称为前缀(Prefix)的字符序列,并且为每个表项分配一个码字(Code word),或称为序号,这张转换表实际上是把8位ASCII字符集进行扩充。增加的符号用来表示在文本或图像中出现的可变长度ASCII字符串。扩充后的代码可用9~12位甚至更多的位表示。12位有4 096个不同的12位代码,这就是说。转换表有4 096个表项,其中256个表项用于存放已定义的字符,剩下的3 840个表项用于存放前缀(Prefix)。LZW编码器(软件编码器或硬件编码器)通过管理该词典完成输入与输出之间的转换。LZW编码器的输入是字符流(Charstream),字符流是用8位ASCII字符组成的字符串,输出是用n位(例如12位)表示的码字流(Codestream),码字代表单个字符或多个字符组成的字符串。LZW编码器采用一种实用的分析(parsing)算法,称为贪婪分析算法(greedy parsingalgorithm)。

在贪婪分析算法中,每一次分析都要串行检查来自字符流(Charstream)的字符串,从中分解出已识别的最长字符串,也就是已在词典中出现的最长的前缀(Prefix)。用已知的前缀(Prefix)加上下一个输入字符C也就是当前字符(Currentcharacter)作为该前缀的扩展字符,形成新的扩展字符串——缀一符串(Sning):Prefix.C。这个新的缀一符串(String)是否要加到词典中,还要看词典中是否存有和它相同的缀一符串(String)。

如果有,那么这个缀一符串(String)就变成前缀(Prefix),继续输入新的字符,否则就把这个缀一符串字符(String)写到词典中生成一个新的前缀(Prefix),并给一个代码。

一般来说,不同的压缩算法有不同的优缺点。不同算法的复杂性对空间的要求以及压缩率也不同。这不仅依赖于压缩方法,也与被压缩数据的特点有关。

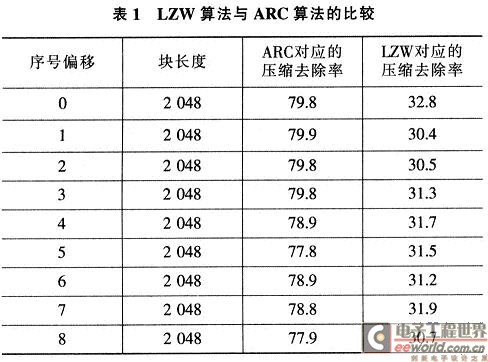

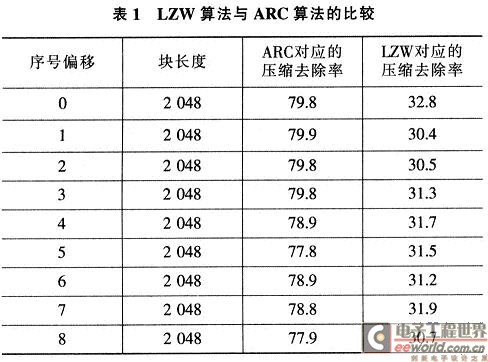

该系统设计是压缩实时数据,要求压缩过程的时间性能较高,故采用事先统计模型的ARC算法。实验证明,采用该算法其运算速度与LZW算法速度相近。而ARC算法在压缩去除率上优于LZW算法。

5 实验结果

算法选择主要从压缩速度和压缩去除率进行比较。该设计中前端以27 kHz的速度实时采集某系统多路噪声压缩,从表1中可知ARC算法针对不同分组段的数据压缩去除率约为79%,而LZW算法,在该分组段压缩去除率仅约 31%,可见ARC压缩算法的压缩去除率比较高。实验中通过上位机发送一定规律数据,经过该系统压缩数据处理,压缩后数据再通过上位机解包、解压,还原的数据与原始数据相比对。其结果一致,证明系统安全可靠。图3为上位机解压报表。

6 结束语

详细介绍了系统组成,采用复杂可编程逻辑器件(CPLD)和数字信号处理器(DSP)的体系结构,对无损压缩的相关算法进行比较,最终采用算术编码 (ARC)作为系统压缩算法。本系统创新点在于采集模块的多通道同步性以及对噪声数据压缩的针对性。最后通过大量实验,证实本方案切实可行,各项指标满足系统要求。

4.1 DSP程序设计流程

设备上电DSP复位后,由其内部固化的自引导程序(BOOT)将存于Flash存储器的程序和数据搬移至内部RAM中,然后DSP开始读取压缩算法的应用程序,继续运行。DSP的工作流程为:首先初始化DSP的CSL函数库,然后初始化PLL、GPIO及相关中断寄存器,等待中断。

采集模块16位数据通过总线不断写入。FIFO1中。程序通过控制其半满(HF)信号,即当数据超过半满时,HF信号低电平有效,将触发一次中断通知 DSP,DSP则进入中断后把2048字节的数据从输入FIFO1中读入到DSP所指向的SDRAM的空间中,DSP在处理完中断的空闲时间内进行高速压缩。将压缩数据与原数据相比较,若压缩数据小于原数据,就把压缩数据写入DSP的软FIFO中,否则,就将原数据写入DSP的软FIFO中。

最终,DSP把软FIFO中得压缩数据写入输出FIFO2中,等待发送模块将数据上传至遥测系统。

4.2 数据压缩算法选择

压缩编码信源信息在解压缩时能够完全恢复,也即在压缩和解压缩过程中信源信息无损失,该编码方法称为无损压缩,经常使用的无损压缩方法有Shannon-Fano编码,Huffman编码,游程(Run-length)编码,IZW (Lempel-Ziv-Welch)编码和算术编码(ARC)等。这里重点讨论ARC算法和LZW算法。ARC算法的思想就像查字典。众所周知.英文词典的编排方式是按首字母排序,首字母相同的词继续按第二字母排序,以此类推。实际应用算术编码更巧妙。利用字符出现的概率对0~1区间分割,然后用0~1 之间的一个小数对数据编码,原始数据越多,这个小数点后的位数就越多。

LZW编码是围绕称为词典的转换表完成的。该转换表用来存放称为前缀(Prefix)的字符序列,并且为每个表项分配一个码字(Code word),或称为序号,这张转换表实际上是把8位ASCII字符集进行扩充。增加的符号用来表示在文本或图像中出现的可变长度ASCII字符串。扩充后的代码可用9~12位甚至更多的位表示。12位有4 096个不同的12位代码,这就是说。转换表有4 096个表项,其中256个表项用于存放已定义的字符,剩下的3 840个表项用于存放前缀(Prefix)。LZW编码器(软件编码器或硬件编码器)通过管理该词典完成输入与输出之间的转换。LZW编码器的输入是字符流(Charstream),字符流是用8位ASCII字符组成的字符串,输出是用n位(例如12位)表示的码字流(Codestream),码字代表单个字符或多个字符组成的字符串。LZW编码器采用一种实用的分析(parsing)算法,称为贪婪分析算法(greedy parsingalgorithm)。

在贪婪分析算法中,每一次分析都要串行检查来自字符流(Charstream)的字符串,从中分解出已识别的最长字符串,也就是已在词典中出现的最长的前缀(Prefix)。用已知的前缀(Prefix)加上下一个输入字符C也就是当前字符(Currentcharacter)作为该前缀的扩展字符,形成新的扩展字符串——缀一符串(Sning):Prefix.C。这个新的缀一符串(String)是否要加到词典中,还要看词典中是否存有和它相同的缀一符串(String)。

如果有,那么这个缀一符串(String)就变成前缀(Prefix),继续输入新的字符,否则就把这个缀一符串字符(String)写到词典中生成一个新的前缀(Prefix),并给一个代码。

一般来说,不同的压缩算法有不同的优缺点。不同算法的复杂性对空间的要求以及压缩率也不同。这不仅依赖于压缩方法,也与被压缩数据的特点有关。

该系统设计是压缩实时数据,要求压缩过程的时间性能较高,故采用事先统计模型的ARC算法。实验证明,采用该算法其运算速度与LZW算法速度相近。而ARC算法在压缩去除率上优于LZW算法。

5 实验结果

算法选择主要从压缩速度和压缩去除率进行比较。该设计中前端以27 kHz的速度实时采集某系统多路噪声压缩,从表1中可知ARC算法针对不同分组段的数据压缩去除率约为79%,而LZW算法,在该分组段压缩去除率仅约 31%,可见ARC压缩算法的压缩去除率比较高。实验中通过上位机发送一定规律数据,经过该系统压缩数据处理,压缩后数据再通过上位机解包、解压,还原的数据与原始数据相比对。其结果一致,证明系统安全可靠。图3为上位机解压报表。

6 结束语

详细介绍了系统组成,采用复杂可编程逻辑器件(CPLD)和数字信号处理器(DSP)的体系结构,对无损压缩的相关算法进行比较,最终采用算术编码 (ARC)作为系统压缩算法。本系统创新点在于采集模块的多通道同步性以及对噪声数据压缩的针对性。最后通过大量实验,证实本方案切实可行,各项指标满足系统要求。

DSP CPLD 传感器 总线 Xilinx 电路 看门狗 编码器 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- FPGA作为协处理器在实时系统中的应用(04-08)

- 学习FPGA绝佳网站推荐!!!(05-23)

- 我的FPGA学习历程(05-23)

- 基于Spartan-3A DSP的安全视频分析(05-01)