基于FPGA的示波器图文显示系统的设计方案

时间:11-08

来源:互联网

点击:

FPGA(Field Programmable Gate Array),即现场可编程门阵列是大规模可编程逻辑器件,可以取代现行所有的全部微机接口芯片,实现微机系统中的存储、地址译码等多种功能。利用 FPGA可以把多个微机系统的功能电路集成在一块芯片上。应用FPGA设计功能电路时,可以让人们的思路从传统的以单片机或DSP芯片为核心的系统集成型转向单一专用芯片型设计。传统的示波器虽然功能齐全,但是体积大、重量重、成本高、等一系列问题使应用受到了限制。有鉴于此,便携式数字存储采集器就应运而生,它采用了LCD显示、高速A/D采集与转换、ASIC芯片等新技术,具有很强的实用性和巨大的市场潜力,也代表了当代电子测量仪器的一种发展趋势,即向功能多、体积小、重量轻、使用方便的掌上型仪器发展。

1 系统总体设计读写

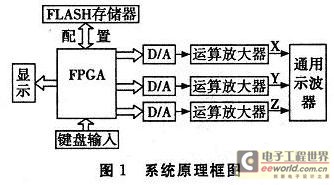

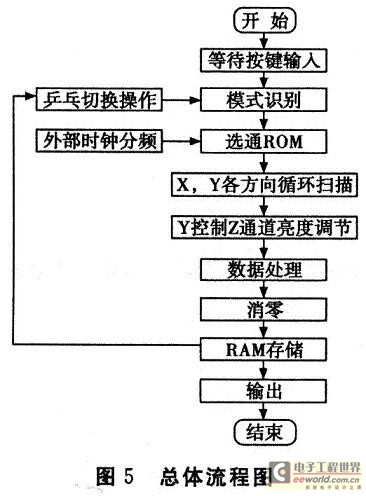

根据设计要求:在示波器上显示2个以上字符或图案,如显示0-9十个数字及英文字符、图象等,结合示波器显示原理,设计电路如图1所示。将要显示的数字或符号进行取模,得到其二进制形式表示。将转换好的数据送入FPGA内部RAM存储。

在设计上我们使用了XILINX的SPARTAN-3芯片,作为控制器,完成总的数控部分、键盘和和显示接口部分的控制。采用八位(或者更高位)D/A转换,对FPGA芯片输出二进制数字量进行数一模转换,在经过高速运算放大器后得到其电压量。分X,Y两路输出给示波器,根据示波器原理,在屏幕上打点显示数字(或者图形)。而Z通道作为另一路独立通道,对显示的数字亮度进行可控显示。

2 系统硬件设计

2.1 总体控制模块

基于本设计,系统控制模块的部分是具有掩膜可编程门阵列的逻辑器件——FPGA。

Spartan系列FPGA是Xilinx公司可编程逻辑产品中的高性价比产品的代表,而Spartan-Ⅲ系列FPGA是为那些需要大容量、低价格电子应用的用户而设计的。本系统使用的是XILINX公司的XC3S200型号芯片,其技术参数如下:

●4 320个逻辑单元;

●系统门密度200 k个;

●CLB阵列24*20,共480个;

●最大用户I/O173,最大差分I/O76;

●分布式RAM容量30 Kbit,Block RAM容量216Kbit;

●嵌入式18x18乘法器支持高性能DSP应用;

●PCI和带有LVDS的高速差分信号。

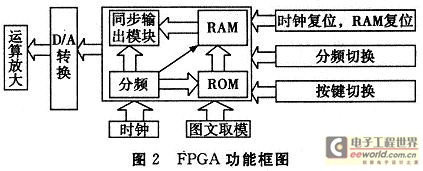

2.2 存储单元模块

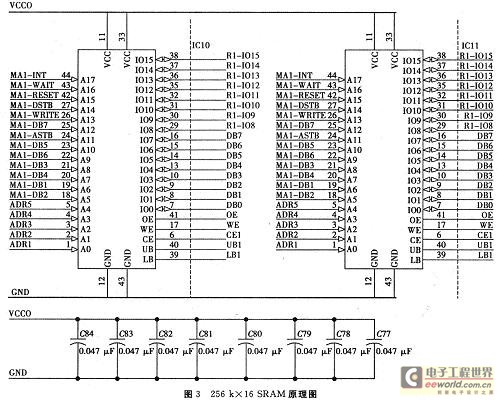

由于FPGA基于CMOS SRAM工艺,不具备掉电保护功能,当无电源供电时,配置的数据丢失,芯片的功能也随之丢失。因此,本设计采用FLASH存储器在线重配置的方法。

2.3 外围电路模块

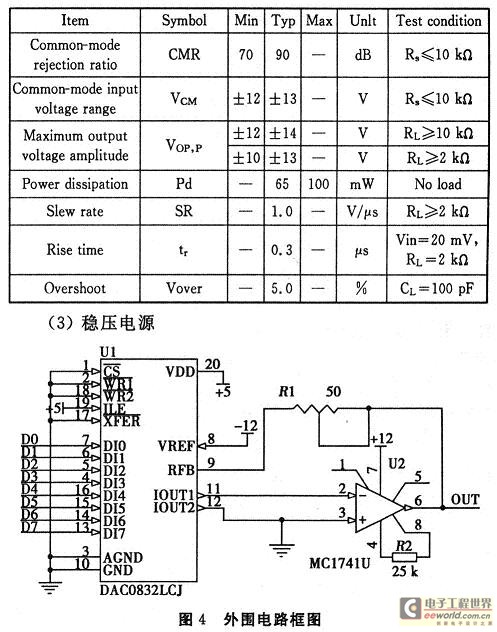

2.3.1 D/A转换

在D/A选择上,我们用的是美国半导体公司的 DAC0832,它具有8位并行、中速(建立时间1 us)、电流型、价格低廉等特点。它有单缓冲工作方式、双缓冲工作方式两种工作方式。单缓冲工作方式时,一个寄存器工作于直通状态,一个工作于受控锁存器状态。在不要求多相D/A同时输出时,可以采用单缓冲方式,此时只需一次写操作,就开始转换,可以提高D/A的数据吞吐量。双缓冲工作方式时,两个寄存器均工作于受控锁存器状态。当要求多个模拟量同时输出时,可采用双重缓冲方式。

它的技术参数为:建立时间1 us;8位并行;低功率损耗20 mW;支持电压:5 V~15 V。

2.3.2 运算放大

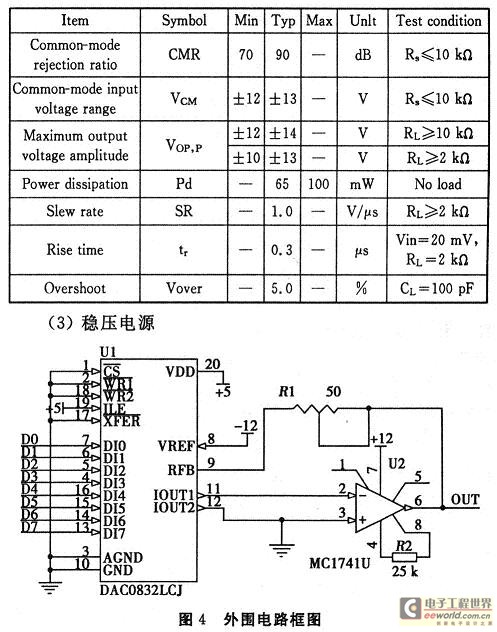

在D/A转换之后,我们得到的是电流信号,而需要输入示波器的为电压信号,因此运用运算放大器来进行转换,同时将运放设计为可调形式,通过调节它便可以调节输出电压的大小,达到控制显示幅值的目的。本设计采用LM741系列运放,其技术指标加下:

3 系统软件设计

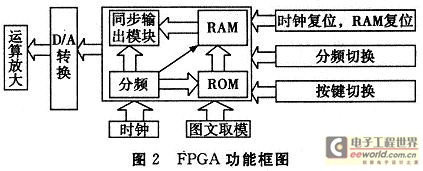

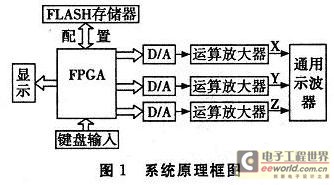

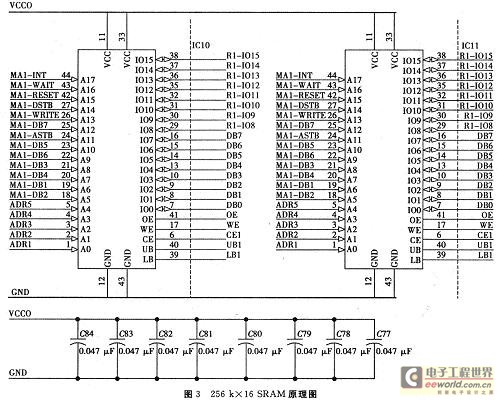

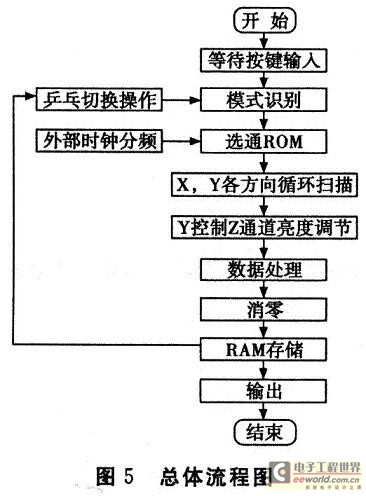

基于VHDL语言的功能与灵活性,非依赖性和可移植性种种优势,本设计在FPGA编程上采用了VHDL语言实现。总体设计思路:采用50 MHz外部时钟控制对FPGA内部进行分频控制,在分频模块的作用下得到设计所需要的时钟信号。通过按键选通在ROM内部选择要显示的模块部分,进行X、 Y方向扫描,得到初步的数据,同时外加Z方向扫描来控制所显图形的亮度。通过将所有的“1”存储在一个ROM中作为缓存,达到消除零点的目的。将ROM中的数据转移到RAM中,通过乒乓交换操作来进行模式转换,最后通过外围电路输入示波器,实现显示。总体流程图:

4 结语

本文是基于FPGA的数字示波器图文显示系统的硬件/软件的设计思路和设计方案。此系统设计完成后,测试表明系统可以将相应的图形文字显示出来,显示的图形和文字与预期的基本一致。该设计满足了系统的需要,更重要的是具有很强的灵活性和可控性,同时使显示更加高速度快捷,具有非常广阔的应用前景。

1 系统总体设计读写

根据设计要求:在示波器上显示2个以上字符或图案,如显示0-9十个数字及英文字符、图象等,结合示波器显示原理,设计电路如图1所示。将要显示的数字或符号进行取模,得到其二进制形式表示。将转换好的数据送入FPGA内部RAM存储。

在设计上我们使用了XILINX的SPARTAN-3芯片,作为控制器,完成总的数控部分、键盘和和显示接口部分的控制。采用八位(或者更高位)D/A转换,对FPGA芯片输出二进制数字量进行数一模转换,在经过高速运算放大器后得到其电压量。分X,Y两路输出给示波器,根据示波器原理,在屏幕上打点显示数字(或者图形)。而Z通道作为另一路独立通道,对显示的数字亮度进行可控显示。

2 系统硬件设计

2.1 总体控制模块

基于本设计,系统控制模块的部分是具有掩膜可编程门阵列的逻辑器件——FPGA。

Spartan系列FPGA是Xilinx公司可编程逻辑产品中的高性价比产品的代表,而Spartan-Ⅲ系列FPGA是为那些需要大容量、低价格电子应用的用户而设计的。本系统使用的是XILINX公司的XC3S200型号芯片,其技术参数如下:

●4 320个逻辑单元;

●系统门密度200 k个;

●CLB阵列24*20,共480个;

●最大用户I/O173,最大差分I/O76;

●分布式RAM容量30 Kbit,Block RAM容量216Kbit;

●嵌入式18x18乘法器支持高性能DSP应用;

●PCI和带有LVDS的高速差分信号。

2.2 存储单元模块

由于FPGA基于CMOS SRAM工艺,不具备掉电保护功能,当无电源供电时,配置的数据丢失,芯片的功能也随之丢失。因此,本设计采用FLASH存储器在线重配置的方法。

2.3 外围电路模块

2.3.1 D/A转换

在D/A选择上,我们用的是美国半导体公司的 DAC0832,它具有8位并行、中速(建立时间1 us)、电流型、价格低廉等特点。它有单缓冲工作方式、双缓冲工作方式两种工作方式。单缓冲工作方式时,一个寄存器工作于直通状态,一个工作于受控锁存器状态。在不要求多相D/A同时输出时,可以采用单缓冲方式,此时只需一次写操作,就开始转换,可以提高D/A的数据吞吐量。双缓冲工作方式时,两个寄存器均工作于受控锁存器状态。当要求多个模拟量同时输出时,可采用双重缓冲方式。

它的技术参数为:建立时间1 us;8位并行;低功率损耗20 mW;支持电压:5 V~15 V。

2.3.2 运算放大

在D/A转换之后,我们得到的是电流信号,而需要输入示波器的为电压信号,因此运用运算放大器来进行转换,同时将运放设计为可调形式,通过调节它便可以调节输出电压的大小,达到控制显示幅值的目的。本设计采用LM741系列运放,其技术指标加下:

3 系统软件设计

基于VHDL语言的功能与灵活性,非依赖性和可移植性种种优势,本设计在FPGA编程上采用了VHDL语言实现。总体设计思路:采用50 MHz外部时钟控制对FPGA内部进行分频控制,在分频模块的作用下得到设计所需要的时钟信号。通过按键选通在ROM内部选择要显示的模块部分,进行X、 Y方向扫描,得到初步的数据,同时外加Z方向扫描来控制所显图形的亮度。通过将所有的“1”存储在一个ROM中作为缓存,达到消除零点的目的。将ROM中的数据转移到RAM中,通过乒乓交换操作来进行模式转换,最后通过外围电路输入示波器,实现显示。总体流程图:

4 结语

本文是基于FPGA的数字示波器图文显示系统的硬件/软件的设计思路和设计方案。此系统设计完成后,测试表明系统可以将相应的图形文字显示出来,显示的图形和文字与预期的基本一致。该设计满足了系统的需要,更重要的是具有很强的灵活性和可控性,同时使显示更加高速度快捷,具有非常广阔的应用前景。

FPGA 电路 单片机 DSP 示波器 LCD 电子 放大器 电压 Xilinx 嵌入式 CMOS 半导体 DAC 电流 运算放大器 VHDL 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)