基于SystemC/TLM方法学的IP开发及FPGA建模

时间:11-08

来源:互联网

点击:

挑战

被测设计(DUT)或被测单元(UUT)的测试对任何设计方法学来说都是最关注的一个方面。在开发的初始阶段,即架构评估阶段,必须需要一个高性能的性能仿真环境。具有行为功能TLM平台能够满足这一需求,并对将要执行的功能进行功能检查。当进入到低级抽象设计阶段时,仿真性能大大降低,这成为有效验证IP的一个问题。

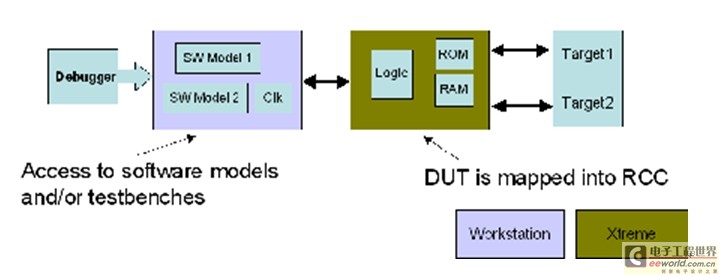

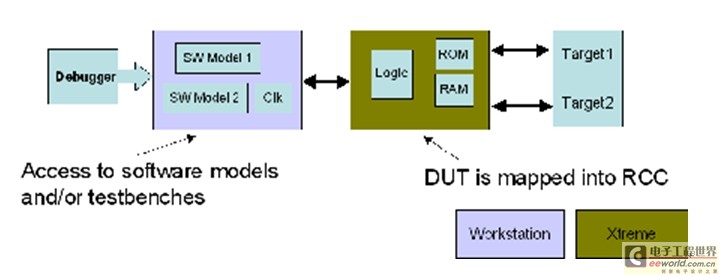

软硬件的系统级仿真与软硬件的协同仿真一块进行。ST有自己的平台,这是一个包含硬件(RTL)的混合平台,软件利用SystemC书写(见图2)。该平台的瓶颈是环境中所引入IP的RTL,而且注意到这将大大地降低性能。正如预期,这是所遇到的约束,而且对是否能够比主仿真运行更快的可能性进行了评估。该方案基于Xtreme服务器硬件仿真,使得运行速度至少要比NCSIM仿真快10倍。

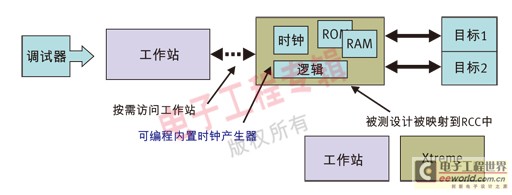

图4:配有软件的Xtreme服务器配置。

图4所示的该技术对第一次仿真特别实用,不需要任何有关环境配置方面的工作量。其概念是在Xtreme的FPGA中运行RTLIP。开始时,引入的时钟为软件时钟,但结果相当可喜,还简化了RTL的系统验证和调试。配置过程中,整个仿真环境是类似的,仅有的改变是用VHDLRTLIP替代SysCIP。试验结果是仿真速度快了10倍。因此,Xtreme服务器平台满足了RTL验证/调试所用平台的需求。最重要的方面是具有与ncsim同等水平的调适能力。还提供了与SystemC环境的无缝集成。

调试功能

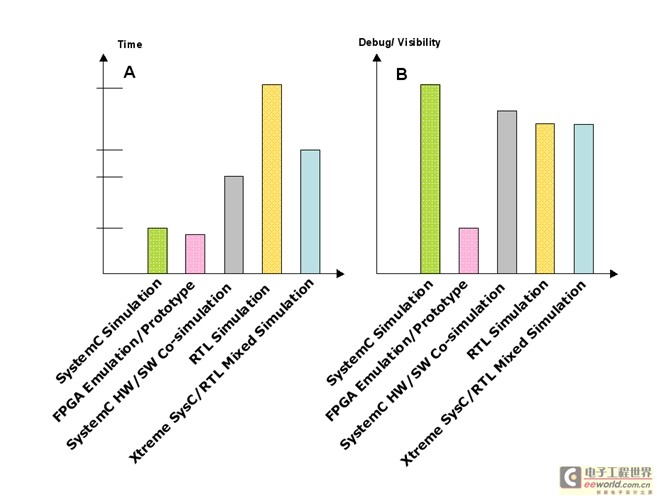

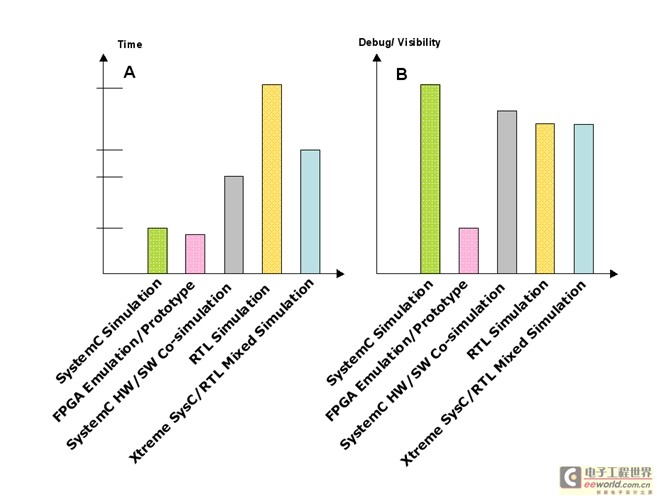

硬件方面的一个更具挑战性的问题是调试。当自检失败时,就需要一个相关的测试范例。为了验证该测试范例,在检查失败原因时必须检查所有的主要信号。所以需要对信号进行存放,验证,从而找出具体的原因。利用基于XTREME服务器的平台可以很容易地执行所有这些功能,无须额外的工作量。通过将实际硬件移入独立的FPGA,可以很容易地改善仿真速度,不过这种方法提供的调试功能较少。因此,基于XTREME服务器的平台不仅改善了仿真速度,还能提供非常好的调试功能。图5给出了分析结果。

图5:A)不同平台上的仿真性能。B)不同平台上的调试复杂性。

FPGA建模

该功能验证方法学中的下一步是对设计进行实时测试。虽然以高级抽象对硬件进行建模能提供高速仿真,但无法对软硬件集成中存在的潜在问题进行放大。同样,利用实际激励在FPGA上运行设计能够实现详尽得多的和更实际的功能覆盖,还能实现与软件的早期集成。

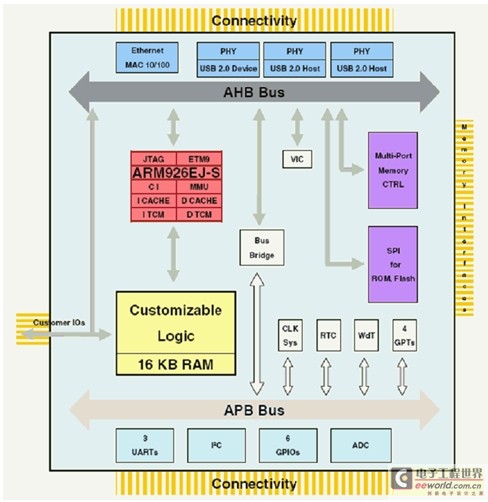

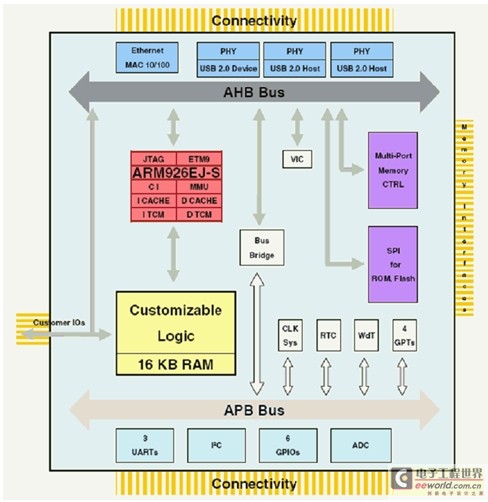

图6:一种普通的SPEAr(SPEArHead)SoC架构。

SPEAr(结构化的处理增强架构)提供一个强大的数字引擎,能够以很少的时间和很少投资提供特殊的用户功能(图6)。该SoC系列具有大量的功能,包括外设,连通性选择,以及允许采用定制IP,从而有助于缩短上市时间。SPEAr采用一个或两个先进的ARM926处理内核,带16k(数据)和16k(指令)高速缓存,主频为333MHz(最坏条件)。它还提供600,000门(与ASIC等效)的嵌入式可配置逻辑,还配有支持DDR/DDR2存储器的存储器接口,以及一个大型的连通性IP(知识产权)系列。这种强大的配置为当今的设计提供了一站式解决方案,同时,通过利用板上能够映射SPEAr内部可配置逻辑块的FPGA,可以将时间和资源需求最小化。

图7:Xtreme服务器箱配置优化。

目标IP(UWB-MAC)被分入两块SPEAr板:MACRTL被分入一块板,而将PHY仿真代码分到另一块中。利用一块仿效MAC-PHY接口的连接板将这两块板连接到一起。利用PC上的软件并通过各自的以太网接口来控制这两块板。板上的FPGA有三个接口,分别为AHB,DMA和中断。

定制逻辑(本例中为MACRTL和PHYEmu)与胶合逻辑(连接三个接口所需的逻辑)一道被成功地移植进FPGA。先前开发的软件在带有SPEAr的ARM平台上得到成功的运行。集成了相同的测试套件,结果显示,功能性与其他架构的结果一致。

被测设计(DUT)或被测单元(UUT)的测试对任何设计方法学来说都是最关注的一个方面。在开发的初始阶段,即架构评估阶段,必须需要一个高性能的性能仿真环境。具有行为功能TLM平台能够满足这一需求,并对将要执行的功能进行功能检查。当进入到低级抽象设计阶段时,仿真性能大大降低,这成为有效验证IP的一个问题。

软硬件的系统级仿真与软硬件的协同仿真一块进行。ST有自己的平台,这是一个包含硬件(RTL)的混合平台,软件利用SystemC书写(见图2)。该平台的瓶颈是环境中所引入IP的RTL,而且注意到这将大大地降低性能。正如预期,这是所遇到的约束,而且对是否能够比主仿真运行更快的可能性进行了评估。该方案基于Xtreme服务器硬件仿真,使得运行速度至少要比NCSIM仿真快10倍。

图4:配有软件的Xtreme服务器配置。

图4所示的该技术对第一次仿真特别实用,不需要任何有关环境配置方面的工作量。其概念是在Xtreme的FPGA中运行RTLIP。开始时,引入的时钟为软件时钟,但结果相当可喜,还简化了RTL的系统验证和调试。配置过程中,整个仿真环境是类似的,仅有的改变是用VHDLRTLIP替代SysCIP。试验结果是仿真速度快了10倍。因此,Xtreme服务器平台满足了RTL验证/调试所用平台的需求。最重要的方面是具有与ncsim同等水平的调适能力。还提供了与SystemC环境的无缝集成。

调试功能

硬件方面的一个更具挑战性的问题是调试。当自检失败时,就需要一个相关的测试范例。为了验证该测试范例,在检查失败原因时必须检查所有的主要信号。所以需要对信号进行存放,验证,从而找出具体的原因。利用基于XTREME服务器的平台可以很容易地执行所有这些功能,无须额外的工作量。通过将实际硬件移入独立的FPGA,可以很容易地改善仿真速度,不过这种方法提供的调试功能较少。因此,基于XTREME服务器的平台不仅改善了仿真速度,还能提供非常好的调试功能。图5给出了分析结果。

图5:A)不同平台上的仿真性能。B)不同平台上的调试复杂性。

FPGA建模

该功能验证方法学中的下一步是对设计进行实时测试。虽然以高级抽象对硬件进行建模能提供高速仿真,但无法对软硬件集成中存在的潜在问题进行放大。同样,利用实际激励在FPGA上运行设计能够实现详尽得多的和更实际的功能覆盖,还能实现与软件的早期集成。

图6:一种普通的SPEAr(SPEArHead)SoC架构。

SPEAr(结构化的处理增强架构)提供一个强大的数字引擎,能够以很少的时间和很少投资提供特殊的用户功能(图6)。该SoC系列具有大量的功能,包括外设,连通性选择,以及允许采用定制IP,从而有助于缩短上市时间。SPEAr采用一个或两个先进的ARM926处理内核,带16k(数据)和16k(指令)高速缓存,主频为333MHz(最坏条件)。它还提供600,000门(与ASIC等效)的嵌入式可配置逻辑,还配有支持DDR/DDR2存储器的存储器接口,以及一个大型的连通性IP(知识产权)系列。这种强大的配置为当今的设计提供了一站式解决方案,同时,通过利用板上能够映射SPEAr内部可配置逻辑块的FPGA,可以将时间和资源需求最小化。

图7:Xtreme服务器箱配置优化。

目标IP(UWB-MAC)被分入两块SPEAr板:MACRTL被分入一块板,而将PHY仿真代码分到另一块中。利用一块仿效MAC-PHY接口的连接板将这两块板连接到一起。利用PC上的软件并通过各自的以太网接口来控制这两块板。板上的FPGA有三个接口,分别为AHB,DMA和中断。

定制逻辑(本例中为MACRTL和PHYEmu)与胶合逻辑(连接三个接口所需的逻辑)一道被成功地移植进FPGA。先前开发的软件在带有SPEAr的ARM平台上得到成功的运行。集成了相同的测试套件,结果显示,功能性与其他架构的结果一致。

半导体 仿真 FPGA ARM 总线 VHDL 射频 SoC 嵌入式 相关文章:

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA 上同步开关噪声的分析(04-05)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)