基于SystemC/TLM方法学的IP开发及FPGA建模

时间:11-08

来源:互联网

点击:

随着系统级芯片技术的出现,设计规模正变得越来越大,因而变得非常复杂,同时上市时间也变得更加苛刻。通常RTL已经不足以担当这一新的角色。上述这些因素正驱使设计师开发新的方法学,用于复杂IP(硬件和软件)以及复杂系统的验证。ST公司建立了一个设计流,它从高级抽象开始,易于将模型写入IP的精密周期或RTL模型中。当转入低级抽象时,建模变得复杂,故IP验证也复杂。我们的方案最适合于这种应用场景,因为它允许人们在各地相似的环境中运行相同的测试平台和测试场景,因而允许在整个开发周期里高效地复用所有的测试范例和环境。

在半导体领域,开发产品的第一步就是以高级抽象开发规范的模型,通常用C/C++来实现。这里,SystemC和C++库提供了很大帮助。它简化了共存的硬件和软件设计的概念化。再加上实现事务级模型间对口连接的TLM传送库,SystemC加速了整个验证过程。另一个重要方面是所有不同抽象架构中经过增强的可移植性。同一测试配置可以无缝地用于不同抽象级的设计。

本文将讨论一种此类的方法学。最终的目标是设计和实现UWBMAC(媒体访问层)IP。出于架构开发的目的,决定用SystemC来实现整个IP。还开发了抽象级具有不同程度变化的不同架构。所付出的努力比较少,最后得到的仿真速度很快,软件的实际编写也可以在设计周期非常早的阶段开始。该IP的RTL结果被移植到了SPEAr系列的FPGA中。除了ARM内核和相应的一系列IP,SPEAr还提供一个可配置逻辑块,这为用户在实现其逻辑功能时提供了无与伦比的灵活性。从而缩短了上市时间,同样也实现了空前的成本节省。

设计开发方法学

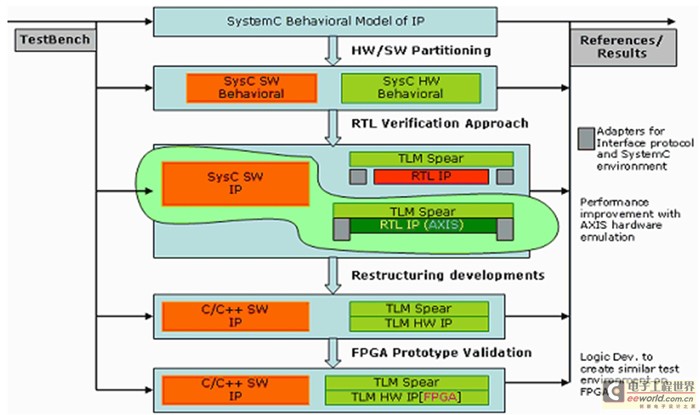

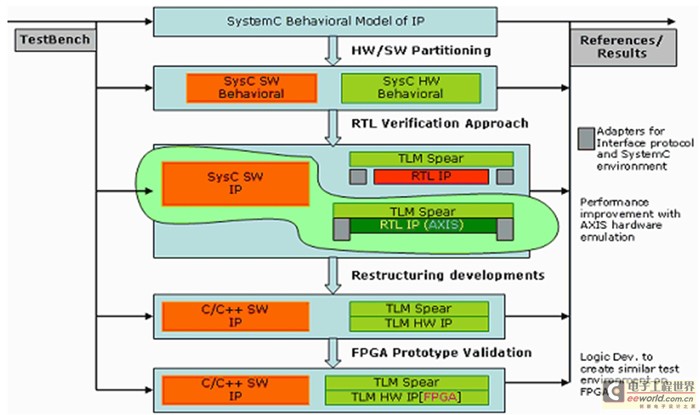

图1所示的该方法学实现了开发的内核中的事务级建模(TLM)。TLM是一种对数字系统进行建模的高级方案,这里将模块之间的具体通信与功能单元或通信架构的具体实现分离开。把总线或FIFO这类通信机制模型化成信道,用SystemC接口类将这些信道提供给模块和部件。这些信道模型的信令接口功能将取代事务请求,这将减少具体的低级信息交换。

图1:IP开发方法学流程。

在事务级建模时,

*更加注重数据转移的功能-即转移的是什么数据,从那里来,到那里去

*不太关注实际的实现-即不太关注数据转移所用的实际协议

该方案使得系统设计师的实验变得更加容易,例如,可以利用不同的总线架构(所有都支持公共的抽象接口),不一定需要对与任意总线进行交互的模型进行重新编码,只要这些模型能够通过公用接口与总线进行交互即可。

在我们的方法中,起始点是对整个功能系统平台进行建模。这是利用SystemC并通过scfifo接口实现的。为了描述通信接口间的数据流,采用了各种架构。这些架构基本上都是协议需要遵守的参数和帧格式信息。围绕IP创建了一个测试环境,环境中开发了测试平台,来传输分别来自两侧的输入,即发送和接收。在这两种范例中,利用这种配置产生了预期的结果或参考。在抽象层,与平台一起使用来进行修改,快速并有效地做试验时将变得很容易,不过精度会降低一些。

随着系统级芯片技术的出现,设计规模正变得越来越大,因而变得非常复杂,同时上市时间也变得更加苛刻。通常RTL已经不足以担当这一新的角色。上述这些因素正驱使设计师开发新的方法学,用于复杂IP(硬件和软件)以及复杂系统的验证。ST公司建立了一个设计流,它从高级抽象开始,易于将模型写入IP的精密周期或RTL模型中。当转入低级抽象时,建模变得复杂,故IP验证也复杂。我们的方案最适合于这种应用场景,因为它允许人们在各地相似的环境中运行相同的测试平台和测试场景,因而允许在整个开发周期里高效地复用所有的测试范例和环境。

在半导体领域,开发产品的第一步就是以高级抽象开发规范的模型,通常用C/C++来实现。这里,SystemC和C++库提供了很大帮助。它简化了共存的硬件和软件设计的概念化。再加上实现事务级模型间对口连接的TLM传送库,SystemC加速了整个验证过程。另一个重要方面是所有不同抽象架构中经过增强的可移植性。同一测试配置可以无缝地用于不同抽象级的设计。

本文将讨论一种此类的方法学。最终的目标是设计和实现UWBMAC(媒体访问层)IP。出于架构开发的目的,决定用SystemC来实现整个IP。还开发了抽象级具有不同程度变化的不同架构。所付出的努力比较少,最后得到的仿真速度很快,软件的实际编写也可以在设计周期非常早的阶段开始。该IP的RTL结果被移植到了SPEAr系列的FPGA中。除了ARM内核和相应的一系列IP,SPEAr还提供一个可配置逻辑块,这为用户在实现其逻辑功能时提供了无与伦比的灵活性。从而缩短了上市时间,同样也实现了空前的成本节省。

在半导体领域,开发产品的第一步就是以高级抽象开发规范的模型,通常用C/C++来实现。这里,SystemC和C++库提供了很大帮助。它简化了共存的硬件和软件设计的概念化。再加上实现事务级模型间对口连接的TLM传送库,SystemC加速了整个验证过程。另一个重要方面是所有不同抽象架构中经过增强的可移植性。同一测试配置可以无缝地用于不同抽象级的设计。

本文将讨论一种此类的方法学。最终的目标是设计和实现UWBMAC(媒体访问层)IP。出于架构开发的目的,决定用SystemC来实现整个IP。还开发了抽象级具有不同程度变化的不同架构。所付出的努力比较少,最后得到的仿真速度很快,软件的实际编写也可以在设计周期非常早的阶段开始。该IP的RTL结果被移植到了SPEAr系列的FPGA中。除了ARM内核和相应的一系列IP,SPEAr还提供一个可配置逻辑块,这为用户在实现其逻辑功能时提供了无与伦比的灵活性。从而缩短了上市时间,同样也实现了空前的成本节省。

设计开发方法学

图1所示的该方法学实现了开发的内核中的事务级建模(TLM)。TLM是一种对数字系统进行建模的高级方案,这里将模块之间的具体通信与功能单元或通信架构的具体实现分离开。把总线或FIFO这类通信机制模型化成信道,用SystemC接口类将这些信道提供给模块和部件。这些信道模型的信令接口功能将取代事务请求,这将减少具体的低级信息交换。

图1:IP开发方法学流程。

在事务级建模时,

*更加注重数据转移的功能-即转移的是什么数据,从那里来,到那里去

*不太关注实际的实现-即不太关注数据转移所用的实际协议

该方案使得系统设计师的实验变得更加容易,例如,可以利用不同的总线架构(所有都支持公共的抽象接口),不一定需要对与任意总线进行交互的模型进行重新编码,只要这些模型能够通过公用接口与总线进行交互即可。

在我们的方法中,起始点是对整个功能系统平台进行建模。这是利用SystemC并通过scfifo接口实现的。为了描述通信接口间的数据流,采用了各种架构。这些架构基本上都是协议需要遵守的参数和帧格式信息。围绕IP创建了一个测试环境,环境中开发了测试平台,来传输分别来自两侧的输入,即发送和接收。在这两种范例中,利用这种配置产生了预期的结果或参考。在抽象层,与平台一起使用来进行修改,快速并有效地做试验时将变得很容易,不过精度会降低一些。

随着系统级芯片技术的出现,设计规模正变得越来越大,因而变得非常复杂,同时上市时间也变得更加苛刻。通常RTL已经不足以担当这一新的角色。上述这些因素正驱使设计师开发新的方法学,用于复杂IP(硬件和软件)以及复杂系统的验证。ST公司建立了一个设计流,它从高级抽象开始,易于将模型写入IP的精密周期或RTL模型中。当转入低级抽象时,建模变得复杂,故IP验证也复杂。我们的方案最适合于这种应用场景,因为它允许人们在各地相似的环境中运行相同的测试平台和测试场景,因而允许在整个开发周期里高效地复用所有的测试范例和环境。

在半导体领域,开发产品的第一步就是以高级抽象开发规范的模型,通常用C/C++来实现。这里,SystemC和C++库提供了很大帮助。它简化了共存的硬件和软件设计的概念化。再加上实现事务级模型间对口连接的TLM传送库,SystemC加速了整个验证过程。另一个重要方面是所有不同抽象架构中经过增强的可移植性。同一测试配置可以无缝地用于不同抽象级的设计。

本文将讨论一种此类的方法学。最终的目标是设计和实现UWBMAC(媒体访问层)IP。出于架构开发的目的,决定用SystemC来实现整个IP。还开发了抽象级具有不同程度变化的不同架构。所付出的努力比较少,最后得到的仿真速度很快,软件的实际编写也可以在设计周期非常早的阶段开始。该IP的RTL结果被移植到了SPEAr系列的FPGA中。除了ARM内核和相应的一系列IP,SPEAr还提供一个可配置逻辑块,这为用户在实现其逻辑功能时提供了无与伦比的灵活性。从而缩短了上市时间,同样也实现了空前的成本节省。

半导体 仿真 FPGA ARM 总线 VHDL 射频 SoC 嵌入式 相关文章:

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)

- FPGA 上同步开关噪声的分析(04-05)

- 初学者如何学习FPGA(08-06)

- 为何、如何学习FPGA(05-23)

- 学习FPGA绝佳网站推荐!!!(05-23)