利用低成本FPGA设计下一代游戏控制台

时间:11-08

来源:互联网

点击:

游戏控制台设计者必须在实现系统的多功能、可靠性和低成本之间寻找平衡。市场压力经常迫使最初的控制台价格低于可盈利的水平。不过,要在商业上获得成功,游戏控制台就必须能够提供多种功能,如高清晰度图像、网络连接、运动传感控制器以及基于IP的视频内容,并且所有这些都要在用户能承受的价格内。

为保持低成本特性,通常采用基于平台的方法来设计游戏控制台。目标是尽可能地使每个控制台相似,同时还能满足特殊区域的要求。单个平台设计通常是不现实的,经济效益上也不可行,但FPGA所提供的硬件灵活性使得游戏系统能够很容易地针对不同区域、模型、组件和升级版进行重新设计。

一个典型的游戏控制台包括CPU、图形处理器、存储器件、通信单元、I/O和用户接口。游戏控制台的核心通常是几个大规模ASIC或ASSP。例如,iSuppli的报告指出,Sony PS3就包含一个7个核定制基于cell的CPU(ASIC)、一个NVIDIA图形芯片组(ASSP)、XDR存储器和一个flexIO处理器接口。

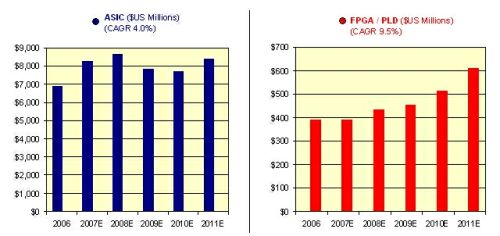

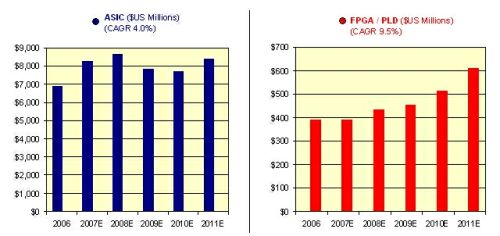

由于FPGA在许多应用中取代了ASIC,或许现在是时候将它用于下一代游戏控制台设计中了。FPGA和PLD相对较低的成本正在推动其在消费电子产品中的使用,尤其是在LCD和等离子电视中。根据Gartner Group的报告(如图1所示),在未来的4年中,用于消费电子产品的PLD和FPGA器件的全球市场年均复合增长率(CAGR)预计将达9.5%,超过了年均复合增长率为4.0%的ASIC器件。

图1:用于消费电子设备的ASIC和FPGA的年收益变化。

基于平台的游戏控制台设计考虑因素

FPGA可以帮助系统设计者尽可能地节约成本并提供最大的灵活性,这是由基于平台方法通过提供以下设计方针来实现的。

需求和模型可随着区域而变化:针对多个标准和格式提供可编程支持能加快产品上市时间;低成本和可靠的设计:集成全部的系统I/O接口、控制逻辑和调试功能,以支持连接至HDD和内部存储器的ASIC/ASSP芯片组的桥接功能,定制的用户接口逻辑可降低在新产品中的风险;在最终测试期间和现场的安全编程能够实现对多种标准的支持、协处理算法的增量升级以及易于对新功能进行测试。

带有嵌入式DSP解决方案的FPGA

在选择面向平台的可编程器件时,通常需考虑三种电路要求:面向协处理功能的嵌入式DSP的功能和性能、查找表(LUT)以及RAM块(EBR),这种协处理功能利用并行方法,针对具体应用以最优成本对功能和性能进行裁剪。低电压差分信号(LVDS)和串行解串器(SERDES)可支持高速芯片至芯片接口,如HyperTransport、PCI Express或串行RapidIO。能够安全地保护知识产权。

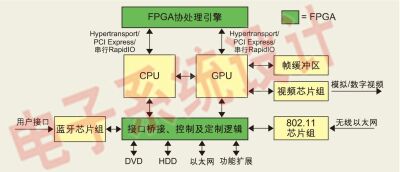

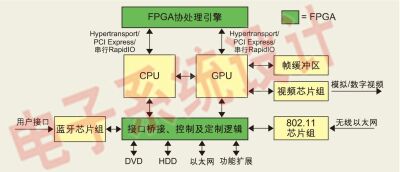

图2显示了一个满足这些要求的FPGA解决方案。FPGA被连接到主CPU、图像处理芯片、用户接口和诸如无线以太网的其它关键ASSP。FPGA模块执行协处理功能和硬件加速,并具有实现未来功能所必需的定制逻辑,这些功能是针对用户接口或控制台的其它部分。

图2:可重构FPGA能支持多个I/O标准、高速接口以及针对硬件加速的协处理算法。

DSP协处理和硬件加速

尽管低成本FPGA通常工作在小于300MHz的系统时钟频率下,但通过并行地执行串行功能仍然可实现很高的DSP吞吐量(63,000MMAC)。例如,某个应用要求具有100MS/s采样率的32抽头FIR滤波器,那么需要带有4个乘法器的通用DSP处理器以800MHz计算乘累加。具有32个乘法器的FPGA能够在100MHz实现相同的滤波器。

与乘法器一样,能够灵活地利用FPGA的并行特性有益于存储器访问。片上分布式存储器可用来构建小容量高性能临时存储器,而片上嵌入式存储块可用来构建大容量高性能存储器。DDR DRAM等片外存储器则可以提供大容量、高性能存储器。

高速的芯片至芯片互连

FPGA通过高速的芯片至芯片互连技术与GPU和CPU连接,这些技术包括HyperTransport、PCI Express或串行RapidIO。串行RapidIO和PCI Express是串行而非并行技术,即串行地发送数据,并通过LVDS以数据包的形式恢复数据,而不是一次恢复一位。从并行到串行接口的转换系统可用较少的线路达到同样的高速数据速率。

源同步和时钟数据恢复接口

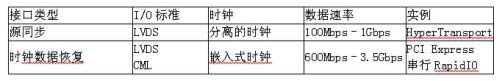

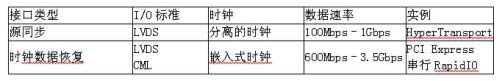

HyperTransport是一个源同步接口,而PCI Express和串行RapidIO采用时钟数据恢复(CDR)技术,如下表所示。对于源同步接口而言,传送方提供数据和差分时钟,这样就能较容易地在高达700Mbps的数据速率捕获数据。

源同步和时钟数据恢复接口。

当数据速率超过700Mbps时,数据通道之间的偏移成为数据有效窗的重要部分,特别是对宽数据通道而言。有些FPGA具有自动对齐功能,能够针对源同步接口管理数据偏移,从而有助于它们达到超过800Mbps的LVDS数据速率(有些情况下高达2Gbps)。

对于CDR接口而言,并没有提供额外的差分时钟。取而代之的是时钟包含在串行数据包中,必须从数据中恢复出来。因此,对于CDR来说时钟偏移不是一个问题,这与源同步不同。利用SERDES高速串行地发送数据包,CDR接收器将对数据本身锁定相位以取得时钟。

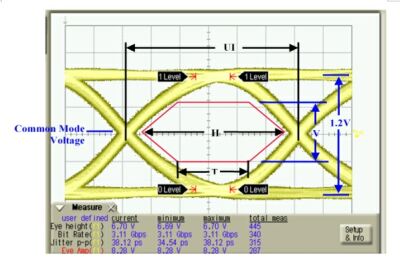

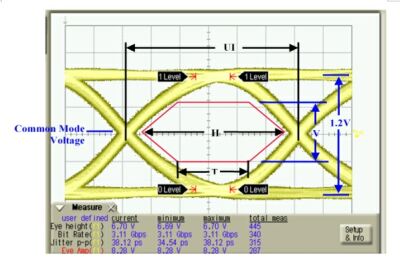

对于CDR而言,在高速情况下,SERDES抖动是主要问题。抖动是指期待数据传输的位置发生了变化,使得难以准确地接收到数据包。如图3所示的眼图,抖动使得围绕眼睛的黄色带的宽度发生变化,图中用红色表示。

图3:CDR眼图。

有些抖动是随机的,但大部分抖动是确定性的,是由于其它信号以及靠近数据信号的半导体元件的开关操作引起,或者是由数据模式的特性、传输的不平衡上升及下降时间所引起。

为保持低成本特性,通常采用基于平台的方法来设计游戏控制台。目标是尽可能地使每个控制台相似,同时还能满足特殊区域的要求。单个平台设计通常是不现实的,经济效益上也不可行,但FPGA所提供的硬件灵活性使得游戏系统能够很容易地针对不同区域、模型、组件和升级版进行重新设计。

一个典型的游戏控制台包括CPU、图形处理器、存储器件、通信单元、I/O和用户接口。游戏控制台的核心通常是几个大规模ASIC或ASSP。例如,iSuppli的报告指出,Sony PS3就包含一个7个核定制基于cell的CPU(ASIC)、一个NVIDIA图形芯片组(ASSP)、XDR存储器和一个flexIO处理器接口。

由于FPGA在许多应用中取代了ASIC,或许现在是时候将它用于下一代游戏控制台设计中了。FPGA和PLD相对较低的成本正在推动其在消费电子产品中的使用,尤其是在LCD和等离子电视中。根据Gartner Group的报告(如图1所示),在未来的4年中,用于消费电子产品的PLD和FPGA器件的全球市场年均复合增长率(CAGR)预计将达9.5%,超过了年均复合增长率为4.0%的ASIC器件。

图1:用于消费电子设备的ASIC和FPGA的年收益变化。

基于平台的游戏控制台设计考虑因素

FPGA可以帮助系统设计者尽可能地节约成本并提供最大的灵活性,这是由基于平台方法通过提供以下设计方针来实现的。

需求和模型可随着区域而变化:针对多个标准和格式提供可编程支持能加快产品上市时间;低成本和可靠的设计:集成全部的系统I/O接口、控制逻辑和调试功能,以支持连接至HDD和内部存储器的ASIC/ASSP芯片组的桥接功能,定制的用户接口逻辑可降低在新产品中的风险;在最终测试期间和现场的安全编程能够实现对多种标准的支持、协处理算法的增量升级以及易于对新功能进行测试。

带有嵌入式DSP解决方案的FPGA

在选择面向平台的可编程器件时,通常需考虑三种电路要求:面向协处理功能的嵌入式DSP的功能和性能、查找表(LUT)以及RAM块(EBR),这种协处理功能利用并行方法,针对具体应用以最优成本对功能和性能进行裁剪。低电压差分信号(LVDS)和串行解串器(SERDES)可支持高速芯片至芯片接口,如HyperTransport、PCI Express或串行RapidIO。能够安全地保护知识产权。

图2显示了一个满足这些要求的FPGA解决方案。FPGA被连接到主CPU、图像处理芯片、用户接口和诸如无线以太网的其它关键ASSP。FPGA模块执行协处理功能和硬件加速,并具有实现未来功能所必需的定制逻辑,这些功能是针对用户接口或控制台的其它部分。

图2:可重构FPGA能支持多个I/O标准、高速接口以及针对硬件加速的协处理算法。

DSP协处理和硬件加速

尽管低成本FPGA通常工作在小于300MHz的系统时钟频率下,但通过并行地执行串行功能仍然可实现很高的DSP吞吐量(63,000MMAC)。例如,某个应用要求具有100MS/s采样率的32抽头FIR滤波器,那么需要带有4个乘法器的通用DSP处理器以800MHz计算乘累加。具有32个乘法器的FPGA能够在100MHz实现相同的滤波器。

与乘法器一样,能够灵活地利用FPGA的并行特性有益于存储器访问。片上分布式存储器可用来构建小容量高性能临时存储器,而片上嵌入式存储块可用来构建大容量高性能存储器。DDR DRAM等片外存储器则可以提供大容量、高性能存储器。

高速的芯片至芯片互连

FPGA通过高速的芯片至芯片互连技术与GPU和CPU连接,这些技术包括HyperTransport、PCI Express或串行RapidIO。串行RapidIO和PCI Express是串行而非并行技术,即串行地发送数据,并通过LVDS以数据包的形式恢复数据,而不是一次恢复一位。从并行到串行接口的转换系统可用较少的线路达到同样的高速数据速率。

源同步和时钟数据恢复接口

HyperTransport是一个源同步接口,而PCI Express和串行RapidIO采用时钟数据恢复(CDR)技术,如下表所示。对于源同步接口而言,传送方提供数据和差分时钟,这样就能较容易地在高达700Mbps的数据速率捕获数据。

源同步和时钟数据恢复接口。

当数据速率超过700Mbps时,数据通道之间的偏移成为数据有效窗的重要部分,特别是对宽数据通道而言。有些FPGA具有自动对齐功能,能够针对源同步接口管理数据偏移,从而有助于它们达到超过800Mbps的LVDS数据速率(有些情况下高达2Gbps)。

对于CDR接口而言,并没有提供额外的差分时钟。取而代之的是时钟包含在串行数据包中,必须从数据中恢复出来。因此,对于CDR来说时钟偏移不是一个问题,这与源同步不同。利用SERDES高速串行地发送数据包,CDR接收器将对数据本身锁定相位以取得时钟。

对于CDR而言,在高速情况下,SERDES抖动是主要问题。抖动是指期待数据传输的位置发生了变化,使得难以准确地接收到数据包。如图3所示的眼图,抖动使得围绕眼睛的黄色带的宽度发生变化,图中用红色表示。

图3:CDR眼图。

有些抖动是随机的,但大部分抖动是确定性的,是由于其它信号以及靠近数据信号的半导体元件的开关操作引起,或者是由数据模式的特性、传输的不平衡上升及下降时间所引起。

FPGA 电子 LCD 嵌入式 DSP 电路 电压 滤波器 半导体 连接器 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)