采用FPGA实现视频监视

时间:11-08

来源:互联网

点击:

低成本AUP移植途径

随着标准的稳定和产量的提高,应该具备低成本移植途径。这通常意味着市场关注的ASSP或者标准单元定制ASIC器件。然而,定制芯片成本不断攀升,只有在大批量消费类应用中采用这些方案才具有一定的经济性。大部分视频和图像芯片公司的主要业务包括视频摄录机、机顶盒、数字照相机、蜂窝电话等便携式产品,以及LCD TV和监视器等。因此,如果设计的产品批量不大,那么最好考虑FPGA,它不像ASSP那样只针对特定的功能,由于产品很有可能过时,即使当时最好的解决方案也可能是风险很高的选择。

Altera视频和图像处理解决方案

考虑到上面阐述的问题,FPGA非常适合应用于视频和图像处理领域。Altera FPGA具有以下特点,是视频和图像处理体系结构最好的选择:

高性能:HD处理可以在一片Altera FPGA中实现。

灵活性:Altera FPGA能够迅速更新体系结构,满足不断发展的需求,同时其可伸缩性使得FPGA能够应用于低成本高性能系统中。

低开发成本:Altera的视频开发套件起价只有1,095美金,包括使用Altera FPGA开发视频系统所需要的软件工具。

不会过时:Altera FPGA拥有广泛的客户基础,多年以来,他们不断采购新产品。Altera还一直在发售199x[SLA1]引入的FPGA。同样的,FPGA设计可以很容易的从一个工艺节点移植到新节点。

低成本结构化ASIC移植途径:Altera结构化ASIC 1百万ASIC逻辑门100ku起价为15美金。

Altera的视频和图像处理解决方案包括经过优化的DSP设计流程、Altera视频和图像处理套件,接口和第三方视频压缩IP以及视频参考设计等。

FPGA/结构化ASIC实现类似ASSP的功能

随着解决方案的增多,Altera及其合作伙伴以FPGA或者结构化ASIC的形式提供ASSP功能。例如ATEME的H.26?普通质量标准清晰度编码器产品。采用这一产品后,客户可以象ASSP那样使用FPGA,其优于传统ASSP之处在于FPGA方案发展迅速,没有过时的风险。

DSP设计流程

对于定制开发,Altera提供最佳的DSP设计流程,可以采用不同的方法进行设计,包括VHDL/Verilog、基于模型的设计和基于C语言的设计。Altera的视频和图像处理套件能够应用于这些设计流程中。Altera和The MathWorks合作开发了全面的DSP开发流程,使设计人员能够充分利用Altera? FPGA的价格/性能优势以及Simulink、The MathWorks基于模型的设计工具等。Altera的DSP Builder是一种DSP开发工具,它结合了Simulink和Altera业界领先的Quartus? II开发软件。DSP Builder提供无缝设计流程,设计人员在MATLAB软件中进行算法开发,在Simulink软件中进行系统级设计,然后将设计导入至硬件描述语言(HDL)文件,供Quartus II软件使用。DSP Builder工具和SOPC Builder工具紧密集成,使用户能够结合Simulink设计和Altera嵌入式处理器以及知识产权内核来构建系统。对于那些在可编程逻辑设计软件上经验还不够的设计人员而言,这种开发流程简单易用,非常直观。视频和图像处理套件

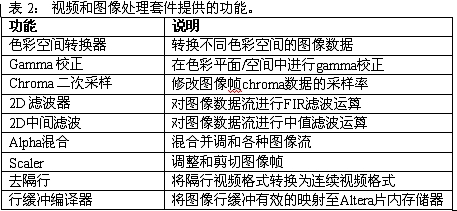

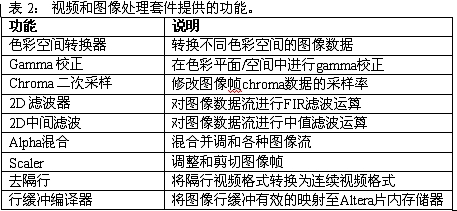

视频和图像处理套件含有9个功能模块,其参数在某些情况下可以动态调整。表2总结了这些功能。

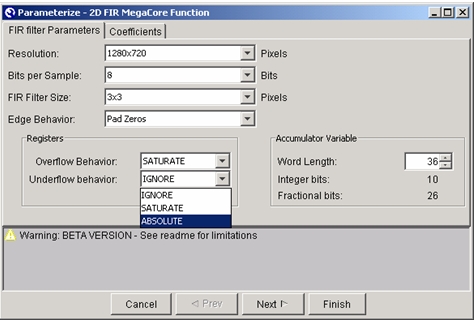

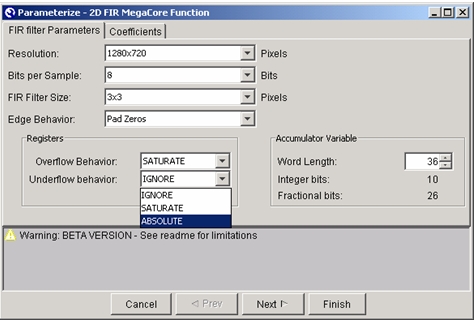

2D滤波器GUI示于下图中,这是一个采用视频和图像处理套件提供的内核来实现用户配置的实例。

分辨率、采样比特、FIR滤波器、边沿、溢出以及累加器长度等都是2D滤波器内核支持的静态参数。

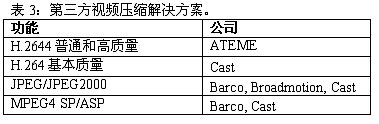

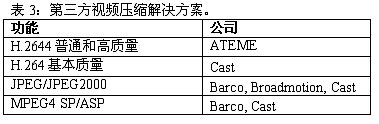

视频压缩许多第三方针对Altera FPGA和结构化ASIC提供了视频压缩方案。表3列出了部分常见视频压缩标准和相关的第三方。

IP承载视频

Altera为IP承载视频提供参考设计。该设计将视频传送流(TS)数据通过IP网络传输,在100Mbps或者1Gbps以太网上桥接多个压缩视频流和IP数据包。参考设计接收TS数据,对其进行包封,在以太网上传输,也可以接收来自以太网的帧,生成TS数据。

以太网TS数据包封使用IP和用户数据报协议(UDP)。也可以采用实时传送协议(RTP)。专用硬件处理包封,实现参考设计的最大吞吐量和最小延时。能够在以太网线路速率上处理、传送和接收帧,支持千兆以太网链路900Mbps以上的集中TS带宽。对于复用TS接口,参考设计将每个接口分别映射到专用UDP/IP插件(结合IP地址和UDP端口)。也可以采用其他的包封参数来分别配置每个TS。参考设计支持IP多播,含有一个Nios II处理器。Nios II处理器中运行的软件对参考设计进行设置,处理所有的以太网管理业务。

结论

Altera的FPGA与功能丰富的Altera视频图像库、Altera IP承载视频参考设计,以及合作伙伴的压缩方案相结合,为视频系统设计人员设计高性能、低成本系统提供了关键构建模块,帮助他们达到时间和市场需求。

随着标准的稳定和产量的提高,应该具备低成本移植途径。这通常意味着市场关注的ASSP或者标准单元定制ASIC器件。然而,定制芯片成本不断攀升,只有在大批量消费类应用中采用这些方案才具有一定的经济性。大部分视频和图像芯片公司的主要业务包括视频摄录机、机顶盒、数字照相机、蜂窝电话等便携式产品,以及LCD TV和监视器等。因此,如果设计的产品批量不大,那么最好考虑FPGA,它不像ASSP那样只针对特定的功能,由于产品很有可能过时,即使当时最好的解决方案也可能是风险很高的选择。

Altera视频和图像处理解决方案

考虑到上面阐述的问题,FPGA非常适合应用于视频和图像处理领域。Altera FPGA具有以下特点,是视频和图像处理体系结构最好的选择:

高性能:HD处理可以在一片Altera FPGA中实现。

灵活性:Altera FPGA能够迅速更新体系结构,满足不断发展的需求,同时其可伸缩性使得FPGA能够应用于低成本高性能系统中。

低开发成本:Altera的视频开发套件起价只有1,095美金,包括使用Altera FPGA开发视频系统所需要的软件工具。

不会过时:Altera FPGA拥有广泛的客户基础,多年以来,他们不断采购新产品。Altera还一直在发售199x[SLA1]引入的FPGA。同样的,FPGA设计可以很容易的从一个工艺节点移植到新节点。

低成本结构化ASIC移植途径:Altera结构化ASIC 1百万ASIC逻辑门100ku起价为15美金。

Altera的视频和图像处理解决方案包括经过优化的DSP设计流程、Altera视频和图像处理套件,接口和第三方视频压缩IP以及视频参考设计等。

FPGA/结构化ASIC实现类似ASSP的功能

随着解决方案的增多,Altera及其合作伙伴以FPGA或者结构化ASIC的形式提供ASSP功能。例如ATEME的H.26?普通质量标准清晰度编码器产品。采用这一产品后,客户可以象ASSP那样使用FPGA,其优于传统ASSP之处在于FPGA方案发展迅速,没有过时的风险。

DSP设计流程

对于定制开发,Altera提供最佳的DSP设计流程,可以采用不同的方法进行设计,包括VHDL/Verilog、基于模型的设计和基于C语言的设计。Altera的视频和图像处理套件能够应用于这些设计流程中。Altera和The MathWorks合作开发了全面的DSP开发流程,使设计人员能够充分利用Altera? FPGA的价格/性能优势以及Simulink、The MathWorks基于模型的设计工具等。Altera的DSP Builder是一种DSP开发工具,它结合了Simulink和Altera业界领先的Quartus? II开发软件。DSP Builder提供无缝设计流程,设计人员在MATLAB软件中进行算法开发,在Simulink软件中进行系统级设计,然后将设计导入至硬件描述语言(HDL)文件,供Quartus II软件使用。DSP Builder工具和SOPC Builder工具紧密集成,使用户能够结合Simulink设计和Altera嵌入式处理器以及知识产权内核来构建系统。对于那些在可编程逻辑设计软件上经验还不够的设计人员而言,这种开发流程简单易用,非常直观。视频和图像处理套件

视频和图像处理套件含有9个功能模块,其参数在某些情况下可以动态调整。表2总结了这些功能。

2D滤波器GUI示于下图中,这是一个采用视频和图像处理套件提供的内核来实现用户配置的实例。

分辨率、采样比特、FIR滤波器、边沿、溢出以及累加器长度等都是2D滤波器内核支持的静态参数。

视频压缩许多第三方针对Altera FPGA和结构化ASIC提供了视频压缩方案。表3列出了部分常见视频压缩标准和相关的第三方。

IP承载视频

Altera为IP承载视频提供参考设计。该设计将视频传送流(TS)数据通过IP网络传输,在100Mbps或者1Gbps以太网上桥接多个压缩视频流和IP数据包。参考设计接收TS数据,对其进行包封,在以太网上传输,也可以接收来自以太网的帧,生成TS数据。

以太网TS数据包封使用IP和用户数据报协议(UDP)。也可以采用实时传送协议(RTP)。专用硬件处理包封,实现参考设计的最大吞吐量和最小延时。能够在以太网线路速率上处理、传送和接收帧,支持千兆以太网链路900Mbps以上的集中TS带宽。对于复用TS接口,参考设计将每个接口分别映射到专用UDP/IP插件(结合IP地址和UDP端口)。也可以采用其他的包封参数来分别配置每个TS。参考设计支持IP多播,含有一个Nios II处理器。Nios II处理器中运行的软件对参考设计进行设置,处理所有的以太网管理业务。

结论

Altera的FPGA与功能丰富的Altera视频图像库、Altera IP承载视频参考设计,以及合作伙伴的压缩方案相结合,为视频系统设计人员设计高性能、低成本系统提供了关键构建模块,帮助他们达到时间和市场需求。

嵌入式 DSP Altera FPGA 机顶盒 LCD 编码器 VHDL Verilog C语言 Quartus 滤波器 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)