采用FPGA实现视频监视

时间:11-08

来源:互联网

点击:

目前,视频监视行业使用模拟CCTV摄像机和接口作为监视系统的基础设施。这些系统组成不容易扩展,视频分辨率低,信号处理功能较弱,甚至不进行信号处理。然而,下一代视频监视系统将逐渐采用新的数字LAN摄像机、复杂的图像处理和IP承载视频等技术来替代这些系统组成,它们不仅是简单的监视摄像机系统,同时还是视频通信系统。

新的监视系统基于互联网协议(IP),具有更大的可伸缩性和灵活性以及计算机安全性。可以采用各种编码和解码标准来传送视频流(MPEG4 CODEC是目前使用的标准)。除了CODEC功能以外,图像预处理和后处理提高了实时图像质量,降低了延时。设计人员使用带有嵌入式DSP模块、存储器和接口的可编程逻辑,能够满足新系统的要求。

数字视频摄录机体系结构

在数字视频摄录机(DVR)系统中,多台模拟CCTV摄像机与中央视频交换机相连,实现存储、缩放、图像处理和显示等功能。由于压缩比较复杂,成本高,视频分辨率和质量比较低。移动探测等特殊处理功能占用了中央交换机大量的存储资源。因此,这种体系结构灵活性不够,扩展性不好,视频监视的质量和监视范围有限。

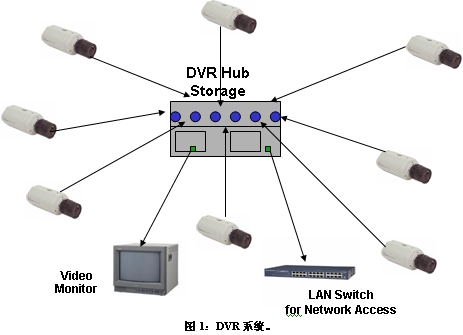

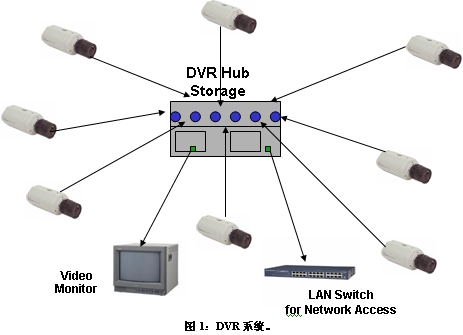

一个典型的DVR系统(图1所示)采用了内部或者外部视频矩阵来连接摄像机和监视器。这类系统需要多路输出和输入复用,适合采用可编程逻辑提高系统的灵活性和扩展性。

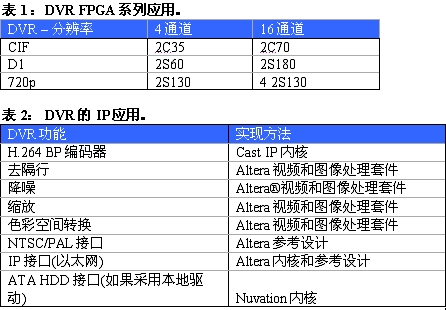

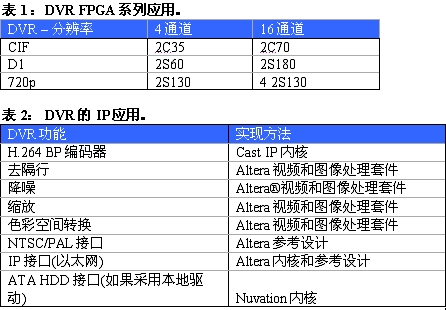

表1列出了Altera FPGA系列在DVR功能(表2)中的应用情况。

网络视频摄录机体系结构

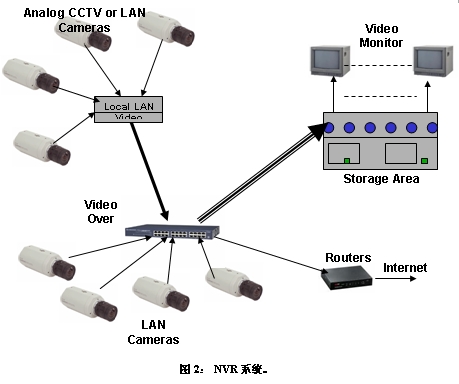

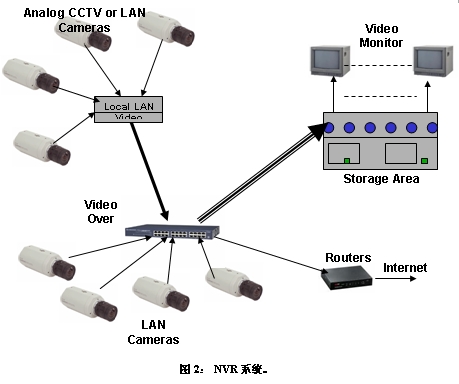

网络视频摄录机(NVR)系统灵活性更大,可以同时使用传统的模拟CCTV摄像机和新的数字LAN摄像机。LAN摄像机向中央文件服务器发送JPEG(低分辨率)或者MPEG4(高分辨率)压缩的视频流,进行存储。存储容量取决于视频分辨率(象素)、压缩类型、帧速率以及连续/间隔记录等。本地视频服务器将模拟视频转换为数字格式,在LAN上传送。所有这些网络视频数据都被传送到存储区域网络(SAN),进行记录。图2是NVR设置的例子。

视频压缩和图像处理

视频数据压缩有很多不同的标准。所采用的压缩标准对硬件系统要求有影响,包括存储器、数据速率和存储容量等。最流行的压缩技术包括JPEG、H.263、Motion JPEG, MPEG和Wavelet。而H.26?的压缩效率较高,下一代监视系统很可能采用这种标准。在带宽受限的网络中传送高质量视频信号时,效率扮演了重要角色。例如,6?0 x 480象素30fps的彩色传输需要26Mbytes/s的数据速率。必须降低(压缩)速率,使其能够在双绞线或者铜缆中传输。

有两种类型的视频压缩速率:固定比特率(CBR)和可变比特率(VBR)。对于带宽有限的实时通信信道,CBR限制了数据速率,当图像中出现高质量的移动细节时,会降低图像质量,导致显示图像中出现图像块。VBR根据是否出现图像移动来调整速率,这对于视频监视系统存储非常有用。支持VBR的H.26?压缩在安全视频存储方面效率最高。

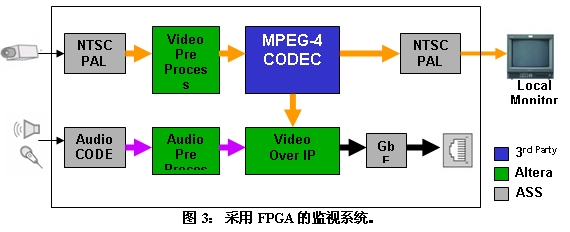

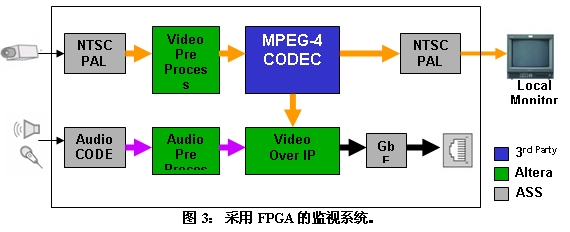

此外,在压缩方法上,其他视频图像处理技术提高了视频流预处理和后处理的视频质量。由于分辨率的提高,以及压缩技术的进展,对高性能的需求在不断增长,同时还要保持体系结构的灵活性,方便进行快速更新。随着技术的成熟和产量的提高,降低成本将成为人们关注的焦点。图3是使用FPGA和ASSP的典型视频监视系统设置。

系统体系结构选择包括标准单元ASIC、ASSP,以及数字信号处理(DSP)或者介质处理器和FPGA等可编程解决方案。这些方案各具优缺点,最终选择取决于最终设备要求和方案的可行性。考虑到上面介绍的发展趋势,理想的监视体系结构应具有以下特征:高性能、灵活性、易于更新、低开发成本,随着应用的成熟和产量的提高,能够通过移植降低成本。

高性能

性能不仅体现在压缩上,还体现在预处理和后处理功能上。事实上,在很多情况下,这些功能要比压缩算法本身对性能的影响更大。这类功能的例子包括缩放、去隔行、滤波和色彩空间转换等。

对于视频监视,对高性能的要求排除了单处理器体系结构,因为一个器件无法满足性能要求。目前最好的1GHz DSP无法进行H.26? HD解码,而H.26? HD编码要比解码复杂10倍。FPGA是唯一能够解决这一矛盾的可编程方案。在某些情况下,最好的解决方案是结合FPGA和外部DSP处理器。

灵活性支持了产品快速面市,方便了产品更新

当技术快速发展时,体系结构必须足够灵活,能够方便的进行更新。在这些应用中无法使用标准单元ASIC和ASSP。ASSP一般针对大批量消费类市场,产品容易过时,对大部分应用而言,选择ASSP的风险较大。

低开发成本

考虑到掩模、晶片、软件、设计验证和布板等成本,开发一个典型90nm标准单元ASIC的成本会高达3千万美金。只有产量非常大的消费类市场能够解决如此昂贵的开发成本。

新的监视系统基于互联网协议(IP),具有更大的可伸缩性和灵活性以及计算机安全性。可以采用各种编码和解码标准来传送视频流(MPEG4 CODEC是目前使用的标准)。除了CODEC功能以外,图像预处理和后处理提高了实时图像质量,降低了延时。设计人员使用带有嵌入式DSP模块、存储器和接口的可编程逻辑,能够满足新系统的要求。

数字视频摄录机体系结构

在数字视频摄录机(DVR)系统中,多台模拟CCTV摄像机与中央视频交换机相连,实现存储、缩放、图像处理和显示等功能。由于压缩比较复杂,成本高,视频分辨率和质量比较低。移动探测等特殊处理功能占用了中央交换机大量的存储资源。因此,这种体系结构灵活性不够,扩展性不好,视频监视的质量和监视范围有限。

一个典型的DVR系统(图1所示)采用了内部或者外部视频矩阵来连接摄像机和监视器。这类系统需要多路输出和输入复用,适合采用可编程逻辑提高系统的灵活性和扩展性。

表1列出了Altera FPGA系列在DVR功能(表2)中的应用情况。

网络视频摄录机体系结构

网络视频摄录机(NVR)系统灵活性更大,可以同时使用传统的模拟CCTV摄像机和新的数字LAN摄像机。LAN摄像机向中央文件服务器发送JPEG(低分辨率)或者MPEG4(高分辨率)压缩的视频流,进行存储。存储容量取决于视频分辨率(象素)、压缩类型、帧速率以及连续/间隔记录等。本地视频服务器将模拟视频转换为数字格式,在LAN上传送。所有这些网络视频数据都被传送到存储区域网络(SAN),进行记录。图2是NVR设置的例子。

视频压缩和图像处理

视频数据压缩有很多不同的标准。所采用的压缩标准对硬件系统要求有影响,包括存储器、数据速率和存储容量等。最流行的压缩技术包括JPEG、H.263、Motion JPEG, MPEG和Wavelet。而H.26?的压缩效率较高,下一代监视系统很可能采用这种标准。在带宽受限的网络中传送高质量视频信号时,效率扮演了重要角色。例如,6?0 x 480象素30fps的彩色传输需要26Mbytes/s的数据速率。必须降低(压缩)速率,使其能够在双绞线或者铜缆中传输。

有两种类型的视频压缩速率:固定比特率(CBR)和可变比特率(VBR)。对于带宽有限的实时通信信道,CBR限制了数据速率,当图像中出现高质量的移动细节时,会降低图像质量,导致显示图像中出现图像块。VBR根据是否出现图像移动来调整速率,这对于视频监视系统存储非常有用。支持VBR的H.26?压缩在安全视频存储方面效率最高。

此外,在压缩方法上,其他视频图像处理技术提高了视频流预处理和后处理的视频质量。由于分辨率的提高,以及压缩技术的进展,对高性能的需求在不断增长,同时还要保持体系结构的灵活性,方便进行快速更新。随着技术的成熟和产量的提高,降低成本将成为人们关注的焦点。图3是使用FPGA和ASSP的典型视频监视系统设置。

系统体系结构选择包括标准单元ASIC、ASSP,以及数字信号处理(DSP)或者介质处理器和FPGA等可编程解决方案。这些方案各具优缺点,最终选择取决于最终设备要求和方案的可行性。考虑到上面介绍的发展趋势,理想的监视体系结构应具有以下特征:高性能、灵活性、易于更新、低开发成本,随着应用的成熟和产量的提高,能够通过移植降低成本。

高性能

性能不仅体现在压缩上,还体现在预处理和后处理功能上。事实上,在很多情况下,这些功能要比压缩算法本身对性能的影响更大。这类功能的例子包括缩放、去隔行、滤波和色彩空间转换等。

对于视频监视,对高性能的要求排除了单处理器体系结构,因为一个器件无法满足性能要求。目前最好的1GHz DSP无法进行H.26? HD解码,而H.26? HD编码要比解码复杂10倍。FPGA是唯一能够解决这一矛盾的可编程方案。在某些情况下,最好的解决方案是结合FPGA和外部DSP处理器。

灵活性支持了产品快速面市,方便了产品更新

当技术快速发展时,体系结构必须足够灵活,能够方便的进行更新。在这些应用中无法使用标准单元ASIC和ASSP。ASSP一般针对大批量消费类市场,产品容易过时,对大部分应用而言,选择ASSP的风险较大。

低开发成本

考虑到掩模、晶片、软件、设计验证和布板等成本,开发一个典型90nm标准单元ASIC的成本会高达3千万美金。只有产量非常大的消费类市场能够解决如此昂贵的开发成本。

嵌入式 DSP Altera FPGA 机顶盒 LCD 编码器 VHDL Verilog C语言 Quartus 滤波器 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)