基于FPGA设计航空电子系统

时间:11-07

来源:互联网

点击:

对 MIL-STD-1553 系统设计采用基于核心的实施

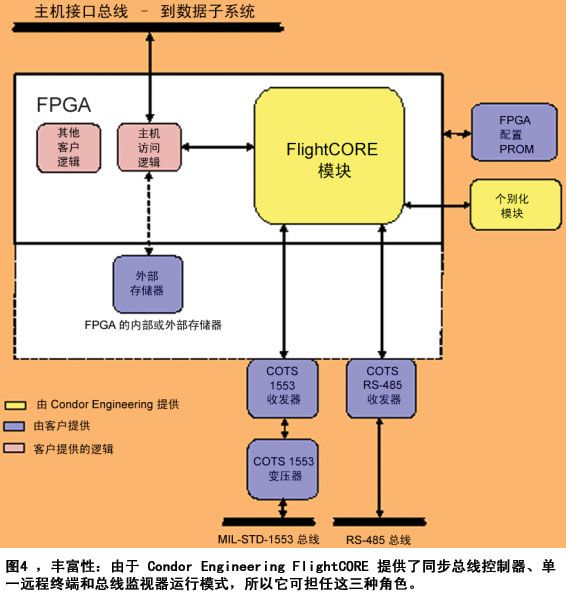

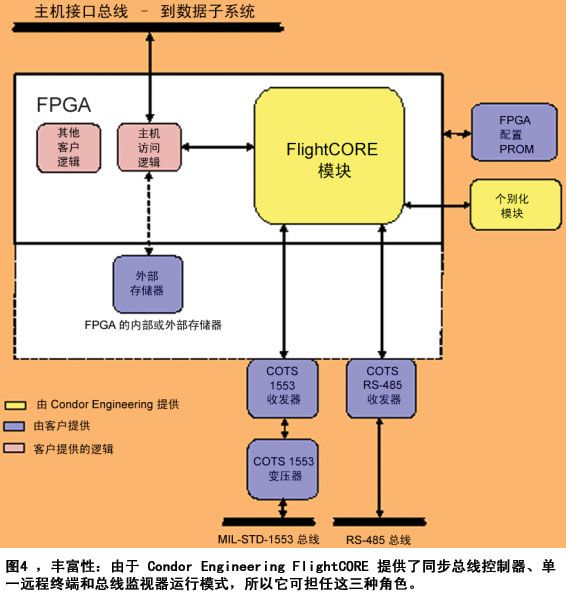

现代 FPGA 的强大功能使其成为 MIL-STD-1553 设计的理想选择,这就是 Condor Engineering 推出 FlightCORE 的原因。FlightCORE 是一种允许设计人员在各种 Altera 和 Xilinx 的 FPGA中轻松实现无版权的实例化设计的 MIL-STD-1553 IP。多数情况下,利用Xilinx 综合技术 (XST) 或 Altera Quartus II 集成综合技术 (QIS),FlightCORE 1553 可以在两天内成功地集成。如图 4 所示,用户只须将 Condor Engineering 的 IP 核心与其自身逻辑和 Condor Engineering 的个别化模块 (3mm x 3mm) 集成,即可实现高性能的 MIL-STD-1553设计。FlightCORE 还允许开发人员选择存储器的大小以恰好地与其系统需求相匹配。图4还显示了可以实施内部存贮和/或外部双端口随机存贮器。该产品还提供了 Manchester II编码与解码、信息协议验证与合法化及为接口控制和编程实施简单的共享存贮架构等所有的必要组件。只需增加外部收发器即可,如标准的COTS MIL-STD-1553或RS-485收发器。

单一芯片上集中多个实例

类似 Condor Engineering 的FlightCORE 这样的 MIL-STD-1553 解决方案需要少量的FPGA资源,约为 3,000个逻辑单元,148k bit的内存和不到 20个引脚(不包括外部主存总线)。较小的体积使在单一芯片上放置多个相互独立的实例成为可能,如图3 所示,某些程序可以在单一FPGA上集中8到10个实例。

结论

FPGA 与其容纳的“知识产权”使设计人员可以对 LRU 进行修改或专门设计,以适应不同的航空电子通信、武器系统和日新月异的升级之间的微小差异。像Condor Engineering的 MIL-STD-1553、1Mb和10Mb的FlightCORE IP 这样的通信核心,提供了一种直接而灵活的方法,可有效地解决日益增长的功能和废弃问题。

现代 FPGA 的强大功能使其成为 MIL-STD-1553 设计的理想选择,这就是 Condor Engineering 推出 FlightCORE 的原因。FlightCORE 是一种允许设计人员在各种 Altera 和 Xilinx 的 FPGA中轻松实现无版权的实例化设计的 MIL-STD-1553 IP。多数情况下,利用Xilinx 综合技术 (XST) 或 Altera Quartus II 集成综合技术 (QIS),FlightCORE 1553 可以在两天内成功地集成。如图 4 所示,用户只须将 Condor Engineering 的 IP 核心与其自身逻辑和 Condor Engineering 的个别化模块 (3mm x 3mm) 集成,即可实现高性能的 MIL-STD-1553设计。FlightCORE 还允许开发人员选择存储器的大小以恰好地与其系统需求相匹配。图4还显示了可以实施内部存贮和/或外部双端口随机存贮器。该产品还提供了 Manchester II编码与解码、信息协议验证与合法化及为接口控制和编程实施简单的共享存贮架构等所有的必要组件。只需增加外部收发器即可,如标准的COTS MIL-STD-1553或RS-485收发器。

单一芯片上集中多个实例

类似 Condor Engineering 的FlightCORE 这样的 MIL-STD-1553 解决方案需要少量的FPGA资源,约为 3,000个逻辑单元,148k bit的内存和不到 20个引脚(不包括外部主存总线)。较小的体积使在单一芯片上放置多个相互独立的实例成为可能,如图3 所示,某些程序可以在单一FPGA上集中8到10个实例。

结论

FPGA 与其容纳的“知识产权”使设计人员可以对 LRU 进行修改或专门设计,以适应不同的航空电子通信、武器系统和日新月异的升级之间的微小差异。像Condor Engineering的 MIL-STD-1553、1Mb和10Mb的FlightCORE IP 这样的通信核心,提供了一种直接而灵活的方法,可有效地解决日益增长的功能和废弃问题。

FPGA 电子 总线 仿真 收发器 变压器 Xilinx 电路 Altera Quartus 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)