成功解决FPGA设计时序问题的三大要点

时间:11-08

来源:互联网

点击:

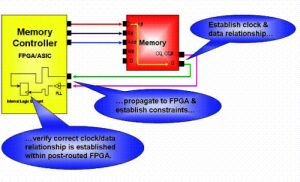

FPGA的设计与高速接口技术可以帮助你满足今天的市场要求,但也提出了一些有趣的设计挑战。为了确保存储器接口的数据传输准确,在超过200兆赫兹以上,进行时序分析将发挥更突出的作用,以识别和解决系统运行的问题。在这些频率内,最重要的是创建和控制时序空余,留下最小的空余,以确保数据采集和演示窗口的准确。更快的边缘速率同时也放大物理设计的影响,造成信号完整性问题,对此则需要更多的沉降时间及缩小时序空余。

FPGA器件现在还包括某些先进的功能,如支持带有I/O单元接口的双通道数据(DDR)和板上锁相环(PLL)网络进行精确时钟控制等等。这些在FPGA技术中的高级功能均提供先进的接口模块,从而有助于减少界面设计,再加上TimingDesigner软件的独特能力,在最短的时序中提供最准确、有力的解决方案。本文主要探讨了DDR型存储器接口设计中必要的时钟偏移及数据采集的时序空余。

DDR/QDR存储器接口的设计问题

DDR或四倍数据速率(QDR)存储设备可以提供和接受两倍于器件时钟频率的源同步数据,这意味着数据在时钟的上升缘和下降缘传输。此外,需要捕捉时钟偏移和进行适当地调整,以确保适当的时钟与数据关系。

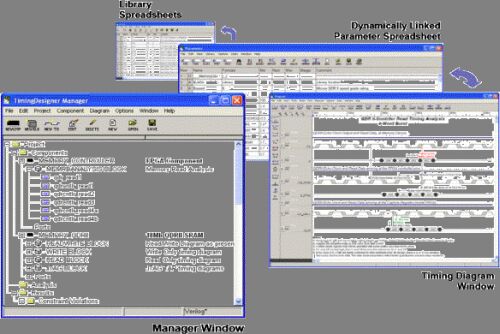

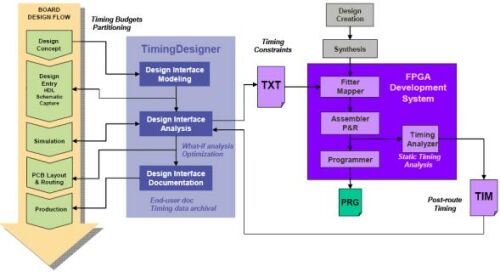

图1:TimingDesigner软件便于捕获设计特点的图形界面窗口。

如前所述,现在一些FPGA装置包括DDR接口的I/O单元和板上的PLL网络。这意味着,你必须有一个方式来控制模块的准确和可靠。为了说明这一点,让我们来读取QDR II SRAM源同步接口的设计要求看看实例。

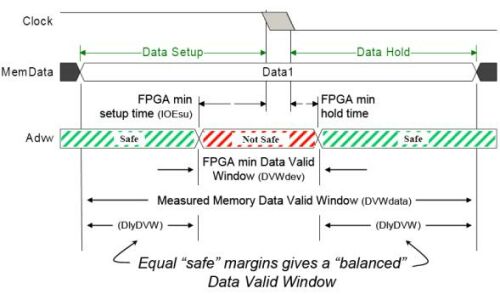

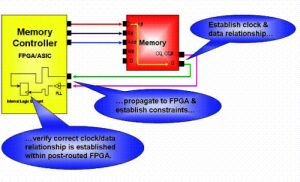

在同步存储器系统例如QDR SRAM中,数据是与时钟同步的,所以存储器数据的相位必须旋转90度。这种相位旋转通常在有效数据窗口中进行时钟中心调整,这是QDR实现准确数据采集的一个重要设计特点(见图2)。如果要改变时钟中心,我们可以通过对板上FPGA的PLL网络进行简单的延时时钟信号来达到。

图2:中心对齐的时钟/数据关系。

获取数据

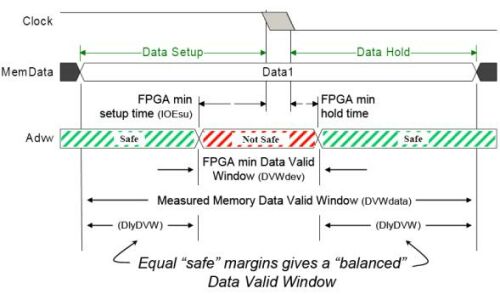

延迟时钟信号可以实现中心对齐以避免各种温度变化和其他类似的设计影响,可能会对时钟或数据方面带来一些影响,但不会很大,但违背了接收存储器的建立或保持时序的要求。在理论上,对于大部分器件,中心对齐的时钟边缘将最大限度地建立和保持时序,留出足够的安全空余。然而,除非建立的需求合适于保持的需求,时钟信号的中心对齐将提供更多的时序空余。

理想的解决办法是为器件的建立和保持提供一个最大的安全空余,可以通过转化平衡空余,为二者都提供相同的安全空余。为了平衡空余,我们为接收器件确定最低的有效数据窗口,在实际有效数据窗口的中心窗内可以给我们的存储器提供设计参数。

利用接收器件最小的建立和保持时间,我们可以利用下面的公式确定最小的"安全"的有效数据窗口:

最小创建时间+最低保持时间=最低有效数据窗口

如图3所示,在存储器器件中可以看出,实际结果是在有效数据窗口中间。为了确保获取数据,总线必须在接收器最小的有效数据窗口外的"安全"区域内进行转换。根据时钟与数据的关系,信号设计在任一区域内,在获取数据时,我们确保尽可能多的安全空余。

图3:平衡实际有效数据窗口中的最小有效数据窗口。

实现适当的时钟偏移

源同步时钟的相位偏移将有效地改变存储控制器接收寄存器的最小有效数据窗口,因此将形成平衡有效数据窗口。时钟偏移调整是FPGA装置中PLL器件的一个组成部分。要确定偏移的值,我们必须考虑到影响信号的布线延迟和任何外部延迟。

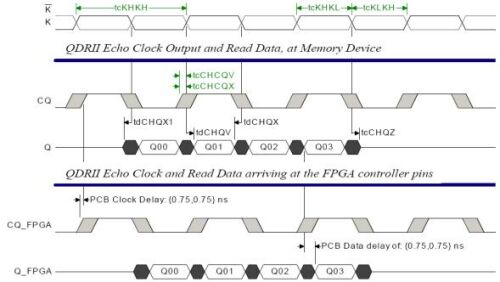

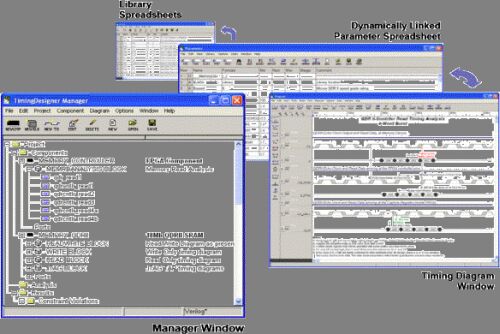

首先,我们使用TimingDesigner软件通过存储器数据表为QDR SRAM创造一个图表(图4)。我们利用此图确定存储器与有效数据窗口中的时钟和数据信号时序的关系。目的是精确定义存储器的信号关系,并在PCB到FPGA的设计中传递这种关系。

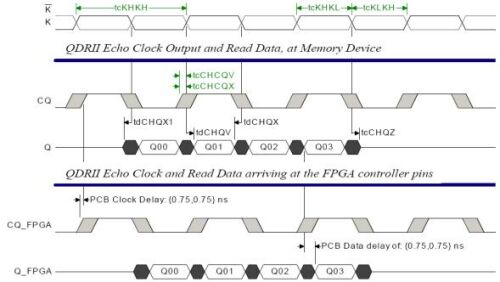

图4:QDR存储器读取时序图MT54W1MH18J

从图4可以看出在FPGA的管脚上,PCB传播延迟与时钟(CQ_FPGA)和数据(Q_FPGA)信号间的关系。在TimingDesigner软件的动态链接参数表中使用单独的变量可以轻松地获得PCB板的延时及延迟值对相关的信号的影响。现在,我们可以在适当的FPGA装置中,为获取时钟而得到内部布线延迟和确定正确的相位偏移。

FPGA设计要素

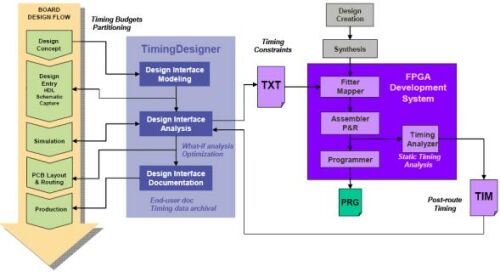

大多数的FPGA利用约束驱动进行布局和布线。时序约束为关键信号提供时序信息。TimingDesigner软件提供独特的时序参考图如测量和计算变量结果,从行内文字到文件都支持厂商特定的约束语法。例如,在一个FPGA约束布线中,对符合其动态文字窗口的语法要求中,可以通过时序图中为特定信号计算延迟误差。然后,我们可以将这些语法通过一个文本文件导入到FPGA的开发系统中,或者我们可以直接将数值复制到FPGA的约束编辑器中。

对于高速存储器接口设计,数据存储器被放置在FPGA装置I/O单元的附近,以尽量减少布线延时的影响。该I/O单元只有一个布线路径为输入数据信号,因此在数据总线的每一部分都存在数据路径延迟。FPGA的PLL也被用来进行适当的时钟控制,并通常有几种可能的从输入焊盘到捕捉寄存器的路径。制造商通过控制特定的属性,使PLL的特点包括相位偏移,相乘,或相除等因素,无论是原始示例的设计代码或约束都可以带入模块。因此,时钟和数据路径的布线和延误必须确定,以实现适当的时钟相位偏移。

图5:TimingDesigner软件为FPGA设计流程提供直观的界面。

在FPGA的最初布局和布线完成后,时序报告提供数据总线中每个时序的详细延时信息。如果有必要,可为FPGA开发系统的关键信号设定延时路径,TimingDesigner软件可以提取相关信息和利用图表更新。在这个设计实例中,我们需要输入数据总线和相关时钟信号的时序报告。

FPGA器件现在还包括某些先进的功能,如支持带有I/O单元接口的双通道数据(DDR)和板上锁相环(PLL)网络进行精确时钟控制等等。这些在FPGA技术中的高级功能均提供先进的接口模块,从而有助于减少界面设计,再加上TimingDesigner软件的独特能力,在最短的时序中提供最准确、有力的解决方案。本文主要探讨了DDR型存储器接口设计中必要的时钟偏移及数据采集的时序空余。

DDR/QDR存储器接口的设计问题

DDR或四倍数据速率(QDR)存储设备可以提供和接受两倍于器件时钟频率的源同步数据,这意味着数据在时钟的上升缘和下降缘传输。此外,需要捕捉时钟偏移和进行适当地调整,以确保适当的时钟与数据关系。

图1:TimingDesigner软件便于捕获设计特点的图形界面窗口。

如前所述,现在一些FPGA装置包括DDR接口的I/O单元和板上的PLL网络。这意味着,你必须有一个方式来控制模块的准确和可靠。为了说明这一点,让我们来读取QDR II SRAM源同步接口的设计要求看看实例。

在同步存储器系统例如QDR SRAM中,数据是与时钟同步的,所以存储器数据的相位必须旋转90度。这种相位旋转通常在有效数据窗口中进行时钟中心调整,这是QDR实现准确数据采集的一个重要设计特点(见图2)。如果要改变时钟中心,我们可以通过对板上FPGA的PLL网络进行简单的延时时钟信号来达到。

图2:中心对齐的时钟/数据关系。

获取数据

延迟时钟信号可以实现中心对齐以避免各种温度变化和其他类似的设计影响,可能会对时钟或数据方面带来一些影响,但不会很大,但违背了接收存储器的建立或保持时序的要求。在理论上,对于大部分器件,中心对齐的时钟边缘将最大限度地建立和保持时序,留出足够的安全空余。然而,除非建立的需求合适于保持的需求,时钟信号的中心对齐将提供更多的时序空余。

理想的解决办法是为器件的建立和保持提供一个最大的安全空余,可以通过转化平衡空余,为二者都提供相同的安全空余。为了平衡空余,我们为接收器件确定最低的有效数据窗口,在实际有效数据窗口的中心窗内可以给我们的存储器提供设计参数。

利用接收器件最小的建立和保持时间,我们可以利用下面的公式确定最小的"安全"的有效数据窗口:

最小创建时间+最低保持时间=最低有效数据窗口

如图3所示,在存储器器件中可以看出,实际结果是在有效数据窗口中间。为了确保获取数据,总线必须在接收器最小的有效数据窗口外的"安全"区域内进行转换。根据时钟与数据的关系,信号设计在任一区域内,在获取数据时,我们确保尽可能多的安全空余。

图3:平衡实际有效数据窗口中的最小有效数据窗口。

实现适当的时钟偏移

源同步时钟的相位偏移将有效地改变存储控制器接收寄存器的最小有效数据窗口,因此将形成平衡有效数据窗口。时钟偏移调整是FPGA装置中PLL器件的一个组成部分。要确定偏移的值,我们必须考虑到影响信号的布线延迟和任何外部延迟。

首先,我们使用TimingDesigner软件通过存储器数据表为QDR SRAM创造一个图表(图4)。我们利用此图确定存储器与有效数据窗口中的时钟和数据信号时序的关系。目的是精确定义存储器的信号关系,并在PCB到FPGA的设计中传递这种关系。

图4:QDR存储器读取时序图MT54W1MH18J

从图4可以看出在FPGA的管脚上,PCB传播延迟与时钟(CQ_FPGA)和数据(Q_FPGA)信号间的关系。在TimingDesigner软件的动态链接参数表中使用单独的变量可以轻松地获得PCB板的延时及延迟值对相关的信号的影响。现在,我们可以在适当的FPGA装置中,为获取时钟而得到内部布线延迟和确定正确的相位偏移。

FPGA设计要素

大多数的FPGA利用约束驱动进行布局和布线。时序约束为关键信号提供时序信息。TimingDesigner软件提供独特的时序参考图如测量和计算变量结果,从行内文字到文件都支持厂商特定的约束语法。例如,在一个FPGA约束布线中,对符合其动态文字窗口的语法要求中,可以通过时序图中为特定信号计算延迟误差。然后,我们可以将这些语法通过一个文本文件导入到FPGA的开发系统中,或者我们可以直接将数值复制到FPGA的约束编辑器中。

对于高速存储器接口设计,数据存储器被放置在FPGA装置I/O单元的附近,以尽量减少布线延时的影响。该I/O单元只有一个布线路径为输入数据信号,因此在数据总线的每一部分都存在数据路径延迟。FPGA的PLL也被用来进行适当的时钟控制,并通常有几种可能的从输入焊盘到捕捉寄存器的路径。制造商通过控制特定的属性,使PLL的特点包括相位偏移,相乘,或相除等因素,无论是原始示例的设计代码或约束都可以带入模块。因此,时钟和数据路径的布线和延误必须确定,以实现适当的时钟相位偏移。

图5:TimingDesigner软件为FPGA设计流程提供直观的界面。

在FPGA的最初布局和布线完成后,时序报告提供数据总线中每个时序的详细延时信息。如果有必要,可为FPGA开发系统的关键信号设定延时路径,TimingDesigner软件可以提取相关信息和利用图表更新。在这个设计实例中,我们需要输入数据总线和相关时钟信号的时序报告。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)