成功解决FPGA设计时序问题的三大要点

时间:11-08

来源:互联网

点击:

1.导入布线后的时序到TimingDesigner软件中

导入FPGA的时序报告信息,我们需要规划最坏的情况从而确定在图表(Q_FPGA)中相关的波形图。信号设计规范定义在同一个时序图表中不能带有同名的波形图。通过规划端口, TimingDesigner软件可以过滤时序报告并提取有用的信息。这些规划被存储在图表文件内并可预先解决的布局和布线问题。

2.提供可视化的捕捉寄存器

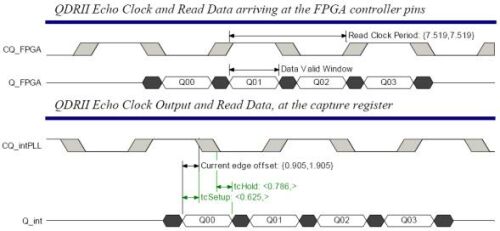

从导入时序报告文件开始, TimingDesigner软件为关键信号延时创建变量,并在电子数据表中规划和分配这些信号端口。变量过去是用来在时序图中更新时钟与数据关系。现在,可确定在FPGA器件内捕捉寄存器中的边缘关系。

内部寄存器建立和保持是从时序报告和相关的约束中提取所需的时序。下一步,在时序图表中添加另外两个信号和偏移时序报告中的布线延时;在捕捉寄存器中添加数据和时钟,然后建立和保持FPGA器件适用的约束。用时钟边缘和有效数据窗口边缘的补偿确定必要的相位偏移,来平衡设计中有效的数据窗口。

3.平衡有效数据窗口

我们可以使用下列公式来确定PLL时钟信号产生的相位偏移:

1、从设计的实际有效数据窗口减少FPGA装置I/O部分的最小有效数据窗口,然后结果除于2,实际结果为这2个有效数据窗口的差额(DlyDVW)。(参考图3)

DlyDVW = (DVWdata - DVWdev) / 2

2、I/O寄存器数据建立时间加上DlyDVW值,就确定了相对时钟边缘的有效数据窗口(DlyRelSU)。

DlyRelSU = DlyDVW + IOEsu

3、最后,从相对建立时间(上面第2步得到的数值),减去时钟信号与捕捉寄存器的有效数据窗口(从时序图测量)之间的补偿。

Clk_offset = DlyRelSU - EdgeOffset

利用上述公式,我们可以确定FPGA开发系统中PLL的相位偏移量,并执行到下一步的布局和布线。

4.验证结果

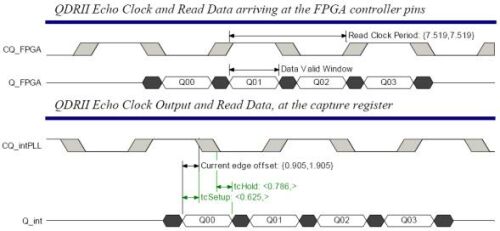

再次导入做过以上修改的布线后时序文件,TimingDesigner软件会自动更新需要的数值,并更正及重新定位I/O单元的时钟信号CQ_intPLL。如图6所示。依靠改变PLL,确切的平衡建立和保持空余将是不可能的。对于这些情况下,应该在FPGA装置的PLL中获取平衡增量以解决这个问题。

图6:在改变时钟和平衡建立及保持空余后,获取数据分析的时序图表。

本文小结

高速设计往往有严格的规范和严谨的发布时间表,所以需要一个交互式的时序规划和分析工具,来获得快速和完整的时序空余,以分析并解决可能影响到最终设计成功的因素。本文说明了如何利用TimingDesigner软件对FPGA设计流程进行准确地捕捉和交换时序信息,以帮助在整个设计过程中管理时序空余,并提供可视化的界面验证设计,并预测设计性能。今天的FPGA器件产品都带有多功能的时钟配置和丰富的I/O资源,并且带有高数据传输能力,TimingDesigner软件为高速存储器如DDR & QDR SRAM提供精确的关键路径时序分析功能。

导入FPGA的时序报告信息,我们需要规划最坏的情况从而确定在图表(Q_FPGA)中相关的波形图。信号设计规范定义在同一个时序图表中不能带有同名的波形图。通过规划端口, TimingDesigner软件可以过滤时序报告并提取有用的信息。这些规划被存储在图表文件内并可预先解决的布局和布线问题。

2.提供可视化的捕捉寄存器

从导入时序报告文件开始, TimingDesigner软件为关键信号延时创建变量,并在电子数据表中规划和分配这些信号端口。变量过去是用来在时序图中更新时钟与数据关系。现在,可确定在FPGA器件内捕捉寄存器中的边缘关系。

内部寄存器建立和保持是从时序报告和相关的约束中提取所需的时序。下一步,在时序图表中添加另外两个信号和偏移时序报告中的布线延时;在捕捉寄存器中添加数据和时钟,然后建立和保持FPGA器件适用的约束。用时钟边缘和有效数据窗口边缘的补偿确定必要的相位偏移,来平衡设计中有效的数据窗口。

3.平衡有效数据窗口

我们可以使用下列公式来确定PLL时钟信号产生的相位偏移:

1、从设计的实际有效数据窗口减少FPGA装置I/O部分的最小有效数据窗口,然后结果除于2,实际结果为这2个有效数据窗口的差额(DlyDVW)。(参考图3)

DlyDVW = (DVWdata - DVWdev) / 2

2、I/O寄存器数据建立时间加上DlyDVW值,就确定了相对时钟边缘的有效数据窗口(DlyRelSU)。

DlyRelSU = DlyDVW + IOEsu

3、最后,从相对建立时间(上面第2步得到的数值),减去时钟信号与捕捉寄存器的有效数据窗口(从时序图测量)之间的补偿。

Clk_offset = DlyRelSU - EdgeOffset

利用上述公式,我们可以确定FPGA开发系统中PLL的相位偏移量,并执行到下一步的布局和布线。

4.验证结果

再次导入做过以上修改的布线后时序文件,TimingDesigner软件会自动更新需要的数值,并更正及重新定位I/O单元的时钟信号CQ_intPLL。如图6所示。依靠改变PLL,确切的平衡建立和保持空余将是不可能的。对于这些情况下,应该在FPGA装置的PLL中获取平衡增量以解决这个问题。

图6:在改变时钟和平衡建立及保持空余后,获取数据分析的时序图表。

本文小结

高速设计往往有严格的规范和严谨的发布时间表,所以需要一个交互式的时序规划和分析工具,来获得快速和完整的时序空余,以分析并解决可能影响到最终设计成功的因素。本文说明了如何利用TimingDesigner软件对FPGA设计流程进行准确地捕捉和交换时序信息,以帮助在整个设计过程中管理时序空余,并提供可视化的界面验证设计,并预测设计性能。今天的FPGA器件产品都带有多功能的时钟配置和丰富的I/O资源,并且带有高数据传输能力,TimingDesigner软件为高速存储器如DDR & QDR SRAM提供精确的关键路径时序分析功能。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)