FPGA中SPI复用配置的编程方法

时间:10-13

来源:互联网

点击:

SPI(Serial Peripheral Interface,串行外围设备接口)是一种高速、全双工、同步的通信总线,在芯片的引脚上只占用4根线,不仅节约了芯片的引脚,同时在PCB的布局上还节省空间。正是出于这种简单、易用的特性,现在越来越多的芯片集成了这种通信协议。

1 SPI配置介绍

1.1 Spantan-3E SPI配置流程

SPI方式是通过符合SPI接口时序的第三方SPI Flash对FPGA进行加载。它适合作为FPGA硬件结构的bit文件保存介质,如果应用软件工程编译后的代码较小,保存在同一片SPI FLash中(即复用SPI Flash)无疑是可行的最廉价方案。

由于本没计软件工程规模较小,所以利用此复用SPI Flash方式对FPGA进行配置,既保存FPGA配置的bit文件,也保存应用软件工程的bit文件。系统在上电或向PROG_B引脚发出低脉冲后,FPGA芯片经过一个初始化序列清空内部FPGA配置存储器。此序列开始时,DONE和INIT_B引脚均转为低。初始化完成后,INIT_B引脚转为高,并采样芯片的配置模式及变量选择引脚。

SPI模式下,FPGA对变量选择(VS[2:0])引脚采样,以确定发出哪个SPI命令序列。当初始化之后发出INIT_B信号时,模式引脚和变量选择引脚都必须处在正确的逻辑级,以确保正确采样。

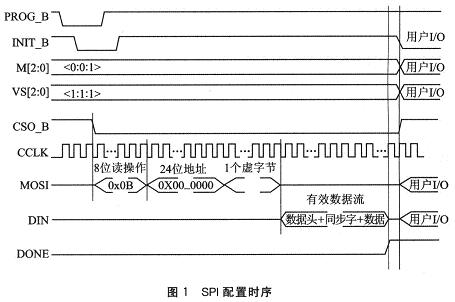

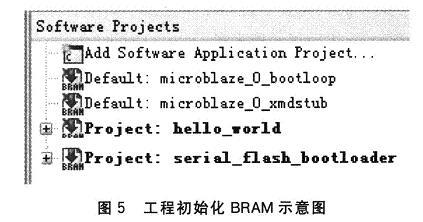

在变量选择引脚选择SPI命令集之后,FPGA将CSO_B选择信号置为低,并且开始通过FPGA的CCLK引脚对SPI Flash存储器进行时钟控制。接着发出8位读命令后跟24位起始地址0x000000和目标命令集的适量虚拟字节。FPGA从地址0开始读取SPI Flash存储器阵列,直到读完所需的配置位数。如果从存储器件读取到有效比特流,则发DONE信号,以指示FPGA配置成功。图1为SPI配置方式的时序。

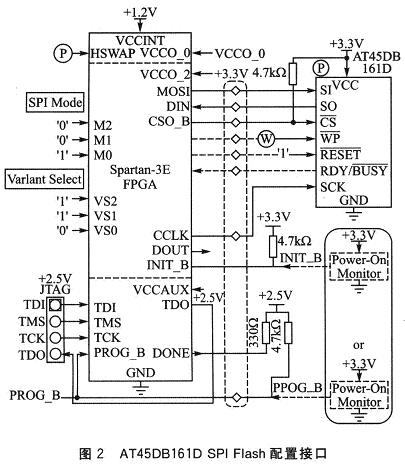

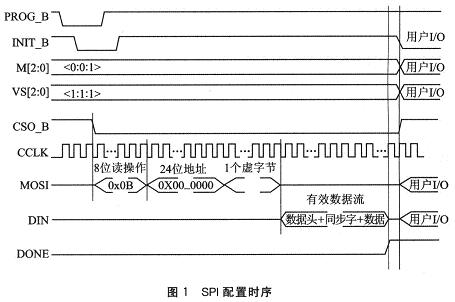

图2是AT45DB161D SPI Flash的配置接口。这种配置方式只占用了FPGA芯片的4个引脚,而且配置成功之后,所有SPI引脚都成为可用的用户I/O引脚,这就节省了FPGA的引脚资源。

1.2 SPI Flash存储器的复用

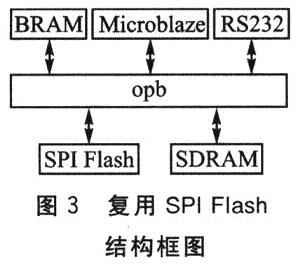

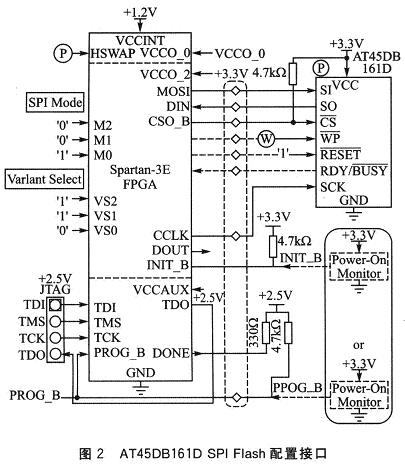

复用SPI Flash是指既用它来保存硬件配置文件、Bootloader引导程序还用来保存用户应用程序。在加载阶段,FPGA自动从SPI Flash中读取硬件配置bit文件及Bootloader程序进行配置到片内BRAM中运行。当完成加载后,FPGA内部逻辑启动,通过运行的Bootloader程序读取SPI Flash中的用户应用程序,并写到外部SDRAM的相应位置,最后Bootloader程序切换指令指针到SDRAM指定位置,在外部的SDRAM中开始执行应用程序。

图3给出了本系统中复用SPI Flash嵌入式系统结构图,用EDK中的opb_sdram连接外部SDRAM,用opb_spi连接SPI Flash(AT45DB161D),通过Bootloader软件程序实现从SPI Flash中复制用户应用程序到SDRAM中,然后在SDRAM中运行。但是,Boot-loader在系统上电时会通过FP-GA芯片的配置引脚首先加载到BRAM中运行,这样就可以实现上电自动加载启动程序。

2 Bootloader引导程序的设计

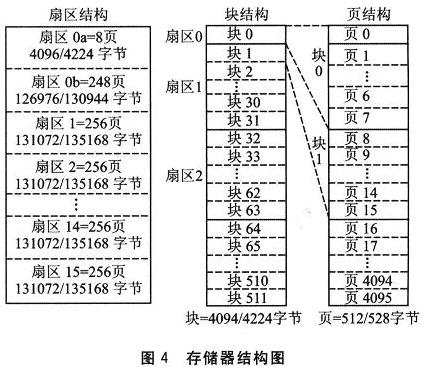

在工程代码编写之前要求对硬件器件有所了解,主要需要了解FPGA所需要的配置文件空间,还有Flash存储结构。例如:XC3S500E配置文件空间为2 270 208位,所以要根据它计算存储应用程序的基地址。AT45DB161D是串行接口的闪存芯片,它包含有17 301 504位,被组织为4 096页,每页512/528字节。除了主存储器,AT45DB161D还包括2个SRAM数据缓冲区,每个缓冲区512/528字节。在主存储器正在编程时,缓冲区是允许接收数据的,并且支持数据流式写入。(此处为528字节/页)

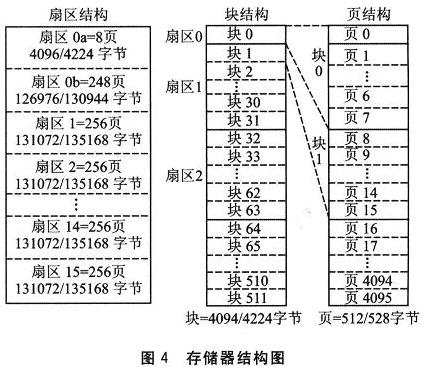

AT45DB161D的存储器阵列分为3个级别的粒度,分别为扇区、块与页。图4对各个级别进行了分析,详细说明了每个扇区与块的页数。所有的编程操作都是针对页的。擦除操作可以作用于芯片、扇区、块或页。

最后利用定义的空函数int(*boot_app_jump) (void);”将地址指针指向内存的应用程序基地址,使其从此处开始运行程序。

//将目的地址赋给跳转函数

boot_app_jump=(int(*)(void))DESTINATION_AD-DR;

//运行跳转函数,使其在该函数地址开始运行程序boot_app_jump();

3 SPI Flash软件引导过程及SPI Flash编程

本实验使用简单的应用程序(打印hello_world),即工程“hello_world”。工程serial_Flash_bootloader就是上面设计的引导程序。

3.1 编译用户应用程序的二进制文件

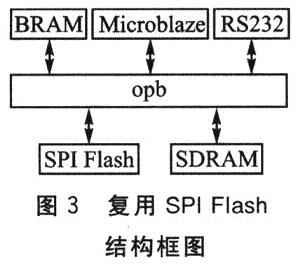

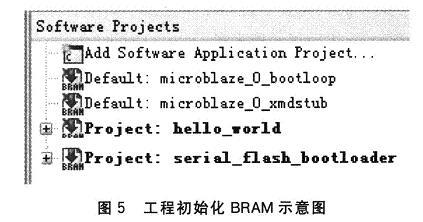

由于应用程序要在外部SDRAM中运行,所以不需要初始化BRAM存储器,如图5所示。

为了指明程序的开始地址和应用程序的可执行文件的产生路径,需要在编译选项中设置。右键“应用程序工程”,Set Compiler Options在Output ELF file中选择可执行文件的产生路径,如XC3S500E\hello_world\hello_world.elf,在Program Start Address中键入程序执行的起始地址(这里是SDRAM的基地址:0x90000000)。接下来编译应用程序工程,编译完成后就会在XC3S500E\hello_world文件夹中产生hello_world.elf。为了后面对SPI Flash编程的需要,应将elf转变成二进制形式的文件。这就需要利用cygwin shell窗口命令来完成,这个脚本提供了一个简单的命令实现这个目的。利用mb-objcopy-O binary<options><ELF file input><bi-nary file to output>命令就可以将elf转变成二进制形式的文件(.b文件)。

例如:mb-objcopy-O binary ./hello world/helloworld.elf./hello_world/hello_world.b用来在工程目录下hello_world文件夹创建工程的一个hello_world.b的二进制文件。生成的文件hello_world.b大约2 KB左右。

1 SPI配置介绍

1.1 Spantan-3E SPI配置流程

SPI方式是通过符合SPI接口时序的第三方SPI Flash对FPGA进行加载。它适合作为FPGA硬件结构的bit文件保存介质,如果应用软件工程编译后的代码较小,保存在同一片SPI FLash中(即复用SPI Flash)无疑是可行的最廉价方案。

由于本没计软件工程规模较小,所以利用此复用SPI Flash方式对FPGA进行配置,既保存FPGA配置的bit文件,也保存应用软件工程的bit文件。系统在上电或向PROG_B引脚发出低脉冲后,FPGA芯片经过一个初始化序列清空内部FPGA配置存储器。此序列开始时,DONE和INIT_B引脚均转为低。初始化完成后,INIT_B引脚转为高,并采样芯片的配置模式及变量选择引脚。

SPI模式下,FPGA对变量选择(VS[2:0])引脚采样,以确定发出哪个SPI命令序列。当初始化之后发出INIT_B信号时,模式引脚和变量选择引脚都必须处在正确的逻辑级,以确保正确采样。

在变量选择引脚选择SPI命令集之后,FPGA将CSO_B选择信号置为低,并且开始通过FPGA的CCLK引脚对SPI Flash存储器进行时钟控制。接着发出8位读命令后跟24位起始地址0x000000和目标命令集的适量虚拟字节。FPGA从地址0开始读取SPI Flash存储器阵列,直到读完所需的配置位数。如果从存储器件读取到有效比特流,则发DONE信号,以指示FPGA配置成功。图1为SPI配置方式的时序。

图2是AT45DB161D SPI Flash的配置接口。这种配置方式只占用了FPGA芯片的4个引脚,而且配置成功之后,所有SPI引脚都成为可用的用户I/O引脚,这就节省了FPGA的引脚资源。

1.2 SPI Flash存储器的复用

复用SPI Flash是指既用它来保存硬件配置文件、Bootloader引导程序还用来保存用户应用程序。在加载阶段,FPGA自动从SPI Flash中读取硬件配置bit文件及Bootloader程序进行配置到片内BRAM中运行。当完成加载后,FPGA内部逻辑启动,通过运行的Bootloader程序读取SPI Flash中的用户应用程序,并写到外部SDRAM的相应位置,最后Bootloader程序切换指令指针到SDRAM指定位置,在外部的SDRAM中开始执行应用程序。

图3给出了本系统中复用SPI Flash嵌入式系统结构图,用EDK中的opb_sdram连接外部SDRAM,用opb_spi连接SPI Flash(AT45DB161D),通过Bootloader软件程序实现从SPI Flash中复制用户应用程序到SDRAM中,然后在SDRAM中运行。但是,Boot-loader在系统上电时会通过FP-GA芯片的配置引脚首先加载到BRAM中运行,这样就可以实现上电自动加载启动程序。

2 Bootloader引导程序的设计

在工程代码编写之前要求对硬件器件有所了解,主要需要了解FPGA所需要的配置文件空间,还有Flash存储结构。例如:XC3S500E配置文件空间为2 270 208位,所以要根据它计算存储应用程序的基地址。AT45DB161D是串行接口的闪存芯片,它包含有17 301 504位,被组织为4 096页,每页512/528字节。除了主存储器,AT45DB161D还包括2个SRAM数据缓冲区,每个缓冲区512/528字节。在主存储器正在编程时,缓冲区是允许接收数据的,并且支持数据流式写入。(此处为528字节/页)

AT45DB161D的存储器阵列分为3个级别的粒度,分别为扇区、块与页。图4对各个级别进行了分析,详细说明了每个扇区与块的页数。所有的编程操作都是针对页的。擦除操作可以作用于芯片、扇区、块或页。

最后利用定义的空函数int(*boot_app_jump) (void);”将地址指针指向内存的应用程序基地址,使其从此处开始运行程序。

//将目的地址赋给跳转函数

boot_app_jump=(int(*)(void))DESTINATION_AD-DR;

//运行跳转函数,使其在该函数地址开始运行程序boot_app_jump();

3 SPI Flash软件引导过程及SPI Flash编程

本实验使用简单的应用程序(打印hello_world),即工程“hello_world”。工程serial_Flash_bootloader就是上面设计的引导程序。

3.1 编译用户应用程序的二进制文件

由于应用程序要在外部SDRAM中运行,所以不需要初始化BRAM存储器,如图5所示。

为了指明程序的开始地址和应用程序的可执行文件的产生路径,需要在编译选项中设置。右键“应用程序工程”,Set Compiler Options在Output ELF file中选择可执行文件的产生路径,如XC3S500E\hello_world\hello_world.elf,在Program Start Address中键入程序执行的起始地址(这里是SDRAM的基地址:0x90000000)。接下来编译应用程序工程,编译完成后就会在XC3S500E\hello_world文件夹中产生hello_world.elf。为了后面对SPI Flash编程的需要,应将elf转变成二进制形式的文件。这就需要利用cygwin shell窗口命令来完成,这个脚本提供了一个简单的命令实现这个目的。利用mb-objcopy-O binary<options><ELF file input><bi-nary file to output>命令就可以将elf转变成二进制形式的文件(.b文件)。

例如:mb-objcopy-O binary ./hello world/helloworld.elf./hello_world/hello_world.b用来在工程目录下hello_world文件夹创建工程的一个hello_world.b的二进制文件。生成的文件hello_world.b大约2 KB左右。

总线 PCB FPGA 嵌入式 Xilinx 电路 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA 重复配置和测试的实现(08-14)

- 经I/O优化的FPGA(04-23)

- 基于Actel FPGA的PWM IP的应用(09-17)