克服FPGA I/O引脚分配挑战

步骤4: 为最终核签(Sign-Off)运行DRC和WASSO

一旦完成引脚分配,就可利用 PinAhead丰富的DRC规则来进行核签前的DRC检查,保证在运行PlanAhead软件实施工具前设计是无错的。 工具中的众多I/O和时钟相关规则可保证I/O布局是合法的。 可利用PlanAhead的DRC对话框来选择相应的规则。

如果工具发现违反规则的情况,将会显示带有错误信息的DRC结果表。 选择相应的错误信息可以更进一步入地了解有关情况。

PlanAhead还提供了加权平均同步转换输出(WASSO)分析功能,可帮助识别引脚分配引起的潜在信号完整性问题。 为工具提供PCB设计的寄生参数特性,PlanAhead软件将会分析不同的I/O组以及其近邻,并报告每一I/O组的利用情况和状态。

步骤5: 导出I/O引脚分配数据

你可以将I/O端口列表和封装引脚信息从PlanAhead软件导出为CSV格式文件、HDL头或UCF文件。 CSV文件包括有关器件封装引脚的所有信息,以及与设计相关的I/O引脚分配和配置。 列表中的封装引脚部分是数据表中定义I/O端口的很好起点。

你还可以利用该数据表自动生成设计小组开始PCB布局所需要的PCB原理图符号。 然而,有时这些符号对于原理图来说太长了,可能需要将它们缩短为几个符号。 利用PinAhead中的创建的接口组可以快速做到这一点。

以原理图符号形式提供这些I/O引脚配置为PCB设计人员开始PCB布局提供了很好的基础。 因为如果在引脚分配的最初就考虑到PCB接口,那么最很可能与最终的引脚配置比较接近。

如果确实需要改变引脚来方便布线,那么改变也比较容易,因为需要改变的引脚可能已经在I/O组内了。 这种方法不会对FPGA设计造成太大的影响。 通过在PCB和FPGA设计人员之间传递修改过的引脚布局数据表或UCF文件,可以保证两个部分之间的任何修改是同步的。

为防止信号噪声以及支持某些FPGA功能,你还可能希望将未用的引脚或特定配置的引脚连接到VCC或GND。 赛灵思目前正在致力于在PinAhead的下一版本中提供这一功能。

通过一个界面方便FPGA设计人员指导此类引脚,并在输出的CSV数据表中包含相应的引脚连接。 这样PCB设计人员就可以更容易识别相关引脚并正确连接之。

未来,随着FPGA集成更复杂的功能以及使用更先进的封装,发展可靠的FPGA和PCB引脚布局方法势在必行。 PinAhead Lite在帮助实现基于协同设计理念的引脚布局策略方面已经能够提供很大帮助,但我们仍然已经在致力于改进这一工具以帮助设计人员更好地应对引脚布局方面的挑战。

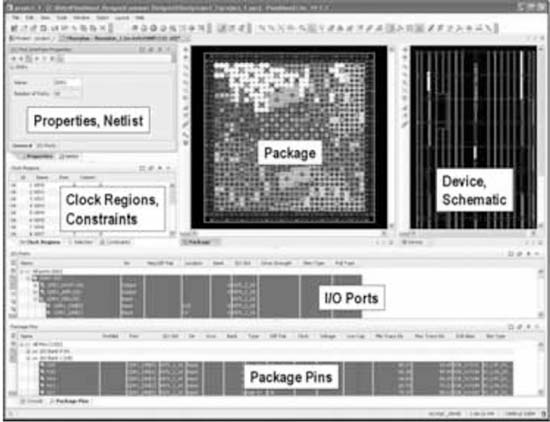

图 2 PinAhead 环境

PCB FPGA Xilinx 赛灵思 连接器 总线 电压 收发器 DSP EDA 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 验证FPGA设计:模拟,仿真,还是碰运气?(08-04)

- FPGA 上同步开关噪声的分析(04-05)

- 我的FPGA学习历程(05-23)

- 在FPGA中实现源同步LVDS接收正确字对齐(05-01)