基于CPLD技术的数字时序控制电路设计

时间:10-08

来源:互联网

点击:

5、系统仿真和验证

软件设计完成后,通过Quartus II软件指定芯片为EPM570T100C5,并根据电路原理图进行引脚分配,设定CPLD的引脚功能,然后启动编译程序来编译项目。编译器将进行错误检查、网表提取、逻辑综合和器件适配,然后进行行为仿真、功能仿真和时序仿真,最后用下载电缆通过JTAG编程方式将文件下载到芯片中,从而生成硬件电路。

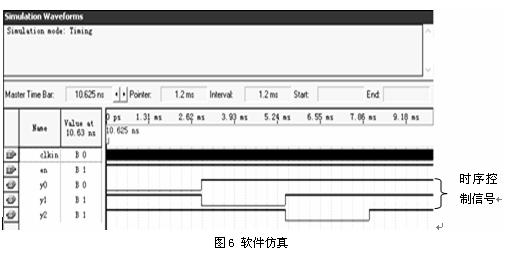

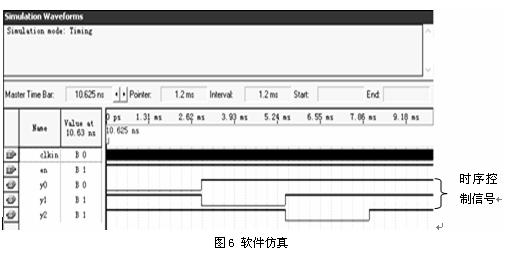

图6为系统软件仿真的结果,从图中可以发现,生成的时序控制信号状态稳定,精度为纳秒级。

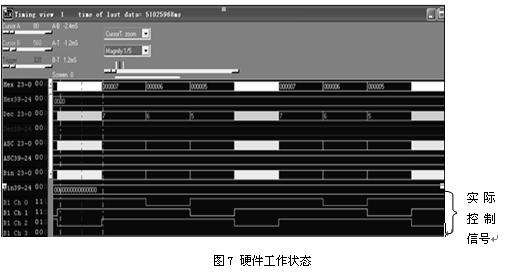

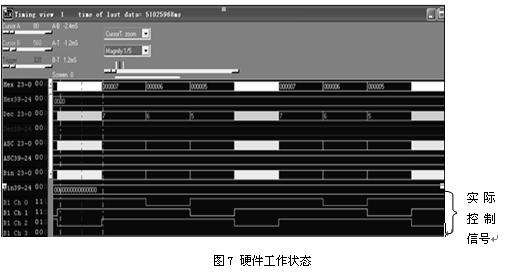

图7为将程序下载到目标芯片,硬件工作时通过逻辑分析仪观察到的系统实际工作状态图,可以发现系统实际工作状态与理论设计思想相一致。图中的三路时序控制信号精度较高、状态稳定,无毛刺和漂移现象,为提高系统的稳定性和接收矩阵的精度奠定了基础。

软件设计完成后,通过Quartus II软件指定芯片为EPM570T100C5,并根据电路原理图进行引脚分配,设定CPLD的引脚功能,然后启动编译程序来编译项目。编译器将进行错误检查、网表提取、逻辑综合和器件适配,然后进行行为仿真、功能仿真和时序仿真,最后用下载电缆通过JTAG编程方式将文件下载到芯片中,从而生成硬件电路。

图6为系统软件仿真的结果,从图中可以发现,生成的时序控制信号状态稳定,精度为纳秒级。

图7为将程序下载到目标芯片,硬件工作时通过逻辑分析仪观察到的系统实际工作状态图,可以发现系统实际工作状态与理论设计思想相一致。图中的三路时序控制信号精度较高、状态稳定,无毛刺和漂移现象,为提高系统的稳定性和接收矩阵的精度奠定了基础。

电路 CPLD 信号发生器 电容 振荡器 Altera Quartus EDA VHDL 仿真 相关文章:

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA按键模式的研究与设计(03-24)

- 周立功:如何兼顾学习ARM与FPGA(05-23)