USB OTG的IP Core设计与FPGA验证

时间:10-09

来源:互联网

点击:

4 USB OTG IP核的特性讨论

4.1 连接状态的检测

当上电复位后进入空闲状态,开始USB会话。首先需要等待一段时间(最多50 ms),OTG控制器会检测输入ID线的电平,以确定自己是A设备还是B设备,高电平表示B设备,低电平表示A设备。对于A设备,IP核会等待电源线Vbus上的电平上升到符合USB会话的4.4 V最低电平要求,具体的操作就是通过UTMI+接口的DrvVbus信号控制PHY对Vbus电源线充电,以提供USB总线工作用的电源;对于B设备,则根据是否正在作SRP请求而实现SRP协议或者进入数据传输。当Vbus电源线上的电平满足要求时,A设备等待B设备连入USB总线。作为主机的A设备的DpPulldown和Dm—Pulldown在开始会话后始终保持高电平状态,如果B设备没有连上,则2条USB数据线DP和DM呈现SE0状态;而当B设备连上USB总线时,DP和DM会呈现J态或者K态。根据这一特点,A设备就可以判断出是否有B设备连入USB总线。

4.2 SRP协议的实现

当设备进入SRP协议实现时,B设备等待SRP操作的初始条件,即通过UTMI+接口的DischrgVbus信号加速SRP条件的满足。当初始条件都满足后,B设备通过UTMI+接口的信号XcvrSelect、TermSelect、DpPulldown和DmPulldown实现对PHY的控制,使之向DP线上发出驱动脉冲。持续5~10 ms后,B设备又通过UTMI+接口的信号ChrgVbus控制PHY向Vbus上发出驱动脉冲,该驱动脉冲需要持续足够长的时间以使Vbus电源线被充电到2.1 V。驱动完成后,回到空闲状态,进而等待A设备对SRP作出响应。如果A设备识别到了B设备的SRP,则会开始USB会话,否则本次SRP失败。

4.3 HNP协议的实现

不妨假设A设备当前处于主机状态,而B设备处于从设备状态。此时,B设备需要通过HNP取得USB主机地位,过程如下:A设备通过发出挂起命令使得USB总线准备进入挂起状态。B设备首先由数据传输状态准备进入挂起状态。这时,B设备需要检查是否有HNP请求,如果有则开始等待A设备连接,否则正常地进入挂起状态。B设备在等待A设备配置时,A设备尚未完全进入挂起状态,当它进入挂起状态的同时会检查是否有B设备的断开中断。如果有,则说明B设备正在进行HNP操作,并且已经进入了等待A设备配置状态,接着A设备进入设备工作状态,从而使自己变为从设备。B设备检测到A设备的连接后,对USB总线进行复位,同时开始对A设备进行复位操作。B设备进入主机模式工作,而A设备则进入从设备模式工作。在B设备作为主机完成了对USB总线的使用后,再一次通过HNP将USB主机地位还给A设备,操作过程类似。

5 系统功能仿真

本设计采用硬件描述语言Verilog HDL完成RTL(寄存器传输级)的描述。寄存器传输级是指在数字系统设计时,可以将数字系统简单地看作是寄存器和寄存器之间的组合逻辑(cornbinational logic)。本设计使用Mentor公司的设计仿真软件ModelSimSE进行功能仿真。应用Verilog HDL语言搭建测试平台,通过仿真工具,设计者对各设计层次的设计模块进行仿真,以确定这些设计模块的功能和逻辑关系是否满足设计要求。

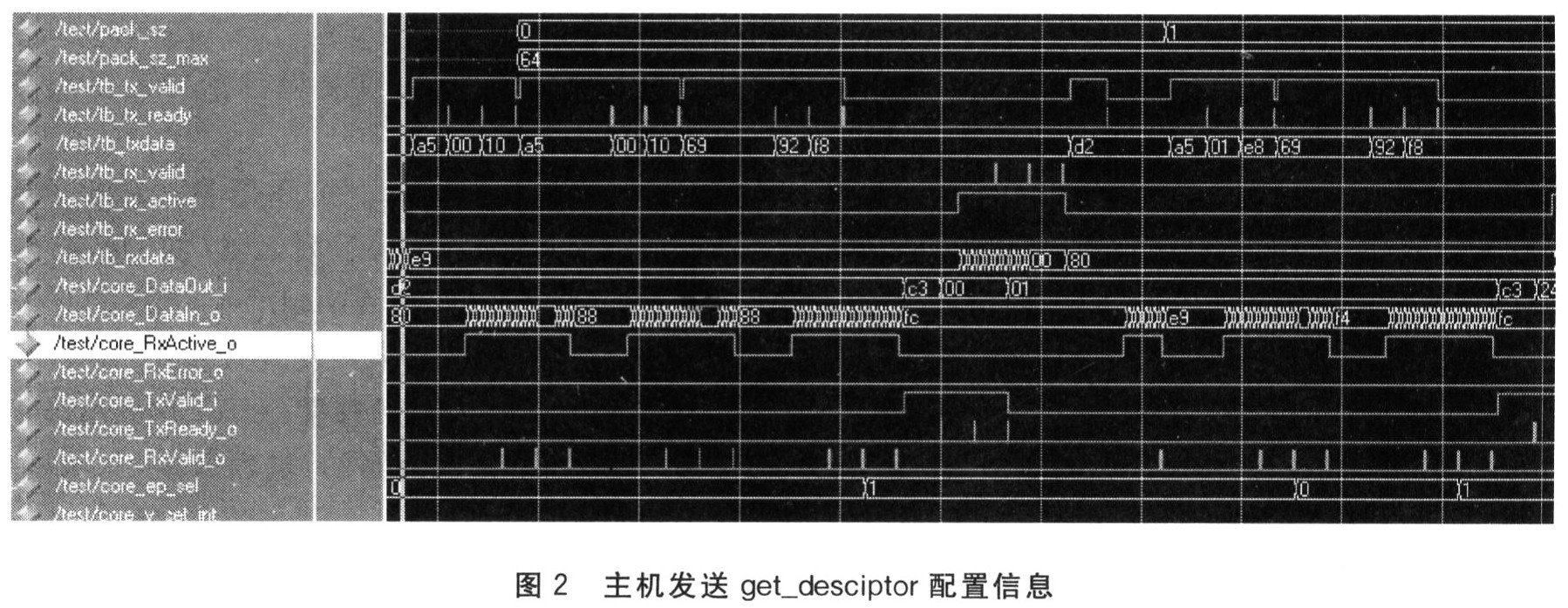

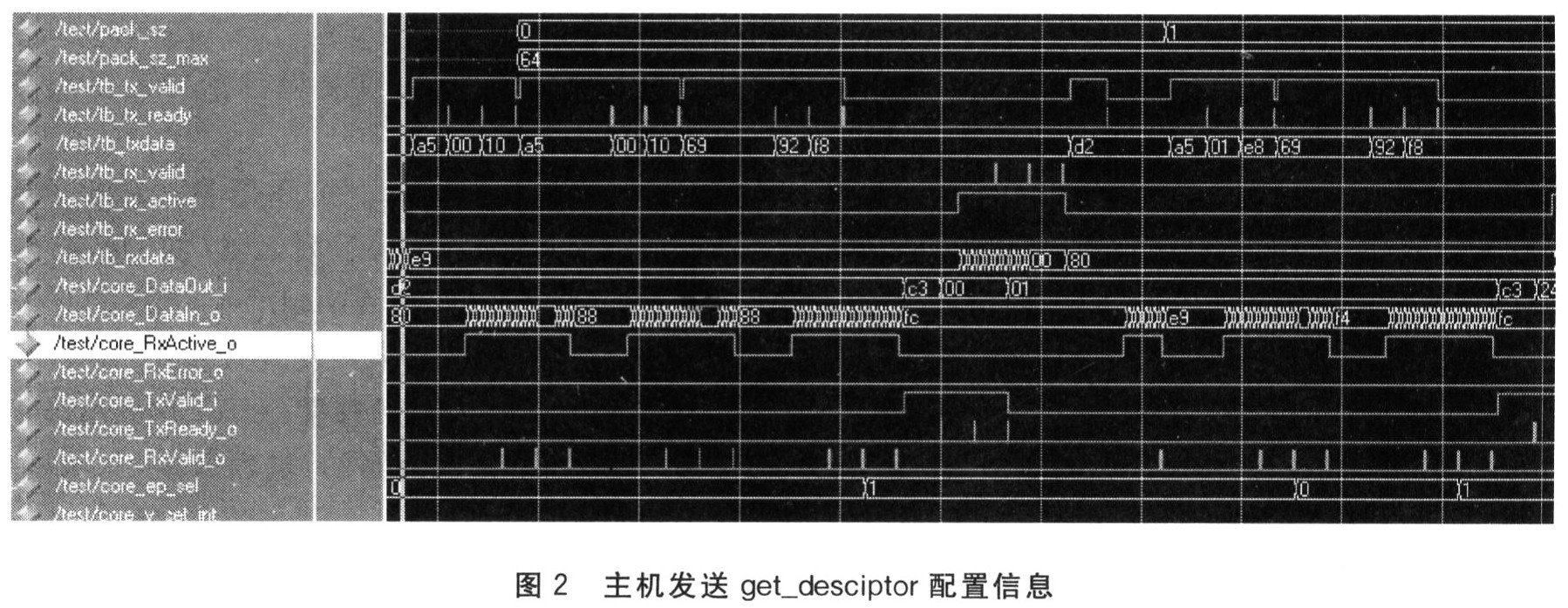

在设计的验证阶段,将包含该设计的2个USB OTG IP核直连,并让这2个IP核工作在不同的工作状态,即一个工作在A设备模式,另一个工作在B设备模式。这样,A设备就可以作为B设备的激励源,通过A设备发出一系列测试信号,比如向B设备发出复位信号以及SRP和HNP协议请求,发送SOF标志信号和配置信息等。然后观察B设备是否对这些命令或者信号做出正确的响应。通过这样的程序来验证该IP核是否具有双功能和对USB协议的支持情况。仿真的部分结果如图2所示。

6 FPGA验证

FPGA是一种可编程逻辑器件,可进行多次编程操作,使器件根据不同的需求实现不同的功能。随着微电子技术的发展,FPGA的性能不断提高,很多设计已经完全可以由FPGA来完成。目前,在ASIC设计中一个重要的验证手段就是通过FPGA进行硬件仿真,以保证设计的可靠性。FPGA芯片是整个验证系统的核心,它包含了USB OTG IP核和相关的控制模块。因为用Verilog语言来实现控制模块的功能,所以将它和USB OTG IP核一起综合然后下载到FPGA中进行测试。

FPGA选用AItera公司的Cyclone系列芯片,具体型号是EPlCl2Q240C8;物理层模拟部分选用Philips公司的产品ISPl301;存储器SRAM选用ISSI公司的IS63LVl024—12J。复位电路用来产生上电复位信号,也可以在系统正常工作时,通过按键开关产生复位信号。此复位信号提供给USB IP核作为系统复位。系统的布局布线采用的是Altera公司的QHartusII 6.0。

验证过程分成2个部分来分别验证主机模式和设备模式。当USB 0TG IP核工作在主机模式时,直接用U盘与IP核进行连接,通过编写的底层驱动可以识别出U盘。在完成对U盘的驱动后,成功地进行了数据传输,最后正确地断开连接。当IP核工作在设备模式时,IP核作为USB从设备接入电脑主机的USB接口。通过安装新的驱动,电脑主机可以识别出该USB设备,完成对该设备的驱动后,同样可以正确地进行数据传输,并安全地移除该设备。验证的结果表明,该USB 0TG IP核的主机和从设备功能均能正常工作,达到了预期的设计要求。

4.1 连接状态的检测

当上电复位后进入空闲状态,开始USB会话。首先需要等待一段时间(最多50 ms),OTG控制器会检测输入ID线的电平,以确定自己是A设备还是B设备,高电平表示B设备,低电平表示A设备。对于A设备,IP核会等待电源线Vbus上的电平上升到符合USB会话的4.4 V最低电平要求,具体的操作就是通过UTMI+接口的DrvVbus信号控制PHY对Vbus电源线充电,以提供USB总线工作用的电源;对于B设备,则根据是否正在作SRP请求而实现SRP协议或者进入数据传输。当Vbus电源线上的电平满足要求时,A设备等待B设备连入USB总线。作为主机的A设备的DpPulldown和Dm—Pulldown在开始会话后始终保持高电平状态,如果B设备没有连上,则2条USB数据线DP和DM呈现SE0状态;而当B设备连上USB总线时,DP和DM会呈现J态或者K态。根据这一特点,A设备就可以判断出是否有B设备连入USB总线。

4.2 SRP协议的实现

当设备进入SRP协议实现时,B设备等待SRP操作的初始条件,即通过UTMI+接口的DischrgVbus信号加速SRP条件的满足。当初始条件都满足后,B设备通过UTMI+接口的信号XcvrSelect、TermSelect、DpPulldown和DmPulldown实现对PHY的控制,使之向DP线上发出驱动脉冲。持续5~10 ms后,B设备又通过UTMI+接口的信号ChrgVbus控制PHY向Vbus上发出驱动脉冲,该驱动脉冲需要持续足够长的时间以使Vbus电源线被充电到2.1 V。驱动完成后,回到空闲状态,进而等待A设备对SRP作出响应。如果A设备识别到了B设备的SRP,则会开始USB会话,否则本次SRP失败。

4.3 HNP协议的实现

不妨假设A设备当前处于主机状态,而B设备处于从设备状态。此时,B设备需要通过HNP取得USB主机地位,过程如下:A设备通过发出挂起命令使得USB总线准备进入挂起状态。B设备首先由数据传输状态准备进入挂起状态。这时,B设备需要检查是否有HNP请求,如果有则开始等待A设备连接,否则正常地进入挂起状态。B设备在等待A设备配置时,A设备尚未完全进入挂起状态,当它进入挂起状态的同时会检查是否有B设备的断开中断。如果有,则说明B设备正在进行HNP操作,并且已经进入了等待A设备配置状态,接着A设备进入设备工作状态,从而使自己变为从设备。B设备检测到A设备的连接后,对USB总线进行复位,同时开始对A设备进行复位操作。B设备进入主机模式工作,而A设备则进入从设备模式工作。在B设备作为主机完成了对USB总线的使用后,再一次通过HNP将USB主机地位还给A设备,操作过程类似。

5 系统功能仿真

本设计采用硬件描述语言Verilog HDL完成RTL(寄存器传输级)的描述。寄存器传输级是指在数字系统设计时,可以将数字系统简单地看作是寄存器和寄存器之间的组合逻辑(cornbinational logic)。本设计使用Mentor公司的设计仿真软件ModelSimSE进行功能仿真。应用Verilog HDL语言搭建测试平台,通过仿真工具,设计者对各设计层次的设计模块进行仿真,以确定这些设计模块的功能和逻辑关系是否满足设计要求。

在设计的验证阶段,将包含该设计的2个USB OTG IP核直连,并让这2个IP核工作在不同的工作状态,即一个工作在A设备模式,另一个工作在B设备模式。这样,A设备就可以作为B设备的激励源,通过A设备发出一系列测试信号,比如向B设备发出复位信号以及SRP和HNP协议请求,发送SOF标志信号和配置信息等。然后观察B设备是否对这些命令或者信号做出正确的响应。通过这样的程序来验证该IP核是否具有双功能和对USB协议的支持情况。仿真的部分结果如图2所示。

6 FPGA验证

FPGA是一种可编程逻辑器件,可进行多次编程操作,使器件根据不同的需求实现不同的功能。随着微电子技术的发展,FPGA的性能不断提高,很多设计已经完全可以由FPGA来完成。目前,在ASIC设计中一个重要的验证手段就是通过FPGA进行硬件仿真,以保证设计的可靠性。FPGA芯片是整个验证系统的核心,它包含了USB OTG IP核和相关的控制模块。因为用Verilog语言来实现控制模块的功能,所以将它和USB OTG IP核一起综合然后下载到FPGA中进行测试。

FPGA选用AItera公司的Cyclone系列芯片,具体型号是EPlCl2Q240C8;物理层模拟部分选用Philips公司的产品ISPl301;存储器SRAM选用ISSI公司的IS63LVl024—12J。复位电路用来产生上电复位信号,也可以在系统正常工作时,通过按键开关产生复位信号。此复位信号提供给USB IP核作为系统复位。系统的布局布线采用的是Altera公司的QHartusII 6.0。

验证过程分成2个部分来分别验证主机模式和设备模式。当USB 0TG IP核工作在主机模式时,直接用U盘与IP核进行连接,通过编写的底层驱动可以识别出U盘。在完成对U盘的驱动后,成功地进行了数据传输,最后正确地断开连接。当IP核工作在设备模式时,IP核作为USB从设备接入电脑主机的USB接口。通过安装新的驱动,电脑主机可以识别出该USB设备,完成对该设备的驱动后,同样可以正确地进行数据传输,并安全地移除该设备。验证的结果表明,该USB 0TG IP核的主机和从设备功能均能正常工作,达到了预期的设计要求。

USB 总线 嵌入式 SoC 电源管理 电流 电路 收发器 模拟前端 仿真 Verilog Mentor ModelSim FPGA 电子 Altera 相关文章:

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- 我的FPGA学习历程(05-23)

- Virtex-5推动超宽带通信和测距的发展(01-06)

- Altera FPGA下载配置(11-11)

- 基于ARM9和CPLD的输入输出系统设计(04-09)

- 基于FPGA的高速图像采集系统设计(03-30)